關于data保存時間的時序錯誤

使用 zynq 器件, select io 解碼串行數據, data 和 clock 直接進入, 未....

Uart協議及Verilog代碼

如果使用Xlinx的片子,建議使用全局時鐘資源(IBUFG后面連接BUFG的方法是最基本的全局時鐘資....

幾種IO口模擬UART的方案

好了,今天為大家帶來幾種IO口模擬串口"硬核"操作,相信大家對類似于串口這樣的電平類通信會有新的認識....

Xilinx生成的讀寫函數

在一個項目中,當你使用microblaze作為控制器來進行系統調度的時候,一般是建議將所有模塊封裝成....

ESP8266的兩種工作模式下的數據傳輸

ESP8266支持3種模式:Station模式、AP模式和Station+AP混合模式。關于這三種模....

探討一下JTAG口是什么?

根據查閱資料及本人的一些實踐經驗所得,在使用JTAG下載接口的過程中,請不要隨意帶電插拔,否則會損壞....

編寫的一個協議相關代碼,位域的值解析

每個域有一個域名,允許在程序中按域名進行操作。這樣就可以把幾個不同的對象用一個字節的二進制位域來表示....

Zookeeper使用注意事項

ZAB (Zookeeper Atomic Broadcast 原子廣播協議) 協議是為分布式協調服....

CS和IP從哪里開始執行代碼

來到我所在的工作車間,提取指令的小A、分析指令的小胖和負責結果回寫的老K都已經到了,就差執行指令的我....

寄存器通電后CPU是怎樣開始工作的

每次一通電,咱們的電路就會啟動自檢工作,把所有的寄存器全部重置,如果哪里有異常的話,就會把錯誤記錄到....

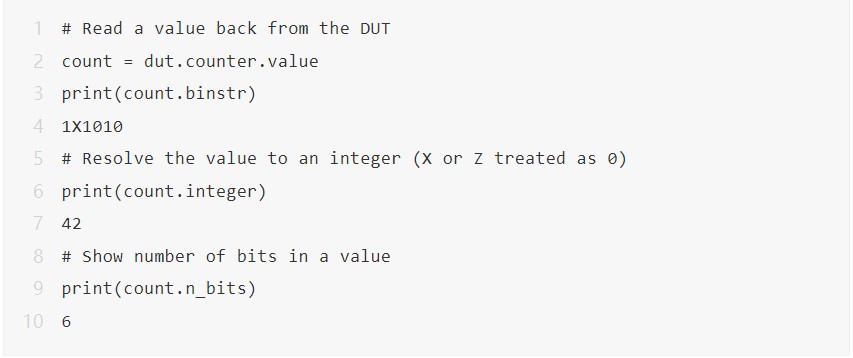

Pynq是不是用Python編程FPGA的新物種?

因此可通過結合最新的HLS優化(例如用于脈動陣列的PolySA和用于模板的SODA與數據流體系結構)....

SERDES的引腳數量和通道優勢

SERDES最明顯的優勢是具備更少的引腳數量和線纜/通道數量。對于早期的SERDES,這意味著數據可....

如何進行FFT IP配置和設計

以Xilinx Vivado設計套件中提供的FFT IP為例,簡要說明如何進行FFT IP配置和設計....

Vivado中快速傅里葉變換IP配置及應用

快速傅里葉變換 (Fast Fourier Transform,FFT), 即利用計算機計算離散傅里....

Sobel算子原理介紹與實現方法

索貝爾算子(Sobel operator)主要用作邊緣檢測,在技術上,它是一離散性差分算子,用來運算....

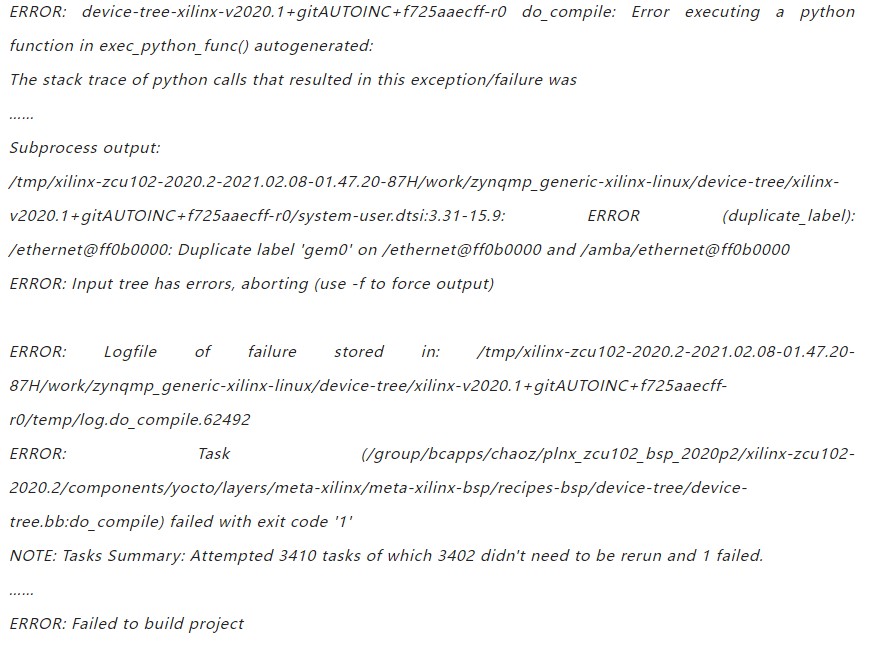

如何在 Petalinux 下定位 decice-tree 錯誤

? 今天邀請到賽靈思專家和大家分享下如何在?Petalinux?下定位?decice-tree?錯誤....

AXI_GPIO簡介與使用指南

前面簡單學習了關于GPIO的操作,本次將使用PL 端調用 AXI GPIO IP 核, 并通過 AX....

使用ModelSim軟件進行時序仿真

通過該圖,我們可以看出,這個工程是我們之前做功能仿真的工程,當我們關閉 ModelSim之后,我們再....