圖像是用各種觀測系統以不同形式和手段觀測客觀世界而獲得的,可以直接或間接作用于人眼進而產生視知覺的實體。

隨著電子技術和計算機技術的飛速發展,數字圖像技術近年來得到極大的重視和長足的發展,并在科學研究、工業生產、醫療衛生、通信等方面得到廣泛的應用。

視頻信號由一系列連續的圖像組成。對視頻信號的處理已經成為數字圖像處理領域中重要的一部分。例如機器人模式識別的過程就是一個視頻信號處理的過程,電視制導導彈識別目標就是充分利用視頻信號處理技術不斷判斷目標是否和預先設定目標圖像一致。本篇將講解如何用 FPGA 技術實現基本的視頻信號處理。本篇的例子可以作為各位大俠進行視頻信號處理時的一個參考,也可以在這個基礎上根據需要進行擴展。

第三篇內容摘要:本篇會介紹程序測試與運行,包括測試程序、測試結果以及總結等相關內容。

五、程序測試與運行

由于整個 FPGA 程序包括 3 部分:處于 TOP 的主體程序,控制其他各個部分程序的運行;視頻圖像數據采集程序,從 SAA7113 獲得數字圖像數據并保存到 SRAM 中;SRAM 讀寫程序實現對 SRAM 的數據讀寫。測試程序需要仿真數據的全部流程。

5.1 測試程序

測試程序代碼如下:

`include "timescale.v"moduletst_saa7113(error,dsprst,xreset,saareset,ARDY,ED_O,ED_OEN_O,SRAM_1_EA,SRAM_2_EA,SRAM_1_O_ED,SRAM_2_O_ED); //內部寄存器 reg reset; reg clk;//50MHz 時鐘 reg llck;//SAA7113 的時鐘 reg [7:0] vpo;//來自 saa7113 的圖像數據 reg capture;//采集數據標志 reg toggle;//總線切換標志 reg [1:0] rst; //輸入 input error; input dsprst,xreset,saareset; input ARDY; input [7:0] ED_O; input ED_OEN_O; input [18:0] SRAM_1_EA; input [7:0] SRAM_1_O_ED; input [18:0] SRAM_2_EA; input [7:0] SRAM_2_O_ED; //來自 dsp 的信號 reg CE3_; reg ARE_; reg AWE_; reg [21:2] EA; reg [7:0] ED_I; //TO SRAM reg [7:0] SRAM_1_IN_ED; reg [7:0] SRAM_2_IN_ED; //wires //from saa7113 wire SRAM_CE_; wire SRAM_OE_; wire SRAM_WE_; wire [18:0] la; wire [7:0] ld; //FROM DSP wire CE_SRAM; wire WE_SRAM; wire OE_SRAM; wire [7:0] ED_SRAM; wire [18:0] EA_SRAM; //連接各個子程序 LWBSAA7113 L_SAA7113 ( .reset(reset), .clk(clk), .llck(llck), .vpo(vpo), .rst(rst), .capture(capture), .error(error), .SRAM_CE_(SRAM_CE_), .SRAM_OE_(SRAM_OE_), .SRAM_WE_(SRAM_WE_), .la(la), .ld(ld) ); LWBDECODE L_DECODE ( .reset(reset), .CE3_(CE3_), .ARE_(ARE_), .AWE_(AWE_), .EA(EA), .ED_I(ED_I), .ED_O(ED_O), .ED_OEN_O(ED_OEN_O), .ARDY(ARDY), .EA_SRAM(EA_SRAM), .ED_SRAM(ED_SRAM), .CE_SRAM(CE_SRAM), .WE_SRAM(WE_SRAM), .OE_SRAM(OE_SRAM), .dsprst(dsprst), .xreset(xreset), .saareset(saareset) ); LWBBUSCHANGE L_BUSCHANGE ( .EA_SRAM(EA_SRAM), .ED_SRAM(ED_SRAM), .CE_SRAM(CE_SRAM), .WE_SRAM(WE_SRAM), .OE_SRAM(OE_SRAM), .la(la), .ld(ld), .SRAM_CE_(SRAM_CE_), .SRAM_WE_(SRAM_WE_), .SRAM_OE_(SRAM_OE_), .SRAM_1_IN_ED(SRAM_1_IN_ED), .SRAM_2_IN_ED(SRAM_2_IN_ED), .toggle(toggle), .SRAM_1_EA(SRAM_1_EA), .SRAM_1_O_ED(SRAM_1_O_ED), .SRAM_2_EA(SRAM_2_EA), .SRAM_2_O_ED(SRAM_2_O_ED) ); //產生時鐘信號 always #10 clk=~clk; always #20 llck = ~llck; initial begin $display(" status : %t TestBench of saa7113 started! ",$time); //initial value clk = 0; #7; llck =0; //reset reset = 1; //dsp 初始化 ARE_ = 1; AWE_ = 1; CE3_ = 1; //初始化 capture = 0; toggle = 1; #2; reset = 0; repeat(20) @(posedge clk); reset = 1'b1; // negate reset //dsp 讀取數據內容 SRAM_1_IN_ED = 8'h1d; SRAM_2_IN_ED = 8'h2d; //dsp 地址總線 EA[21:16] = 6'b000000; EA[15:7] = 9'b000000000; EA[6:2]= 5'b00001; #5; CE3_ = 0; ARE_ = 0; //saa7113 輸出內容 capture = 1; #5; @(posedge llck) vpo = 8'haa; @(posedge llck) vpo = 8'hbb; @(posedge llck) vpo = 8'hcc; @(posedge llck) vpo = 8'hdd; @(posedge llck) vpo = 8'hee; //場同步信號 //1 @(posedge llck) vpo = 8'hff;//begin @(posedge llck) vpo = 8'h00; @(posedge llck) vpo = 8'h00; @(posedge llck) vpo = 8'b00100000;//sav //2 @(posedge llck) vpo = 8'hff;//begin @(posedge llck) vpo = 8'h00; @(posedge llck) vpo = 8'h00; @(posedge llck) vpo = 8'b00100000; //數據開始 @(posedge llck) vpo = 8'hff;//begin @(posedge llck) vpo = 8'h00; @(posedge llck) vpo = 8'h00; @(posedge llck) vpo = 8'b00000000; //data @(posedge llck) vpo = 8'h01;//Cb @(posedge llck) vpo = 8'h02;//Yb @(posedge llck) vpo = 8'h03;//Cr @(posedge llck) vpo = 8'h04;//Yr--1 @(posedge llck) vpo = 8'h05;//Cb @(posedge llck) vpo = 8'h06;//Yb @(posedge llck) vpo = 8'h07;//Cr @(posedge llck) vpo = 8'h08;//Yr--2 @(posedge llck) vpo = 8'h09;//Cb @(posedge llck) vpo = 8'h0a;//Yb @(posedge llck) vpo = 8'h0b;//Cr @(posedge llck) vpo = 8'h0c;//Yr--3 @(posedge llck) vpo = 8'h0d;//Cb @(posedge llck) vpo = 8'h0e;//Yb @(posedge llck) vpo = 8'h0f;//Cr @(posedge llck) vpo = 8'h10;//Yr--4 @(posedge llck) vpo = 8'h11;//Cb @(posedge llck) vpo = 8'h12;//Yb @(posedge llck) vpo = 8'h13;//Cr @(posedge llck) vpo = 8'h14;//Yr--5 @(posedge llck) vpo = 8'h15;//Cb @(posedge llck) vpo = 8'h16;//Yb @(posedge llck) vpo = 8'h17;//Cr @(posedge llck) vpo = 8'h18;//Yr--6 @(posedge llck) vpo = 8'h19;//Cb @(posedge llck) vpo = 8'h1a;//Yb @(posedge llck) vpo = 8'h1b;//Cr @(posedge llck) vpo = 8'h1c;//Yr--7 @(posedge llck) vpo = 8'h1d;//Cb @(posedge llck) vpo = 8'h1e;//Yb @(posedge llck) vpo = 8'h1f;//Cr @(posedge llck) vpo = 8'h20;//Yr--8 @(posedge llck) vpo = 8'h21;//Cb @(posedge llck) vpo = 8'h22;//Yb @(posedge llck) vpo = 8'h23;//Cr @(posedge llck) vpo = 8'h24;//Yr--9 @(posedge llck) vpo = 8'h25;//Cb @(posedge llck) vpo = 8'h26;//Yb @(posedge llck) vpo = 8'h27;//Cr @(posedge llck) vpo = 8'h28;//Yr--10 @(posedge llck) vpo = 8'h29;//Cb @(posedge llck) vpo = 8'h3a;//Yb @(posedge llck) vpo = 8'h3b;//Cr @(posedge llck) vpo = 8'h3c;//Yr--11 //數據結束 @(posedge llck) vpo = 8'hff;//ff @(posedge llck) vpo = 8'h00;//00 @(posedge llck) vpo = 8'h00;//00 @(posedge llck) vpo = 8'b01110000;//end of field 1 #20; ARE_ = 1; capture = 0; #200; //開始切換 toggle = 0; #100; ARE_ = 0; //開始采集數據 capture = 1; //vertical blanking stage //1 @(posedge llck) vpo = 8'hff;//begin @(posedge llck) vpo = 8'h00; @(posedge llck) vpo = 8'h00; @(posedge llck) vpo = 8'b00100000;//sav //2 @(posedge llck) vpo = 8'hff;//begin @(posedge llck) vpo = 8'h00; @(posedge llck) vpo = 8'h00; @(posedge llck) vpo = 8'b00100000; //data start @(posedge llck) vpo = 8'hff;//begin @(posedge llck) vpo = 8'h00; @(posedge llck) vpo = 8'h00; @(posedge llck) vpo = 8'b00000000; //data @(posedge llck) vpo = 8'h01;//Cb @(posedge llck) vpo = 8'h02;//Yb @(posedge llck) vpo = 8'h03;//Cr @(posedge llck) vpo = 8'h04;//Yr--1 @(posedge llck) vpo = 8'h05;//Cb @(posedge llck) vpo = 8'h06;//Yb @(posedge llck) vpo = 8'h07;//Cr @(posedge llck) vpo = 8'h08;//Yr--2 @(posedge llck) vpo = 8'h09;//Cb @(posedge llck) vpo = 8'h0a;//Yb @(posedge llck) vpo = 8'h0b;//Cr @(posedge llck) vpo = 8'h0c;//Yr--3 @(posedge llck) vpo = 8'h0d;//Cb @(posedge llck) vpo = 8'h0e;//Yb @(posedge llck) vpo = 8'h0f;//Cr @(posedge llck) vpo = 8'h10;//Yr--4 @(posedge llck) vpo = 8'h11;//Cb @(posedge llck) vpo = 8'h12;//Yb @(posedge llck) vpo = 8'h13;//Cr @(posedge llck) vpo = 8'h14;//Yr--5 @(posedge llck) vpo = 8'h15;//Cb @(posedge llck) vpo = 8'h16;//Yb @(posedge llck) vpo = 8'h17;//Cr @(posedge llck) vpo = 8'h18;//Yr--6 @(posedge llck) vpo = 8'h19;//Cb @(posedge llck) vpo = 8'h1a;//Yb @(posedge llck) vpo = 8'h1b;//Cr @(posedge llck) vpo = 8'h1c;//Yr--7 @(posedge llck) vpo = 8'h1d;//Cb @(posedge llck) vpo = 8'h1e;//Yb @(posedge llck) vpo = 8'h1f;//Cr @(posedge llck) vpo = 8'h20;//Yr--8 @(posedge llck) vpo = 8'h21;//Cb @(posedge llck) vpo = 8'h22;//Yb @(posedge llck) vpo = 8'h23;//Cr @(posedge llck) vpo = 8'h24;//Yr--9 @(posedge llck) vpo = 8'h25;//Cb @(posedge llck) vpo = 8'h26;//Yb @(posedge llck) vpo = 8'h27;//Cr @(posedge llck) vpo = 8'h28;//Yr--10 @(posedge llck) vpo = 8'h29;//Cb @(posedge llck) vpo = 8'h3a;//Yb @(posedge llck) vpo = 8'h3b;//Cr @(posedge llck) vpo = 8'h3c;//Yr--11 //數據結束 @(posedge llck) vpo = 8'hff;//ff @(posedge llck) vpo = 8'h00;//00 @(posedge llck) vpo = 8'h00;//00 @(posedge llck) vpo = 8'b01110000;//end of field 1 #20; //結束數據采集 capture = 0; #200; //測試程序結束 $finish; endendmodule

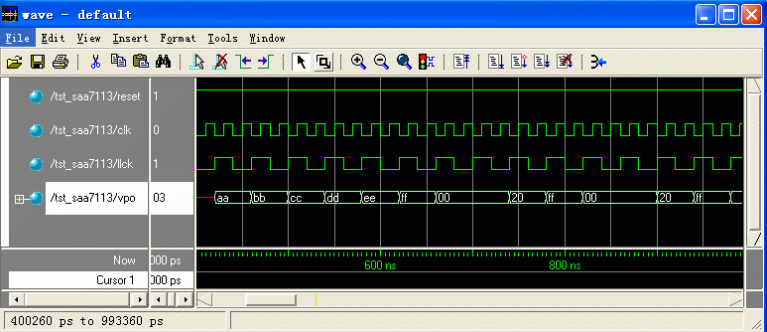

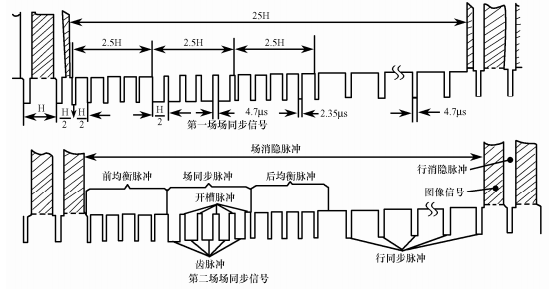

5.2 測試結果 仿真程序產生的視頻圖像數據如圖 18 所示。開始的“aa bb cc dd ee ff”是無效數據,“ff 00 20”表示場同步信號。

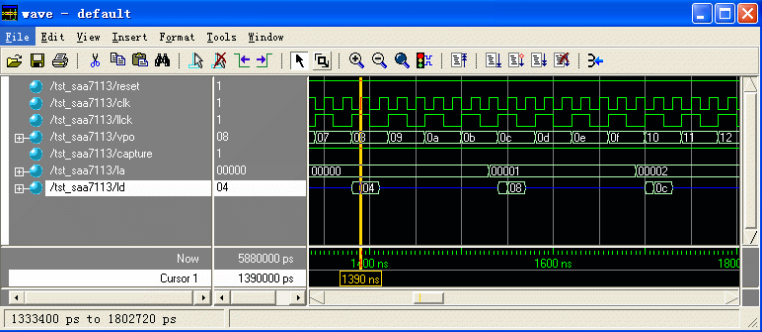

圖 18 仿真產生的視頻圖像數據 經過 FPGA 處理后獲得有效圖像數據并產生相應的地址信號,如圖 19 所示。由于只進行灰度運算,只取亮度信息,因此獲得數據為“04 08 0c”,同時產生地址信號“00 01 02”。

圖 19 FPGA 采集得到的有效圖像數據并產生的地址信號

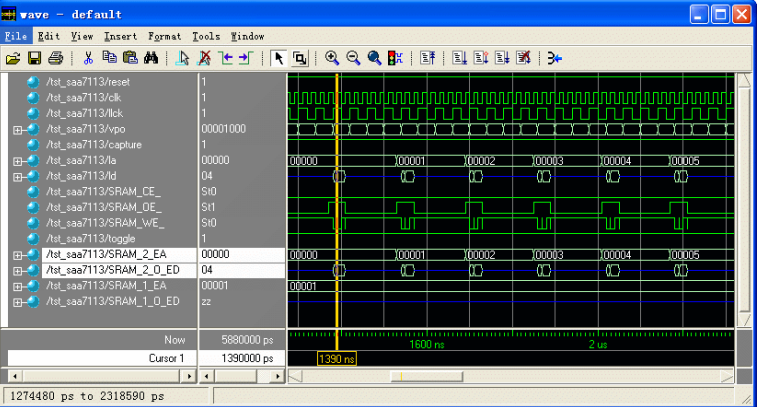

對 SRAM 的讀寫控制,如圖 20 所示。

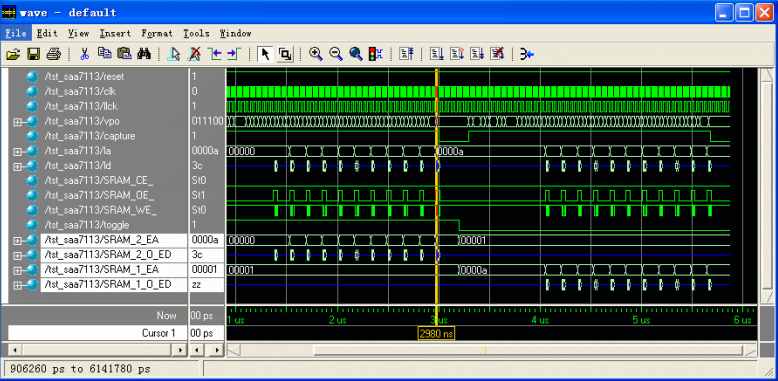

圖 20 產生的對 SRAM 的讀寫控制 兩塊 SRAM 之間的切換,如圖 21 所示。

圖 21 兩塊 SRAM 之間的切換 仿真結果表明整個視頻信號處理程序完成了預先設定的設計目標。

七、總結

本篇首先介紹了視頻信號的基本原理、組成等,然后講解了進行視頻信號處理的基本過程和框架。接下來結合實例講解用 FPGA 及其他芯片組成視頻處理的電路設計和 FPGA 的程序實現。最后用 Modelsim 仿真和測試了程序。本篇為各位大俠提供了一種視頻信號處理的設計方案,僅供參考。

-

FPGA

+關注

關注

1643文章

21957瀏覽量

614046 -

程序

+關注

關注

117文章

3823瀏覽量

82403 -

視頻信號處理

+關注

關注

0文章

2瀏覽量

5017

發布評論請先 登錄

FPGA應用視頻信號處理的基本過程是怎樣的

如何去實現一種CCD視頻信號處理電路的設計?

基于PCI總線的塔康視頻信號產生電路設計

基于XRD4460的CCD視頻信號處理電路的設計

CCD視頻信號處理電路

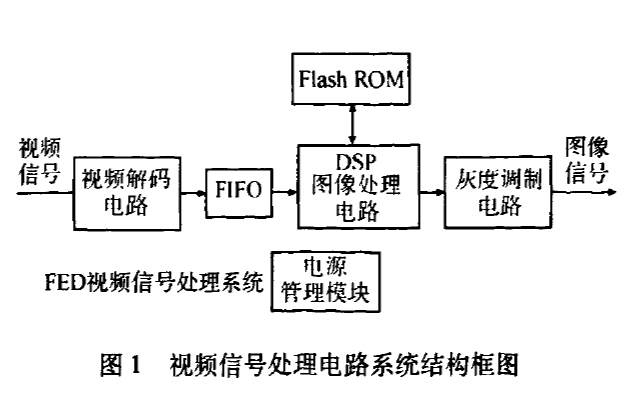

一種基于DSP與FPGA實現場發射平板顯示器視頻信號處理系統的方案

自適應視頻信號傳輸解決方案

基于FPGA的實時視頻信號處理平臺的設計

如何使用DSP和FPGA實現場發射平板顯示器視頻信號處理系統的方案說明

一種視頻信號處理的設計方案

一種視頻信號處理的設計方案

評論