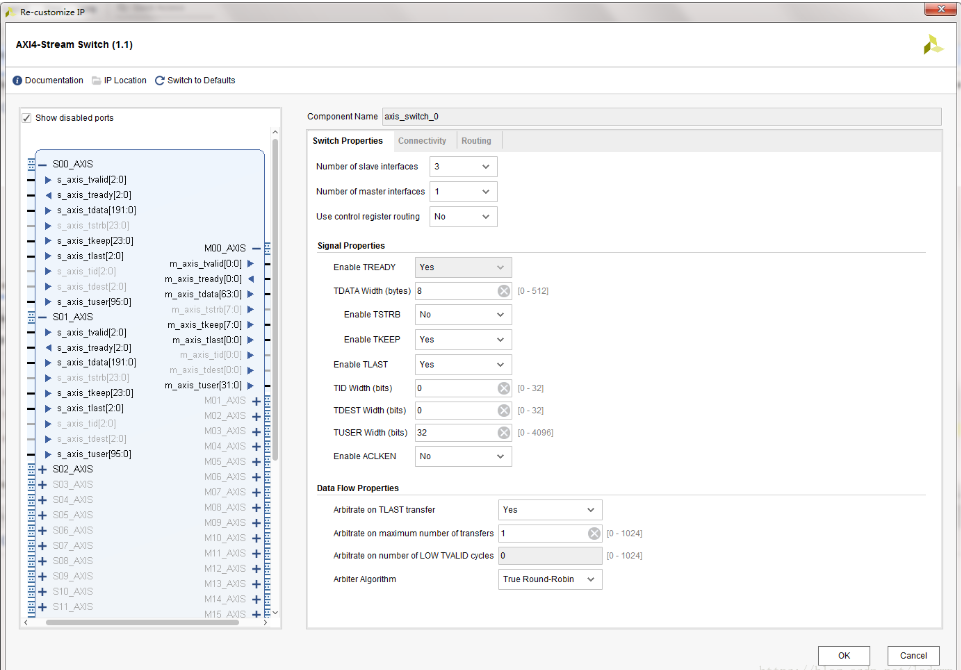

第一點是IP的生成,官方的IP顯示應該是有BUG,我的使用需求是3從1主做仲裁,然后在IP顯示圖中顯示了三組AXIs從接口,但是每個從接口是主接口的位寬的3倍,當時看到這個一度覺得很奇怪,IP的手冊也沒有說明接口的使用方法,后來看例化模板發(fā)現(xiàn)只有一組AXIS從接口,位寬是主接口的3倍,剛好符合我的實際設置情況。

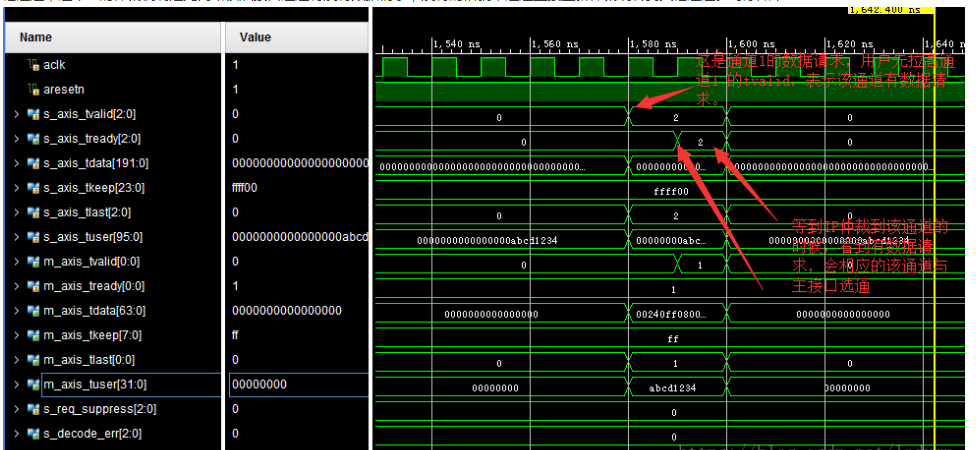

第二點是關(guān)于里面仲裁機制的細節(jié),就是無論選擇什么仲裁方式,對于接入這個AXIS從接口的信號,從接口的S_TVALID一定要提前于S_TREADY拉高,這個是什么意思呢,意思是說,用戶接入從接口的邏輯,不能等到S_TREADY拉高,才把S_TVALID的握手機制,必須先讓S_TVALID拉高告訴IP這個從接口有數(shù)據(jù)請求,當IP剛好仲裁到該從接口的時候,才會拉高S_TREADY接通到M_TREADY,所以某個從接口有數(shù)據(jù)請求的話不提前拉高S_TVALID的話,對應從接口的S_TREADY將不會選通連接到M_TREADY。由此可以推斷,該IP的仲裁切換,是根據(jù)該從接口通道有沒有數(shù)據(jù)請求來決定是否選通主接口與該從接口通道。這個和我平時寫的類似于DDR多通道讀寫的仲裁機制有所不同,我之前是先選通該通道,然后判斷該通道有沒有數(shù)據(jù)請求,沒有則重新仲裁跳轉(zhuǎn)到其他通道,這個IP的仲裁機制是先判斷該從接口通道有沒有數(shù)據(jù)請求,沒有的話就不選通直接重新仲裁跳轉(zhuǎn)到其他通道。

序如下:

第三點是suppress信號,是抑制某個通道與主接口通道選通的控制位,如果置1,對應的從接口將會不與主接口通道選通。

以上的一些使用說明是基于3從1主的總線總裁使用心得,其他情況讀者請自行分析。

-

Switch

+關(guān)注

關(guān)注

1文章

535瀏覽量

59268 -

Stream

+關(guān)注

關(guān)注

0文章

21瀏覽量

8098

發(fā)布評論請先 登錄

如何使用AXI VIP在AXI4(Full)主接口中執(zhí)行驗證和查找錯誤

NVMe IP之AXI4總線分析

是否可以使用AXI4流以某種方式從收發(fā)器中提取輸入數(shù)據(jù)

AXI-stream數(shù)據(jù)傳輸過程

ARM CoreLink AXI4至AHB Lite XHB-400橋接技術(shù)參考手冊

一文詳解ZYNQ中的DMA與AXI4總線

AXI-Stream代碼

關(guān)于AXI4-Stream協(xié)議總結(jié)分享

AXI4 、 AXI4-Lite 、AXI4-Stream接口

使用AXI4總線實現(xiàn)視頻輸入輸出

AXI3與AXI4寫響應的依賴區(qū)別?

Xilinx FPGA AXI4總線(一)介紹【AXI4】【AXI4-Lite】【AXI-Stream】

基于3從1主的AXI4 Stream Switch使用

基于3從1主的AXI4 Stream Switch使用

評論