AXI4-Stream去掉了地址項,允許無限制的數據突發傳輸規模;

二、握手機制

只有當VALID和READY同時為高時,才能進行傳輸。

VALID和READY信號的先后順序有一下三種形式:

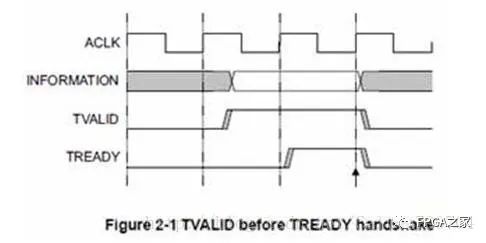

2.1VALID早于READY信號

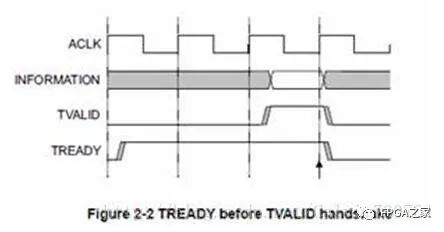

2.2READY信號早于VALID信號

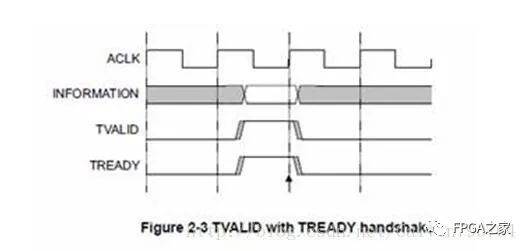

2.3 VALID信號與READY信號同時

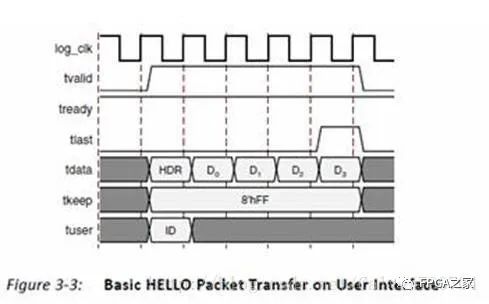

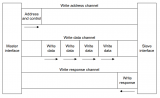

三、基本事務

AXI4-Stream跟AXI4的區別就是AXI4-Stream去除了地址線,這樣就不涉及讀寫數據的概念了,只有簡單的發送與接收說法,減少了延時。由于AXI4-Stream協議(amba4_axi4_stream_v1_0_protocol_spec.pdf)沒有時序圖,因此,我使用XILINX公司的產品指導手冊(pg007_srio_gen2_v3_1.pdf)里的一個時序圖來演示AXI4-Stream各個信號的關系。如下圖所示:

上圖中,tready信號一直處于高電平,表示從設備做好了接收數據準備。tvalid變為高電平的同時,tdata、tkeep、tuser也同時進行發送。在tdata最后一個字節數據時,tlast發送一個高電平脈沖。數據發送完成后,tvalid變為低電平。這樣一次傳輸就完成了。

審核編輯 :李倩

-

信號

+關注

關注

11文章

2852瀏覽量

78271 -

Stream

+關注

關注

0文章

21瀏覽量

8132

原文標題:AXI4-Stream協議總結

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

關于AXI Lite無法正常握手的問題

RDMA簡介9之AXI 總線協議分析2

RDMA簡介8之AXI 總線協議分析1

NVMe IP之AXI4總線分析

NVMe簡介之AXI總線

NVMe協議簡介之AXI總線

一文詳解AXI DMA技術

一文詳解Video In to AXI4-Stream IP核

AMBA AXI4接口協議概述

Xilinx NVMe AXI4主機控制器,AXI4接口高性能版本介紹

關于AXI4-Stream協議總結分享

關于AXI4-Stream協議總結分享

評論