概述

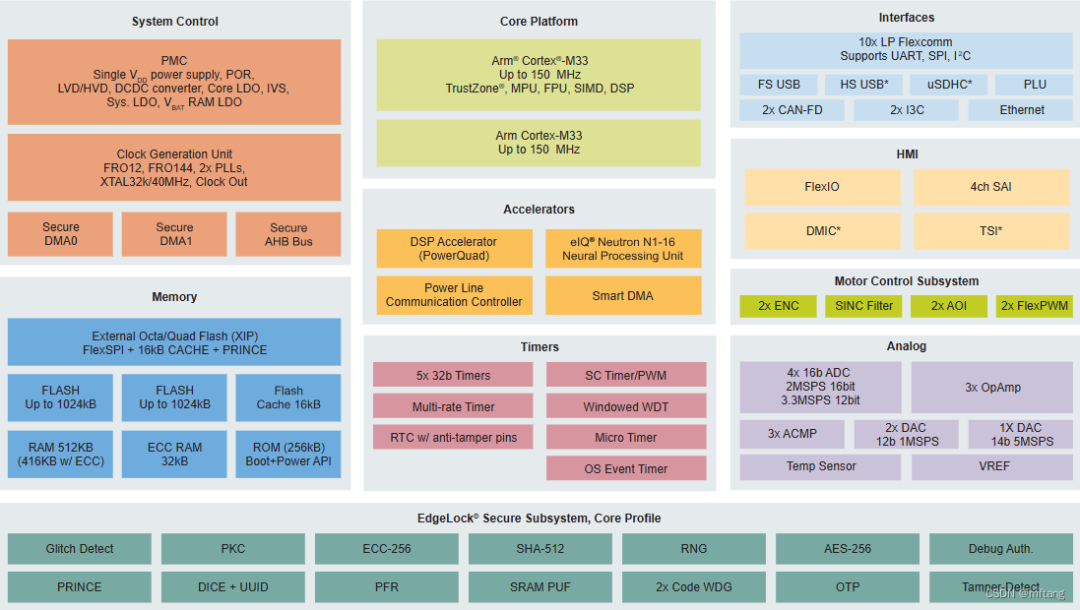

MCXN947芯片是一款高度集成的微控制器,具有強大的處理能力、豐富的外設支持和高級安全特性,適用于多種復雜應用。其中有個非常重要的外設為FlexSPI。

FlexSPI是一種可擴展的串行外設接口,主要用于連接固態存儲設備,如QuadSPI NOR Flash、QuadSPI NAND Flash、HyperRAM等。FlexSPI是一種全面的、靈活的、高性能的解決方案,可以配置成不同的模式以適應不同的存儲設備。

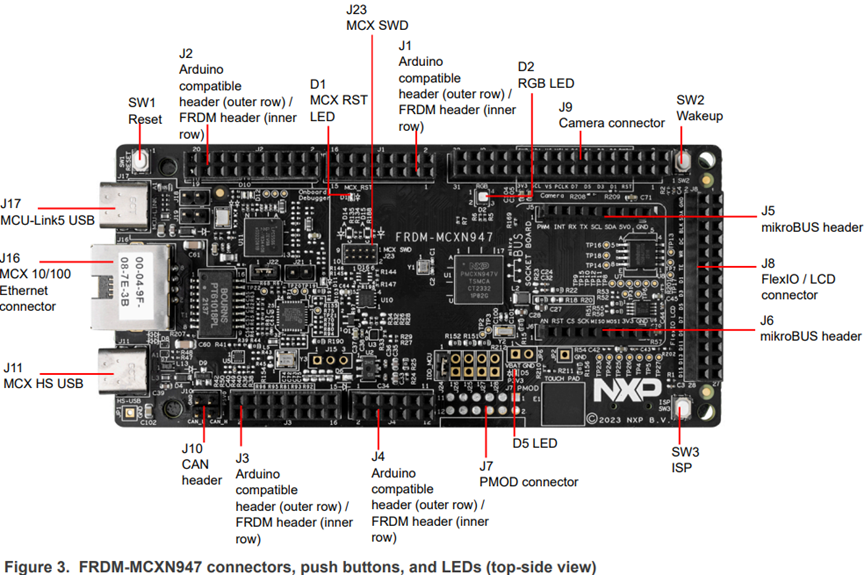

NXP FRDM-MCXN947板是一款基于MCXN947設備的低成本設計與評估板。NXP為MCXN947設備提供了包括硬件評估板、軟件開發集成開發環境(IDE)、示例應用程序和驅動程序在內的工具和軟件支持。該板FlexSPI接口默認接了一塊MT35XU512 NOR Flash。

在本文中,我們將探討如何在MCXN947板的FlexSPI接口接HyperRAM。

硬件環境:

開發板:FRDM-MCXN947

HyperRAM:W956D8MBYA

軟件環境:

IDE:MCUXpresso IDE v11.9.0

SDK:SDK Builder | MCUXpresso SDKBuilder (nxp.com)

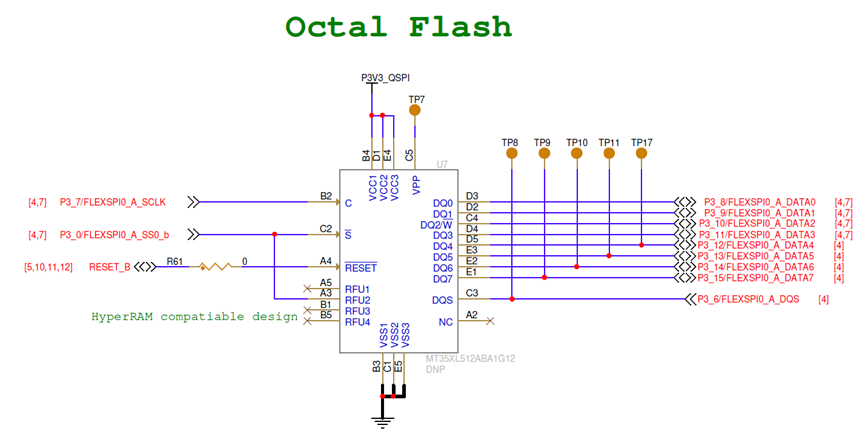

HyperRAM原理圖

以下是官方FRDM-MCXN947中的八線Flash的原理圖,由于W956D8MBYA的HyperRAM的封裝都為TFBGA 24-Ball 5 x 5 Array,所以可以直接進行替換。

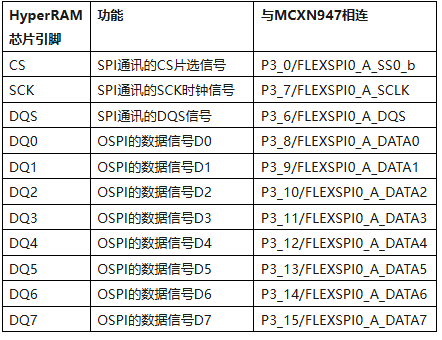

根據以上原理圖,總結出HyperRAM存儲器的信號連接方式見表:

HyperRAM配置流程

3.1 時鐘配置

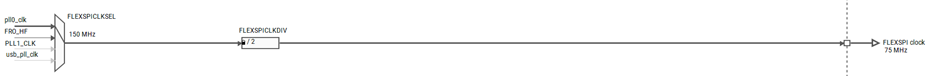

FlexSPI的時鐘需要正確配置。

我們在調試程序的階段還是保險地選擇低一點的頻率,這里選擇75MHz。

3.2 FlexSPI初始化配置結構體詳解

接下來是FlexSPI相關配置,我們可以調用FLEXSPI_GetDefaultConfig獲取一些針對FlexSPI特性結構體flexspi_config_t的一些默認配置,這個默認配置具有一定的普遍性,能兼容大部分的FlexSPI設備,對于該W956D8MBYA 的HyperRAM,在默認配置的基礎上,增加如下幾個參數:

config.ahbConfig.enableAHBPrefetch = true;

config.ahbConfig.enableAHBBufferable = true;

config.ahbConfig.enableReadAddressOpt= true;

config.ahbConfig.enableAHBCachable = true;

config.rxSampleClock= kFLEXSPI_ReadSampleClkLoopbackFromDqsPad;

(1)enableAHBPrefetch:是否使能AHB預讀取特性,當使能時,FlexSPI會讀取比當前AHB突發讀取更多的數據。

(2)enableAHBBufferable :是否使能AHB寫緩沖訪問,在執行寫命令后,不等待其執行完畢就返回,允許后續指令繼續執行,提高系統的并發性。

(3)enableReadAddressOpt:控制是否移除AHB讀取突發起始地址對齊限制,若使能,突發讀取地址沒有字節對齊限制。

(4)enableAHBCachable:使能AHB總線緩存讀取,若命中則從緩存中讀取,但要確保數據的一致性

(5)rxSampleClock:讀數據使用的時鐘源,對于HyperRAM來說,HyperRAM提供讀選通脈沖并從DQS引腳輸入。

3.3 FlexSPI外部設備配置結構體詳解

FlexSPI與外部設備通訊時常常需要與設備協調通訊的時序,如時鐘頻率、數據有效時間等內容,NXP軟件庫提供了結構體類型flexspi_device_config_t專門用于配置這些參數。

typedef struct _flexspi_device_config

{

uint32_t flexspiRootClk;

bool isSck2Enabled;

uint32_t flashSize;

flexspi_cs_interval_cycle_unit_t CSIntervalUnit;

uint16_t CSInterval;

uint8_t CSHoldTime;

uint8_t CSSetupTime;

uint8_t dataValidTime;

uint8_t columnspace;

bool enableWordAddress;

uint8_t AWRSeqIndex;

uint8_t AWRSeqNumber;

uint8_t ARDSeqIndex;

uint8_t ARDSeqNumber;

flexspi_ahb_write_wait_unit_t AHBWriteWaitUnit;

uint16_t AHBWriteWaitInterval;

bool enableWriteMask;

} flexspi_device_config_t;

(1) flexspiRootClk = 75000000,此參數與前面設置的FlexSPI的時鐘頻率一致。

(2) flashSize = 0x2000, Flash的大小,以KB為單位。對于W956D8MBYA,64Mb = 8MB = 8 *1024KB。

(3) CSIntervalUnit = kFLEXSPI_CsIntervalUnit1SckCycle,此參數用于配置CS信號線間隔的時間單位。

(4) CSInterval = 2,此參數用于配置CS信號線有效與無效切換的最小時間間隔,單位為上面CSIntervalUnit成員的配置。

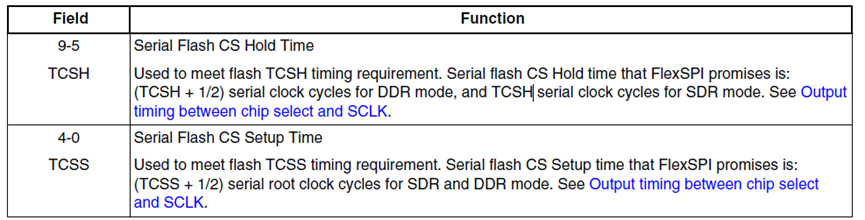

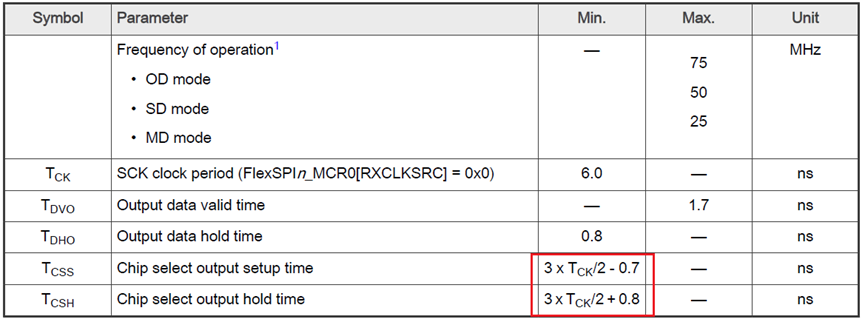

(5) CSHoldTime = 3,此參數用于設定CS信號線的保持時間,單位為FlexSPI根時鐘周期。

(6) CSSetupTime=3,此參數用于設定CS信號線的建立時間,單位為FlexSPI根時鐘周期。

根據MCXNx4x datasheet,= 6ns,最小的= 8.3ns,最小的= 9.8ns。時鐘為75M的周期時間大約是13.3ns。故CSHoldTime和CSSetupTime大于等于1即可,均配置成3。

(7) dataValidTime=2,寄存器DLLACR和DLLBCR,本成員用于配置通訊中的數據有效時間,單位為納秒。

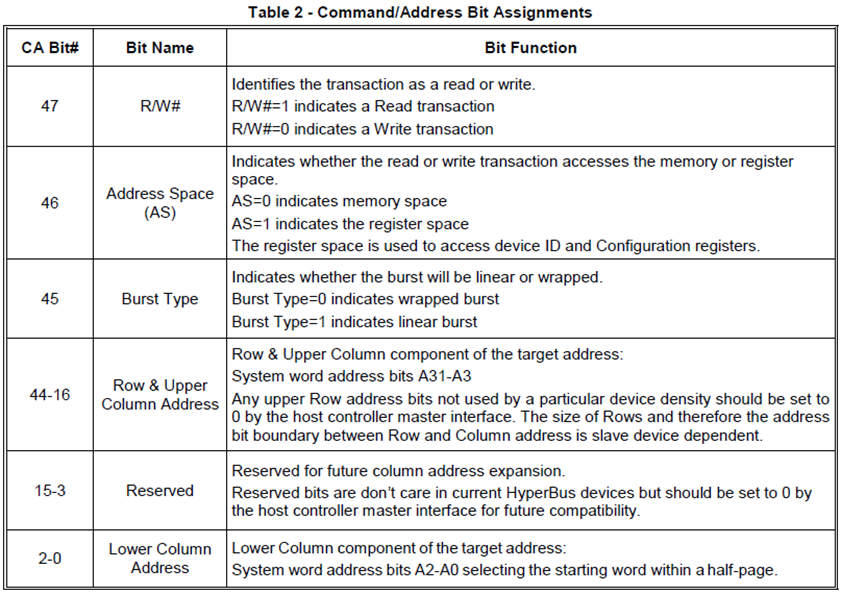

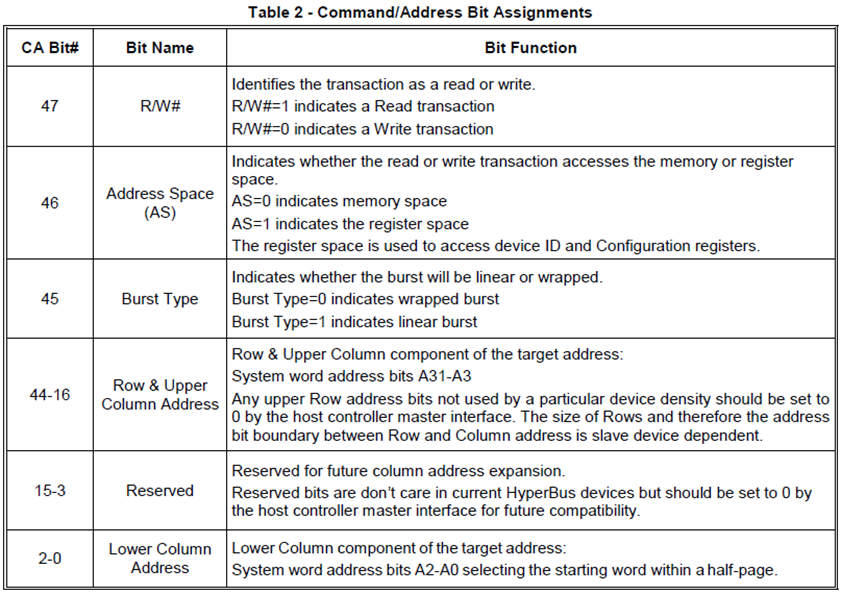

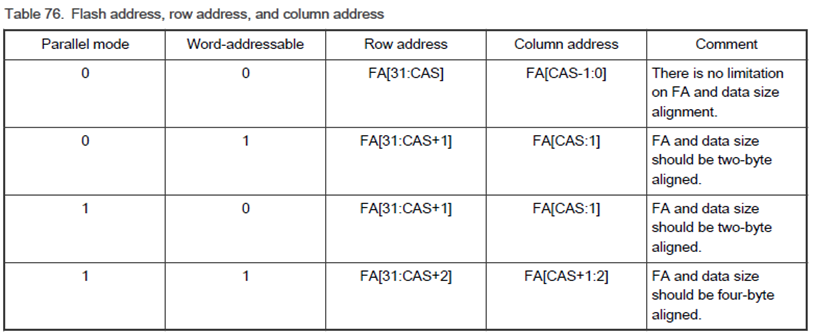

(8) columnspace = 3,低位列地址寬度,對于這個HyperRAM來說,是用行列進行尋址的,這里列地址的寬度為3位。

(9) enableWordAddress = true,配置是否使能2字節可尋址功能,使能后會以16位的數據格式對HyperRAM進行訪問。

(10) AWRSeqIndex = 1,對應寫的時序序列在LUT中的索引。

(11) AWRSeqNumber =1,此參數配置AHB寫命令的序列數目。

(12) ARDSeqIndex = 0,對應讀的時序序列在LUT中的索引。

(13) ARDSeqNumber =1,此參數配置AHB讀命令的序列數目。

(14) enableWriteMask = true,此參數用于設置FlexSPI寫外部設備時是否使能驅動DQS位作為掩碼,這種功能在訪問數據寬度為16位時用于地址對齊。

3.4 LUT表格配置

下面是HyperRAM 讀和寫的時序LUT表格的代碼示例,

const uint32_t customLUT[CUSTOM_LUT_LENGTH] = {

/* Read Data */

[4 * PSRAM_CMD_LUT_SEQ_IDX_READDATA] = FLEXSPI_LUT_SEQ(kFLEXSPI_Command_DDR,kFLEXSPI_8PAD, 0xA0, kFLEXSPI_Command_RADDR_DDR, kFLEXSPI_8PAD, 0x18),

[4 * PSRAM_CMD_LUT_SEQ_IDX_READDATA + 1] = FLEXSPI_LUT_SEQ(kFLEXSPI_Command_CADDR_DDR,kFLEXSPI_8PAD, 0x10, kFLEXSPI_Command_DUMMY_RWDS_DDR, kFLEXSPI_8PAD, 0x07),

[4 * PSRAM_CMD_LUT_SEQ_IDX_READDATA + 2] = FLEXSPI_LUT_SEQ(kFLEXSPI_Command_READ_DDR,kFLEXSPI_8PAD, 0x04, kFLEXSPI_Command_STOP, kFLEXSPI_1PAD, 0x00),

/* Write data */

[4 * PSRAM_CMD_LUT_SEQ_IDX_WRITEDATA] = FLEXSPI_LUT_SEQ(kFLEXSPI_Command_DDR,kFLEXSPI_8PAD, 0x20, kFLEXSPI_Command_RADDR_DDR, kFLEXSPI_8PAD, 0x18),

[4 * PSRAM_CMD_LUT_SEQ_IDX_WRITEDATA + 1] = FLEXSPI_LUT_SEQ(kFLEXSPI_Command_CADDR_DDR,kFLEXSPI_8PAD, 0x10, kFLEXSPI_Command_DUMMY_RWDS_DDR, kFLEXSPI_8PAD, 0x07),

[4 * PSRAM_CMD_LUT_SEQ_IDX_WRITEDATA + 2] = FLEXSPI_LUT_SEQ(kFLEXSPI_Command_WRITE_DDR,kFLEXSPI_8PAD, 0x04, kFLEXSPI_Command_STOP, kFLEXSPI_1PAD, 0x00),

};

(1) 我們使用的是8線差分的HyperRAM,在時鐘的雙邊沿都采樣,所以與外部存儲器通信時用的數據線的個數均為kFLEXSPI_8PAD。

(2) HyperRAM和HyperFlash是基于Cypress Semiconductor的HyperBus接口規范設計的存儲器產品,這個operand是在該規范中定義的,所以讀操作operand固定為0xA0,寫數據的operand固定為0x20。

(3) CADDR_DDR列地址,由于一次傳輸的字節一定是8的倍數,如果你傳的行列地址大于特定大小的HyperRAM最大的行和列,FlexSPI會自動將高位置0。

上表中顯示低16位是列地址,有效位有3位,高13位是預留兼容的列地址位,需要置0。所以這里列地址的時序參數需要填16,即0x10。

(4) RADDR_DDR行地址,如圖所示,如果 FLSHxxCR1[CAS] 位不為 0 ,那么 FlexSPI 外設在傳輸時序里會拆分實際映射 Flash Address (即存儲器自身偏移地址) 為行地址 FA[31:CAS] 和列地址 [CAS-1:1] 來分別傳輸。對于字可尋址閃存設備,不需要地址的最后一位,因為閃存是按照兩個字節讀取和編程的。Flexspi 一個字為兩個字節,所有需要如果2個字節對齊,就需要少一位地址。行列地址加一起少一位。W956D8MBYA有64Mbit,即2^26,列地址還有3位,所以理論上行地址需要傳輸26-1-3=22位,即可尋址整個HyperRAM。然后向8位對齊,不然FlexSPI會在低位補0,就不是我們要訪問的地址了。所以參數為0x18,即24位。

實驗驗證 我們可以利用簡單的AHB讀寫來驗證此HyperRAM是否可以工作。

代碼如下:

for (i = 0; i < sizeof(s_psram_write_buffer); i++)

{

s_psram_write_buffer[i] = i;

}

memcpy((uint32_t*)(EXAMPLE_FLEXSPI_AMBA_BASE), s_psram_write_buffer, sizeof(s_psram_write_buffer));

memcpy(s_psram_read_buffer,(uint32_t*)(EXAMPLE_FLEXSPI_AMBA_BASE) , sizeof(s_psram_read_buffer));

if (memcmp(s_psram_read_buffer, s_psram_write_buffer,sizeof(s_psram_write_buffer)) == 0)

{

PRINTF("AHB Command Read/Write data successfully !

");

}

當你的串口打印出"AHB Command Read/Write data successfully!"

證明你的FlexSPI接HyperRAM現在可以正常工作啦!

作者:Hang Zhang

-

微控制器

+關注

關注

48文章

7906瀏覽量

153701 -

NXP

+關注

關注

61文章

1332瀏覽量

187451 -

接口

+關注

關注

33文章

8943瀏覽量

153202 -

HyperRAM

+關注

關注

0文章

5瀏覽量

1617

原文標題:MCX N947:FlexSPI接HyperRAM分析和配置

文章出處:【微信號:NXP_SMART_HARDWARE,微信公眾號:恩智浦MCU加油站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

恩智浦MCU MCXN947 基于MCUXpresso Config tools創建IIC的教程步驟

FRDM-MCXN947的純Linux命令行環境搭建

關于將Flash寫入FRDM-MCXN947的問題求解

使用FRDM-MXCN947板,在MCUXpresso IDE中調試期間嘗試從下載寫入QSPI閃存出現報錯的原因?

MCXN947使用ADC并編寫代碼,總是報警告是怎么回事?

MCXN947如何配置和外擴PSRAM?

如何在HyperRAM中讀/寫?

FlexSPI1 ISSI HyperRAM初始化問題求解

I.MXRT1170從FLEXSPI2啟動

恩智浦MCX系列MCU的新品MCXN947

《恩智浦FRDM-MCXN947開發實踐指南》上線啦

MCXN947系列高性能微控制器產品介紹

如何在MCXN947板的FlexSPI接口接HyperRAM

如何在MCXN947板的FlexSPI接口接HyperRAM

評論