CMOS集成電路使用時(shí)的技術(shù)要求,CMOS IC requirements

關(guān)鍵字:CMOS集成電路使用時(shí)的技術(shù)要求

CMOS集成電路使用時(shí)的技術(shù)要求

1.CMOS集成電路輸入端的要求

CMOS集成電路具有很高的輸入阻抗,其內(nèi)部輸入端接有二極管保護(hù)電路.以防范外界干擾、沖擊和靜電擊穿。CMOS集成電路的輸入端懸空時(shí)輸入阻抗高,易受外界噪聲干擾,使電路產(chǎn)生誤動(dòng)作。破壞正常的邏輯關(guān)系,而且也極易使柵極感應(yīng)靜電造成擊穿損壞。所以,對(duì)于“與”門(mén)、“與非”門(mén)CMOS集成電路的多余端采取接高電平措施;對(duì)于“或”門(mén)、“或非”門(mén)CMOS集成電路的多余端采取接低電平措施。如果電路的工作速度要求不高,功耗也不需要特別考慮,則可采用多余的輸入端和使用端并用的措施加以解決。輸入端的電流不能超過(guò)1mA(極限值為10mA),必須在輸入端加適當(dāng)?shù)?a target="_blank">電阻進(jìn)行限流保護(hù)(一般在12V的工作電壓時(shí),輸入端加1.2kΩ的電阻進(jìn)行限流保護(hù))。輸入信號(hào)不可大于VDD小于VSS,否則輸入保護(hù)二極管會(huì)因正向偏置而引起大電流。在工作或測(cè)試時(shí),必須先接通電源后再加信號(hào),先撤除信號(hào)后再關(guān)電源。如果輸入信號(hào)的上升或下降時(shí)間過(guò)長(zhǎng)。容易造成虛假觸發(fā)而導(dǎo)致器件失去正常功能,還會(huì)造成損耗。對(duì)4000B系列,上升或下降時(shí)間限于15us以?xún)?nèi)。否則,須使用史密特觸發(fā)電路對(duì)輸入信號(hào)整形。在CMOS集成電路的輸入端與機(jī)械接點(diǎn)連接或應(yīng)用在其他特殊情況下,輸入端接線過(guò)長(zhǎng)。使分布電容和分布電感較大,很容易形成LC振蕩,破壞CMOS中的保護(hù)二極管。

CMOS集成電路的工作電源電壓一般在3—18V之間.由于CMOS集成電路的工作電壓范圍寬,不使用穩(wěn)壓的電源電路也可以工作。但當(dāng)系統(tǒng)中有模擬應(yīng)用的門(mén)電路時(shí),最低工作電壓則不應(yīng)低于4.5V。工作在不同電源電壓下的器件,其輸出阻抗、工作速度和功耗也會(huì)不同.在使用中應(yīng)注意。CMOS器件輸出端不允許直接和VCC或VSS連接,否則將導(dǎo)致器件損壞。

2.防靜電要求

如果輸入電路中沒(méi)有一定的抗靜電措施,CMOS集成電路很容易造成電路的毀滅性破壞。CMOS集成電路應(yīng)放在抗靜電的材料中儲(chǔ)存和運(yùn)輸。工作人員不宜穿化纖衣服、硬塑料底的鞋,手或工具在接觸集成塊前最好先接一下地。對(duì)器件引線矯直、彎曲或人工焊接時(shí).使用的設(shè)備必須接地良好。由于保護(hù)電路吸收的瞬變能量有限,太大的瞬變信號(hào)和過(guò)高的靜電電壓將使保護(hù)電路失去作用。在焊接CMOS管腳時(shí),電烙鐵必須可靠接地,利用電烙鐵斷電后的余熱焊接,并先焊接其接地腳,以防電烙鐵漏電擊穿器件輸入端。總而言之,CMOS集成電路在包裝、儲(chǔ)存、運(yùn)輸、焊接等環(huán)節(jié)中可能產(chǎn)生的靜電問(wèn)題,仍須謹(jǐn)慎對(duì)待,采取各種措施預(yù)防,并且接地良好、可靠。

3。接口與驅(qū)動(dòng)要求

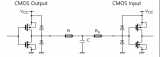

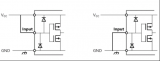

CMOS集成電路與運(yùn)放接口時(shí)。運(yùn)放如果使用單電源。并且與CMOS使用的電源一樣,則可直接連接。如果運(yùn)放采用雙電源。CMOS采用的是獨(dú)立的另一組電源,在電路中,則要采用鉗位保護(hù)電路,使CMOS輸入電壓處在10V與地之間。接口電阻既作為CMOS的限流電阻,又對(duì)二極管進(jìn)行限流保護(hù)。邏輯器件的接口電路主要應(yīng)注意電平匹配和輸出能力兩個(gè)問(wèn)題,要和器件的電源電壓結(jié)合起來(lái)考慮。例如,CMOS集成電路和TTL等其他電路的連接.其電路相互之間的電源電壓和輸入、輸出電平及電流不相同,則其前級(jí)電路的輸出電流必須滿足后級(jí)電路對(duì)輸入電流的要求:前級(jí)電路輸出的邏輯電平必須滿足后級(jí)電路對(duì)輸入電平的要求,它們之間的連接是通過(guò)電平轉(zhuǎn)換或電流轉(zhuǎn)換電路完成的。CMOS集成電路既可以將同一個(gè)芯片幾個(gè)同類(lèi)電路并接起來(lái)提高驅(qū)動(dòng)能力。也可以選用驅(qū)動(dòng)能力較強(qiáng)的緩沖放大器來(lái)提高驅(qū)動(dòng)能力。 ◇山東郎筠

聲明:本文內(nèi)容及配圖由入駐作者撰寫(xiě)或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問(wèn)題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

熱點(diǎn)推薦

CMOS超大規(guī)模集成電路制造工藝流程的基礎(chǔ)知識(shí)

本節(jié)將介紹 CMOS 超大規(guī)模集成電路制造工藝流程的基礎(chǔ)知識(shí),重點(diǎn)將放在工藝流程的概要和不同工藝步驟對(duì)器件及電路性能的影響上。

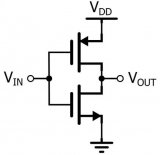

浮思特 | CMOS技術(shù)原理與應(yīng)用:從晶體管結(jié)構(gòu)到反相器設(shè)計(jì)

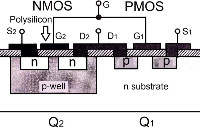

MOSFET在數(shù)字電路中的常見(jiàn)形式是互補(bǔ)MOS(CMOS)電路。CMOS技術(shù)將n溝道和p溝道MOSFET成對(duì)

硬件基礎(chǔ)篇——TTL與CMOS電平

電平TTL集成電路主要由BJT晶體管構(gòu)成,如STC單片機(jī),電平規(guī)范如下:輸出模式:Uoh ≥ 2.4V,Uol≤0.4V;輸入模式:Uih ≥ 2.0V,Uil≤0.8V;3、CMOS電平CMOS

發(fā)表于 03-22 15:21

CMOS集成電路的基本制造工藝

本文主要介紹CMOS集成電路基本制造工藝,特別聚焦于0.18μm工藝節(jié)點(diǎn)及其前后的變化,分述如下:前段工序(FrontEnd);0.18μmCMOS前段工序詳解;0.18μmCMOS后段鋁互連工藝;0.18μmCMOS后段銅互連工藝。

愛(ài)普生(EPSON) 集成電路IC

隨著技術(shù)的發(fā)展,Epson在集成電路(IC)方面的研發(fā)和生產(chǎn)也逐步成為其重要的業(yè)務(wù)之一。Epson的集成電路主要應(yīng)用于各種電子設(shè)備中,包括消費(fèi)類(lèi)電子、工業(yè)設(shè)備、汽車(chē)電子等多個(gè)領(lǐng)域。愛(ài)普

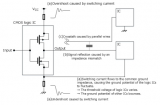

CMOS邏輯IC應(yīng)用中的噪聲問(wèn)題和解決對(duì)策

前面兩期的芝識(shí)課堂,我們介紹了大量關(guān)于CMOS邏輯IC應(yīng)用的一些細(xì)節(jié)事項(xiàng),本期課堂讓我們進(jìn)入實(shí)際的應(yīng)用案例,解決電路設(shè)計(jì)中的噪聲問(wèn)題。

如何優(yōu)化CMOS邏輯IC的性能

在上期的芝識(shí)課堂中,我們介紹了一部分CMOS邏輯IC設(shè)計(jì)的常見(jiàn)問(wèn)題以及處理辦法。本期課堂將繼續(xù)探討如何優(yōu)化CMOS邏輯IC的性能,特別是負(fù)載電容連接技巧和功耗計(jì)算,這些因素對(duì)于

CMOS邏輯IC的使用注意事項(xiàng)

當(dāng)今的電子設(shè)計(jì)領(lǐng)域,CMOS邏輯IC因其低功耗、高集成度和良好的噪聲抑制能力而得到廣泛應(yīng)用。然而,要充分發(fā)揮CMOS邏輯IC的性能優(yōu)勢(shì),確保

CMOS逆變器的功耗介紹

CMOS 反相器的發(fā)展為集成電路提供了基本功能,是技術(shù)史上的一個(gè)轉(zhuǎn)折點(diǎn)。該邏輯電路突出了 CMOS 獨(dú)特的電氣特性,非常適合高密度、高性能數(shù)

最新CMOS技術(shù)發(fā)展趨勢(shì)

隨著科技的飛速發(fā)展,CMOS技術(shù)也在不斷進(jìn)步,以滿足日益增長(zhǎng)的性能需求。從最初的簡(jiǎn)單邏輯門(mén)到現(xiàn)在的復(fù)雜集成電路,CMOS技術(shù)已經(jīng)成為推動(dòng)數(shù)字

什么是集成電路?有哪些類(lèi)型?

集成電路,又稱(chēng)為IC,按其功能結(jié)構(gòu)的不同,可以分為模擬集成電路、數(shù)字集成電路和數(shù)/模混合集成電路三大類(lèi)。

單片集成電路和混合集成電路的區(qū)別

單片集成電路(Monolithic Integrated Circuit,簡(jiǎn)稱(chēng)IC)和混合集成電路(Hybrid Integrated Circuit,簡(jiǎn)稱(chēng)HIC)是兩種不同的電子電路

如何判斷cmos有無(wú)燒壞

CMOS(互補(bǔ)金屬氧化物半導(dǎo)體)是一種廣泛應(yīng)用于集成電路制造的半導(dǎo)體技術(shù)。CMOS電路具有低功耗、高集成

怎么判斷cmos門(mén)電路的輸出狀態(tài)

CMOS(互補(bǔ)金屬氧化物半導(dǎo)體)是一種廣泛使用的集成電路技術(shù),它利用了兩種類(lèi)型的晶體管:N型和P型。CMOS門(mén)電路是數(shù)字邏輯

HV-CMOS工藝制程技術(shù)簡(jiǎn)介

BCD 工藝制程技術(shù)只適合某些對(duì)功率器件尤其是BJT 或大電流 DMOS 器件要求比較高的IC產(chǎn)品。BCD 工藝制程技術(shù)的工藝步驟中包含大量工藝是為了改善 BJT 和 DMOS 的大電

CMOS集成電路使用時(shí)的技術(shù)要求,CMOS IC requirements

CMOS集成電路使用時(shí)的技術(shù)要求,CMOS IC requirements

評(píng)論