MOSFET在數字電路中的常見形式是互補MOS(CMOS)電路。CMOS技術將n溝道和p溝道MOSFET成對集成在同一芯片上,成為數字集成電路的主導技術,相比單獨使用NMOS和PMOS晶體管具有諸多優勢。

發展互補MOSFET(CMOS)技術的主要動機是實現數字電路邏輯門的高速運行與低功耗。CMOS技術支持構建多種高性能模擬和數字電路,其工作原理與BJT邏輯器件類似,但通過電壓而非電流觸發——CMOS柵極不存在電流輸入。

1970年代CMOS技術僅應用于電子表等特定消費領域。但到1980年代,憑借低功耗、高噪聲容限、更寬的工作溫度/電壓范圍、電路簡化、抗電遷移、高可靠性及版圖設計便捷等優勢,VLSI技術開始轉向CMOS。80年代VLSI的發展使單芯片集成度達到數百萬晶體管。目前CMOS已成為VLSI數字和混合信號設計的主流技術,相比晶體管-晶體管邏輯(TTL),CMOS速度更快、更適應低電源電壓工作且功耗更低。

下文將闡述n型與p型互補晶體管對如何構成CMOS模塊基礎。

反相器介紹

反相器是實現信號反轉的邏輯元件。數字電路中,二進制算術和開關函數的數學運算最佳采用0(低電平)和1(高電平)表示。當邏輯電平定義為0V(地)和V伏時,反相器使0V輸入產生V伏輸出,反之亦然。

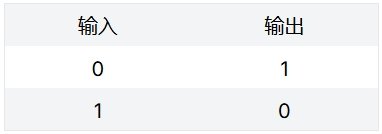

除文字描述外,真值表可系統呈現所有可能輸入組合及其對應輸出。表1即為反相器真值表。

表1

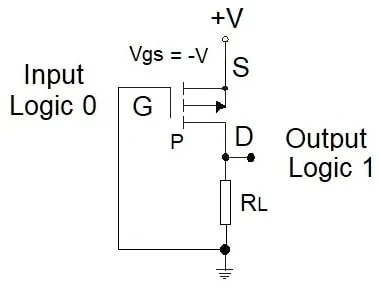

表1NMOS反相器

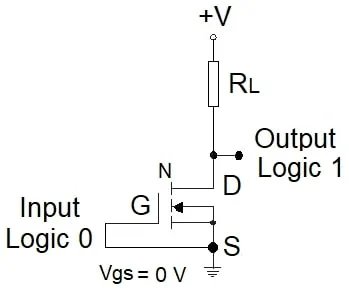

常規用法以柵極為輸入、漏極為輸出,源極與襯底接地。圖1顯示增強型n溝道MOS(NMOS)在輸入接地時的符號與連接。正電壓+V通過負載電阻(RL)為漏極供電形成偏置。負載電阻產生Id?RL壓降(Id為漏極電流),襯底、源極和柵極均接地。

圖1

圖1輸入接地時,柵電容電壓為零(邏輯0),電容保持放電狀態,晶體管無導電溝道形成,呈現高阻開路特性,漏源電流Id極低。因負載電阻壓降可忽略,輸出為正電壓+V(邏輯1)。故輸入邏輯0時晶體管截止,輸出近似電源電壓(邏輯1)。

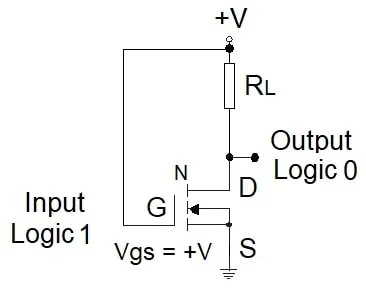

當柵極施加正電壓時,電子被吸引至柵極氧化層。當電荷積累足夠時,硅表面轉變為n型材料,形成連接n型源漏區的低阻n溝道,使漏極電流Id從漏極流向源極。柵極正電壓使晶體管開啟(閾值電壓VT),表現為閉合開關。此時n溝道電阻遠小于負載電阻,輸出近似接地(邏輯0)。

圖2

圖2綜上,輸入邏輯0時輸出近V伏(邏輯1),輸入邏輯1時輸出接地(邏輯0),實現反相功能。"增強型"得名于晶體管常態開路、導通需激活的特性。需注意:柵極連接電容使直流輸入始終開路,僅電容充放電時存在輸入電流。

NMOS反相器的缺陷在于晶體管導通時存在電源到地的持續電流,這在復雜電路中會導致顯著功耗增加。

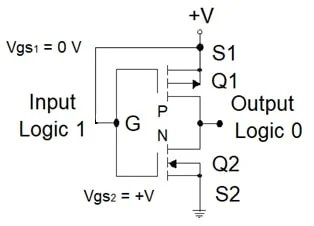

PMOS反相器

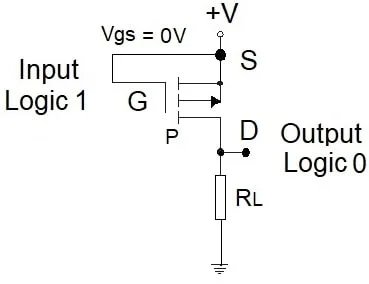

PMOS晶體管以互補方式工作,其反相器連接與NMOS相反。圖3展示輸入接+V(邏輯1)時PMOS反相器的符號與連接,襯底和源極接+V,負載電阻接地。

圖3

圖3+V輸入(Vgs=0V)不充電柵電容,晶體管保持截止,其高阻使輸出接地(邏輯0)。接地輸入(Vgs=-V)使柵電容充電,電容另一側的正電荷將n型硅表面轉為p型材料,形成源漏間低阻p溝道,晶體管開啟,Id從源極流向漏極。此時導通電阻遠小于負載電阻,輸出近+V(邏輯1)。與NMOS相同,輸入邏輯0輸出邏輯1,反之亦然。

圖4

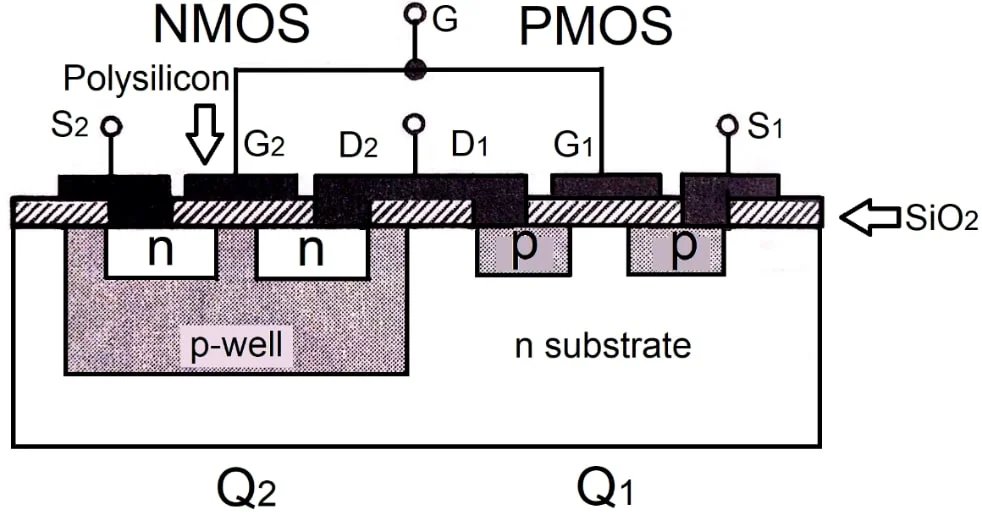

圖4CMOS剖面結構

CMOS制造于兼具電氣參考和機械支撐的襯底上。剖面圖沿晶體管中部切割晶圓呈現側視圖。圖5為CMOS柵極的簡易剖面,NMOS和PMOS集成在同一芯片:p溝道器件右側形成p溝道,n溝道器件左側形成n溝道。

圖5

圖5此結構中,PMOS直接制作于n型襯底(體區),NMOS制作于p型區域(p阱)。阱是低摻雜深擴散區,既作為器件襯底又提供隔離。也可采用p型襯底配合n阱工藝。n型體區與p阱的連接方式未具體說明。

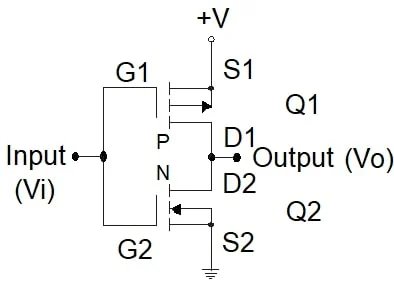

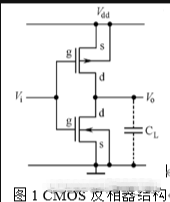

CMOS反相器

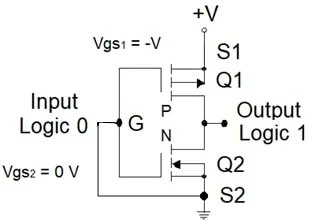

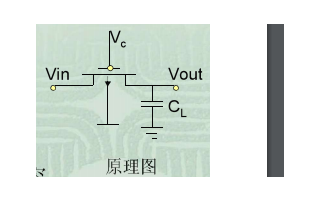

CMOS反相器結構簡潔(圖6),將功耗降至最低。它由增強型NMOS和PMOS串聯構成,各晶體管互為對方的負載電阻。柵極并聯為輸入端,漏極連接處為輸出端。PMOS(Q1)襯底和源極接+V,NMOS(Q2)對應端接地。

圖6

圖6輸入+V(邏輯1)時,Q2的Vgs=+V導通(漏源電阻極小),Q1的Vgs=0V截止(漏源電阻極大),根據分壓規則輸出近0V(邏輯0)(圖7)。輸入接地時,Q2截止,Q1的Vgs=-V導通,此時Q1低阻、Q2高阻,輸出近+V(邏輯1)(圖8)。NMOS作為下拉管將輸出拉至地,PMOS作為上拉管將輸出拉至+V。

圖7

圖7 圖8

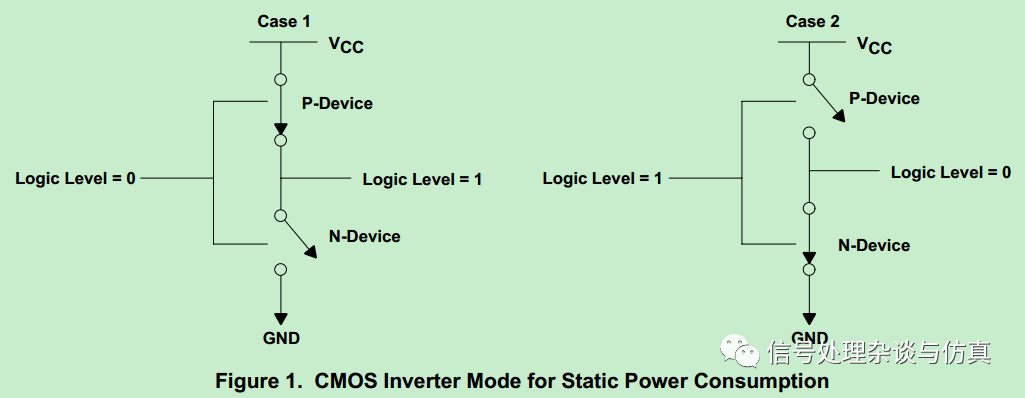

圖8CMOS反相器功耗

CMOS電路直流輸入電流可忽略。因截止晶體管將漏電流限制為泄漏值,兩種狀態的功耗均極低,僅輸入切換時出現顯著功耗。雖然CMOS平均功耗低,但其值取決于電路活動性:靜態電路功耗極小,此特性使CMOS總體比TTL更高效;但高頻狀態切換時功耗可能接近TTL水平。

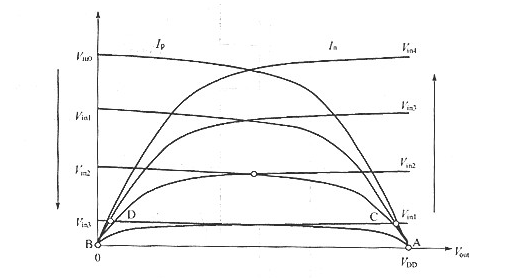

CMOS反相器直流電壓傳輸特性

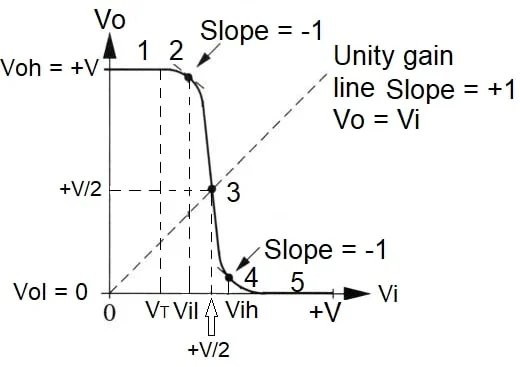

直流電壓傳輸特性(VTC)可量化反相器工作狀態,即輸出電壓(Vo)隨輸入電壓(Vi)的變化曲線。CMOS反相器的VTC近乎理想,圖9展示Q1/Q2匹配時的VTC曲線。

圖9

圖9匹配晶體管使VTC對稱且上下拉電流驅動能力相等。CMOS反相器的重要特性是高輸出電壓擺幅。如圖9所示,根據Q1/Q2工作模式,VTC分為五段:

Q2截止

Q2飽和/Q1線性

Q1/Q2均飽和

Q1飽和/Q2線性

Q1截止

該曲線將邏輯0/1定義為電壓范圍,且輸入/輸出的邏輯電平閾值不同。關鍵參數包括輸入高低電平Vih/Vil、輸出高低電平Voh/Vol及閾值電壓VT。Vih/Vil對應VTC斜率dVo/dVi=-1的點:Vi>Vil時增益增加進入轉換區;Vi

數字設計追求窄轉換區,而模擬設計則關注該區域。

CMOS技術回顧

互補MOS(CMOS)在數字電路中無處不在,成為復雜數字IC的首選技術。"互補"指同一芯片上配對的增強型NMOS和PMOS:導通晶體管漏源電阻極低,截止時極高。

CMOS反相器采用串聯的NMOS和PMOS,PMOS接+V,NMOS接地。輸入邏輯0時NMOS截止/PMOS導通,輸出上拉至邏輯1;輸入邏輯1時NMOS導通/PMOS截止,輸出下拉至邏輯0。與其他FET器件相同,CMOS輸入柵極絕緣,故輸入電流極小。CMOS僅在狀態切換時產生顯著功耗,這一無靜態功耗的特性使其自誕生起就大獲成功。

-

CMOS

+關注

關注

58文章

5985瀏覽量

238058 -

反相器

+關注

關注

6文章

315瀏覽量

44043 -

晶體管

+關注

關注

77文章

9978瀏覽量

140640

發布評論請先 登錄

CMOS反相器構建Big Muff

CMOS晶體管,CMOS晶體管是什么意思

MOS反相器和CMOS反相器的詳細資料說明

浮思特 | CMOS技術原理與應用:從晶體管結構到反相器設計

浮思特 | CMOS技術原理與應用:從晶體管結構到反相器設計

評論