概述

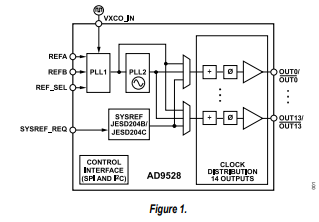

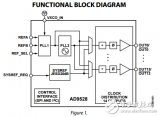

AD9528是一款雙級PLL,集成JESD204B/JESD204C SYSREF發生器,可用于多器件同步。第一級鎖相環(PLL) (PLL1)通過減少系統時鐘的抖動,從而實現輸入基準電壓調理。第二級PLL (PLL2)提供高頻時鐘,可實現來自時鐘輸出驅動器的較低積分抖動以及較低寬帶噪聲。外部VCXO提供PLL2所需的低噪聲基準電壓,以滿足苛刻的相位噪聲和抖動要求,實現可以接受的性能。片內VCO的調諧頻率范圍為3.450 GHz至4.025 GHz。集成的SYSREF發生器輸出單次、N次或連續信號,并與PLL1和PLL2輸出同步,以便對齊多個器件的時間。

數據表:*附件:AD9528提供14路LVDS HSTL輸出的JESD204B JESD204C時鐘發生器技術手冊.pdf

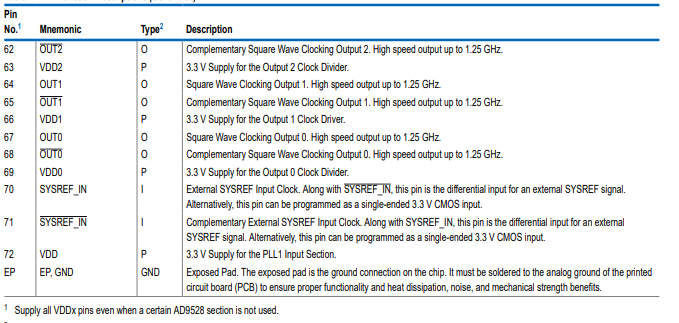

AD9528產生最高頻率為1.25 GHz的六路輸出(輸出0至輸出3、輸出12和輸出13),以及最大頻率高達1 GHz的八路輸出。每一路輸出均可配置為直接從PLL1、PLL2或內部SYSREF發生器輸出。14路輸出通道的每一路都包含一個帶數字相位粗調功能的分頻器,以及一個模擬微調相位延遲模塊,允許全部14路輸出具有時序對齊的高度靈活性。AD9528還可用作靈活的雙通道輸入緩沖器,以便實現14路器件時鐘和/或SYSREF信號的分配。啟動時,AD9528直接向輸出12和輸出13發送VCXO信號,用作啟動就緒時鐘。

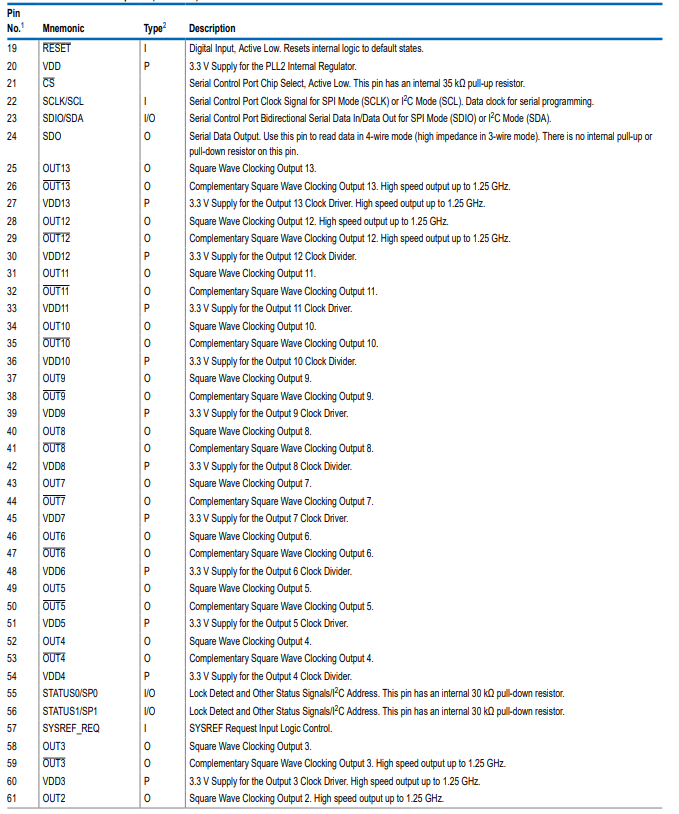

注意在整篇數據手冊中,雙功能引腳名稱通過適用的相關功能來引用。

應用

- 高性能無線收發器

- LTE和多載波GSM基站

- 無線和寬帶基礎設施

- 醫療儀器

- 為高速ADC、DAC、DDS、DDC、DUC、MxFE提供時鐘;支持JESD204B/JESD204C

- 低抖動、低相位噪聲時鐘分配

- 自動測試設備(ATE)和高性能儀器儀表

特性

- 14路輸出,可配置為HSTL或LVDS

- 最大輸出頻率

- 6路輸出高達1.25 GHz

- 8路輸出高達1 GHz

- 取決于壓控晶體振蕩器(VCXO)頻率精度(啟動頻率精度:<±100 ppm)

- 每路輸出均提供專用的8位分頻器

- 粗調延遲: 63個步長為RF VCO分頻器輸出頻率一半的步進,不受抖動影響

- 微調延遲: 15個步進,分辨率為31 ps

- 典型輸出間偏斜: 20 ps

- 針對奇數分頻器設置提供占空比校正

- 輸出12和輸出13,上電時VCXO輸出

- 絕對輸出抖動: <160 f

S(122.88 MHz時)

12 kHz至20 MHz積分范圍 - 數字鎖頻檢測

- SPI和I^2^C兼容型串行控制端口

- 雙PLL架構

- PLL1

- 利用外部VCXO實現參考輸入時鐘清零

- 鑒相器速率:最高110 MHz

- 冗余參考輸入

- 自動和手動參考切換模式

- 恢復式和非恢復式切換

- 保持模式支持參考丟失檢測

- VCXO提供的低噪聲LVDS/HSTL輸出可用于射頻/中頻(RF/IF)頻率合成器

- PLL2

- 鑒相器速率:最高275 MHz

- 集成低噪聲VCO

- PLL1

框圖

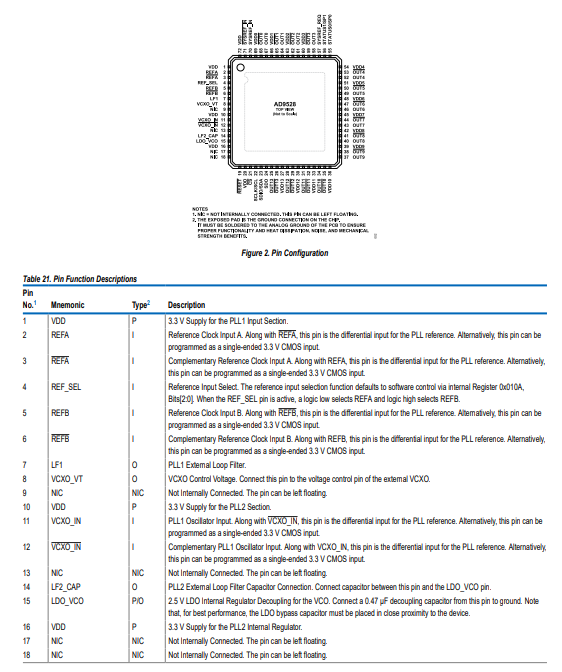

引腳配置描述

典型應用電路

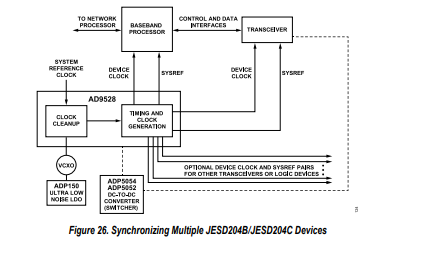

AD9258 能夠同步多個符合 JESD204B/JESD204C 標準(聯合電子設備工程委員會標準)的器件。圖 26 展示了 AD9258 同步系統參考時鐘的過程。AD9528 首先對系統參考時鐘進行凈化處理,然后在雙環模式下將其倍頻至更高頻率。AD9528 的時鐘分配功能用于為系統中所有周邊的 JESD204B/JESD204C 器件提供時鐘并使其同步。

器件初始化和校準流程圖

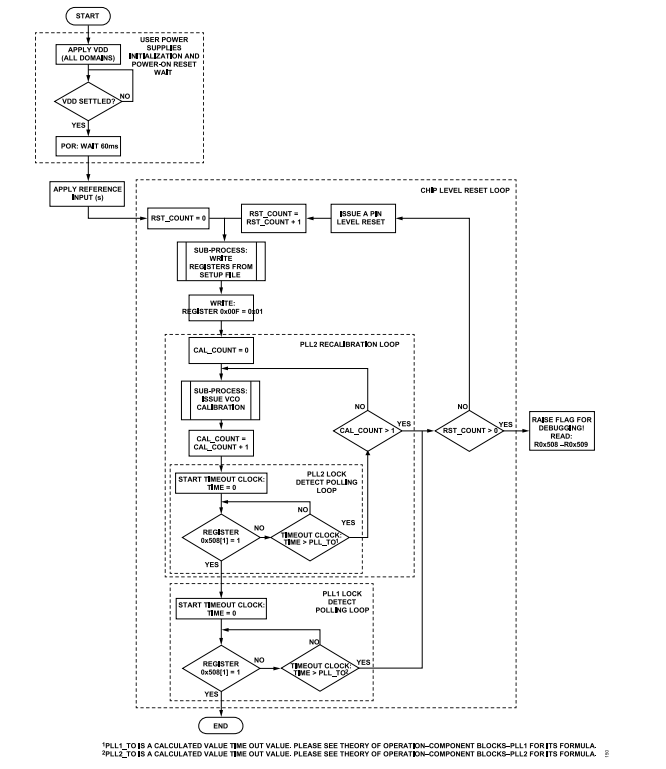

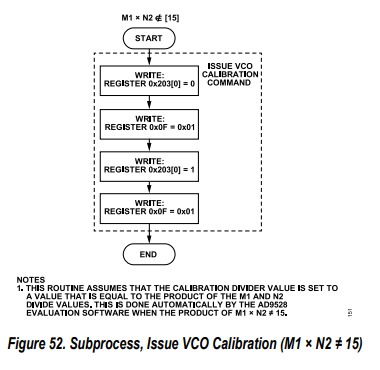

本節中的流程圖展示了使用評估軟件生成的設置文件(.stp)時,AD9528 典型的初始化例程,以及為實現穩健的系統啟動而設計的校準例程。

圖 51、圖 52、圖 53 和圖 54 假定以下條件:壓控振蕩器(VCO)具有 ±100 ppm 的拉偏范圍,且使用設置文件進行可靠的頻率轉換。這些流程圖并非無限循環,芯片級復位循環的計數變量(RST_COUNT)和 PLL2 重新校準循環的計數變量(CAL_COUNT)是用于為循環設置計數上限的計數變量,這些變量僅適用于初始化過程。

-

pll

+關注

關注

6文章

881瀏覽量

136041 -

時鐘發生器

+關注

關注

1文章

223瀏覽量

68868 -

ad9528

+關注

關注

1文章

4瀏覽量

2909

發布評論請先 登錄

AD9680 JESD204B接口的不穩定會導致較大的電流波動,怎么解決?

JESD204B的系統級優勢

串行LVDS和JESD204B的對比

JESD204標準解析

JESD204C的標準和新變化

JESD204B協議介紹

JESD204B時鐘發生器14輸出ad9528數據表LVDS技術

LTC6952:超低抖動、4.5 GHz PLL,帶11個輸出和JESD204B/JESD204C支持數據表

AD9207: 12-Bit, 6 GSPS, JESD204B/JESD204C Dual ADC Data Sheet AD9207: 12-Bit, 6 GSPS, JESD204B/JESD204C Dual ADC Data Sheet

從JESD204B升級到JESD204C時的系統設計注意事項

LTC6953具有11個輸出并支持JESD204B/JESD204C協議的超低抖動、4.5GHz時鐘分配器技術手冊

AD9528提供14路LVDS/HSTL輸出的JESD204B/JESD204C時鐘發生器技術手冊

AD9528提供14路LVDS/HSTL輸出的JESD204B/JESD204C時鐘發生器技術手冊

評論