資料介紹

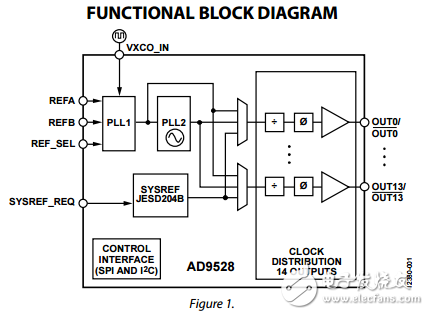

The AD9528 is a two-stage PLL with an integrated JESD204B SYSREF generator for multiple device synchronization. The first stage phase-locked loop (PLL) (PLL1) provides input reference conditioning by reducing the jitter present on a system clock. The second stage PLL (PLL2) provides high frequency clocks that achieve low integrated jitter as well as low broadband noise from the clock output drivers. The external VCXO provides the low noise reference required by PLL2 to achieve the restrictive phase noise and jitter requirements necessary to achieve acceptable performance. The on-chip VCO tunes from 3.450 GHz to 4.025 GHz. The integrated SYSREF generator outputs single shot, N-shot, or continuous signals synchronous to the PLL1 and PLL2 outputs to time align multiple devices. The AD9528 generates two outputs (Output 1 and Output 2) with a maximum frequency of 1.25 GHz, and 12 outputs up to 1 GHz. Each output can be configured to output directly from PLL1, PLL2, or the internal SYSREF generator. Each of the 14 output channels contains a divider with coarse digital phase adjustment and an analog fine phase delay block that allows complete flexibility in timing alignment across all 14 outputs. The AD9528 can also be used as a dual input flexible buffer to distribute 14 device clock and/or SYSREF signals. At power-up, the AD9528 sends the VCXO signal directly to Output 12 and Output 13 to serve as the power-up ready clocks. Note that, throughout this data sheet, the dual function pin names are referenced by the relevant function where applicable.

- 采用JESD204B的LMK5C33216超低抖動時鐘同步器數據表

- LMK0482x超低噪聲JESD204B兼容時鐘抖動消除器數據表

- 理解JESD204B協議

- AD9250:14位、170 MSPS/250 MSPS、JESD204B、雙模數轉換器數據表

- LTC2123:帶JESD204B串行輸出的雙14位250 Msps ADC數據表

- AD9694:14位、500 MSPS、JESD204B、四路模數轉換器數據表

- LTC6953:超低抖動、4.5 GHz時鐘分配器,帶11個輸出和JESD204B/JESD204C支持數據表

- AD9697:14位,1300 MSPS,JESD204B,模擬到數字轉換器數據Sheet

- AD9528:具有14個LVDS/HSTL輸出的JESD204B時鐘發生器數據表

- LTC2122:帶JESD204B串行輸出的雙14位170 Msps ADC數據表

- 集成2.2 GHz VCO數據表的AD9522-2:12 LVDS/24 CMOS輸出時鐘發生器

- AD9522-5:12 LVDS/24 CMOS輸出時鐘發生器數據表

- AD9516-5:14-輸出時鐘發生器數據表

- LTC6952:超低抖動、4.5 GHz PLL,帶11個輸出和JESD204B/JESD204C支持數據表

- AD9675:采用JESD204B的八進制超聲波AFE數據表

- 抓住JESD204B接口功能的關鍵問題 1251次閱讀

- SC6301低功耗超低噪聲時鐘抖動消除器簡介 1081次閱讀

- 采用系統參考模式設計JESD 204B時鐘 1562次閱讀

- 在賽靈思FPGA上快速實現JESD204B 4582次閱讀

- JESD204B學習手冊 2633次閱讀

- JESD204B與串行LVDS接口在寬帶數據轉換器應用中的考慮因素 1539次閱讀

- 在串行LVDS和JESD204B接口之間選擇 1579次閱讀

- 寬帶數據轉換器應用的JESD204B與串行LVDS接口考量 1450次閱讀

- 什么是JESD204B標準為什么需要關注JESD204B接口 1.3w次閱讀

- 為便于實現如此龐大的吞吐量,JESD204B標準應運而生 4709次閱讀

- 針對高速數據轉換器的最新高速JESD204B標準帶來了驗證挑戰 3160次閱讀

- JESD204B接口及協議狀態過程 3131次閱讀

- JESD204B標準及演進歷程 1.4w次閱讀

- 采用系統參考模式設計JESD204B時鐘 3196次閱讀

- JESD204B SystemC module 設計簡介(一) 3266次閱讀

下載排行

本周

- 1TC358743XBG評估板參考手冊

- 1.36 MB | 330次下載 | 免費

- 2開關電源基礎知識

- 5.73 MB | 6次下載 | 免費

- 3100W短波放大電路圖

- 0.05 MB | 4次下載 | 3 積分

- 4嵌入式linux-聊天程序設計

- 0.60 MB | 3次下載 | 免費

- 5基于FPGA的光纖通信系統的設計與實現

- 0.61 MB | 2次下載 | 免費

- 651單片機窗簾控制器仿真程序

- 1.93 MB | 2次下載 | 免費

- 751單片機大棚環境控制器仿真程序

- 1.10 MB | 2次下載 | 免費

- 8基于51單片機的RGB調色燈程序仿真

- 0.86 MB | 2次下載 | 免費

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費

- 2555集成電路應用800例(新編版)

- 0.00 MB | 33564次下載 | 免費

- 3接口電路圖大全

- 未知 | 30323次下載 | 免費

- 4開關電源設計實例指南

- 未知 | 21549次下載 | 免費

- 5電氣工程師手冊免費下載(新編第二版pdf電子書)

- 0.00 MB | 15349次下載 | 免費

- 6數字電路基礎pdf(下載)

- 未知 | 13750次下載 | 免費

- 7電子制作實例集錦 下載

- 未知 | 8113次下載 | 免費

- 8《LED驅動電路設計》 溫德爾著

- 0.00 MB | 6653次下載 | 免費

總榜

- 1matlab軟件下載入口

- 未知 | 935054次下載 | 免費

- 2protel99se軟件下載(可英文版轉中文版)

- 78.1 MB | 537796次下載 | 免費

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420026次下載 | 免費

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費

- 5Altium DXP2002下載入口

- 未知 | 233046次下載 | 免費

- 6電路仿真軟件multisim 10.0免費下載

- 340992 | 191185次下載 | 免費

- 7十天學會AVR單片機與C語言視頻教程 下載

- 158M | 183279次下載 | 免費

- 8proe5.0野火版下載(中文版免費下載)

- 未知 | 138040次下載 | 免費

電子發燒友App

電子發燒友App

創作

創作 發文章

發文章 發帖

發帖  提問

提問  發資料

發資料 發視頻

發視頻 上傳資料賺積分

上傳資料賺積分

評論