JESD204B接口一般用在高速的AD和DA芯片上,用于傳輸采集到的數(shù)據(jù)。該接口相比LVDS可以減少大量的IO管腳,所以正在逐步取代LVDS接口(引用wp446-jesd204b.pdf)。

Xilinx提供了JESD204B對應(yīng)的IP和相應(yīng)的phy。本文主要介紹xilinx-JESD204B的使用方法,基本上都是從pg066手冊得到的總結(jié),但也有自己的一些心得。

JESD204有很多的分支,包括A,B,C等,主要的區(qū)別是支持的速率不同。最早的JESD版本不支持精確的延時(shí),后來版本不斷升級,現(xiàn)在使用JESD204協(xié)議通過使用sysref和sync達(dá)到了精準(zhǔn)延時(shí)的效果,畢竟現(xiàn)在的速率達(dá)到幾十G,沒有精確的延時(shí)不能達(dá)到具體的設(shè)計(jì)要求。JESD204B的subclass0是沒有精準(zhǔn)延時(shí)的,subclass1使用sysref,subclass2使用sync。由于有了精準(zhǔn)的要求,所以對sysref和sync的時(shí)序要求很高。

言歸正傳,使用xilinx的JESD204B IP核,最簡單的方式是通過使用example design開始,并且pg066中也是這么建議的,為什么?第一是簡單,官方已經(jīng)提供給了一個(gè)教程,自己照貓畫虎就行了;最重要的是,單獨(dú)的JESD204B IP核一般不能使用,需要有對應(yīng)的PHY,因此如果不使用example design,自己就得再例化一個(gè)JESD204 PHY的IP,所以使用example design方便了很多,所以這種方法最簡單。

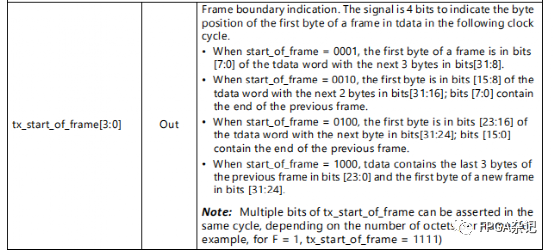

這個(gè)IP的接口比較簡單,查看pg066基本都能了解是干什么用的,我只介紹一下tx_start_of_frame這個(gè)信號。手冊對這個(gè)信號的介紹如下圖所示:

我重點(diǎn)關(guān)注 Note 部分,這部分的意思是說tx_start_of_frame信號會根據(jù)每幀包含的字節(jié)個(gè)數(shù)而使多個(gè)bit置位,并舉例說明:當(dāng)F=1(F表示的每幀包含的字節(jié)個(gè)數(shù))時(shí),tx_start_of_frame信號為4’b1111。同樣的在仿真example design時(shí),testbeach中F=2,查看波形可以看到tx_start_of_frame為4’b0101。但為什么會出現(xiàn)多bit 置 1 呢?這是因?yàn)榘l(fā)送數(shù)據(jù)tx_data的位寬為32bit,而當(dāng)F很小時(shí),tx_data的32bit數(shù)據(jù)中包含多個(gè)數(shù)據(jù)幀,所以導(dǎo)致tx_start_of_frame信號的多bit置 1 。即當(dāng)F=1時(shí),表示一幀數(shù)據(jù)只有一個(gè)字節(jié),所以tx_data(32bit)中包含4個(gè)數(shù)據(jù)幀,而每個(gè)字節(jié)都是起始位,所以tx_start_of_frame為4’b1111;同理,當(dāng)F=2時(shí),表示一幀數(shù)據(jù)包含兩個(gè)字節(jié),所以tx_data包含2個(gè)數(shù)據(jù)幀,起始位置在第1和第3字節(jié),所以tx_start_of_frame為4’b0101。而F為較小時(shí)比較常見,尤其是在AD采集芯片中,因?yàn)锳D芯片輸出的有效數(shù)據(jù)的位寬通常為8、12、14,轉(zhuǎn)換之后的F值就是1或者2。

PS:看到了一個(gè)好的博客,附上鏈接,不知道讓不讓轉(zhuǎn)發(fā),在博客中沒有看到禁止項(xiàng),有問題請及時(shí)聯(lián)系我。https://blog.csdn.net/weixin_41974812/article/details/117220777

審核編輯:湯梓紅

-

接口

+關(guān)注

關(guān)注

33文章

8941瀏覽量

153197 -

Xilinx

+關(guān)注

關(guān)注

73文章

2182瀏覽量

124342 -

lvds

+關(guān)注

關(guān)注

2文章

1111瀏覽量

67079 -

JESD204B

+關(guān)注

關(guān)注

6文章

82瀏覽量

19507

原文標(biāo)題:JESD204B學(xué)習(xí)手冊

文章出處:【微信號:FPGA雜記,微信公眾號:FPGA雜記】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

JESD204B的系統(tǒng)級優(yōu)勢

JESD204B串行接口時(shí)鐘的優(yōu)勢

如何讓JESD204B在FPGA上工作?FPGA對于JESD204B需要多少速度?

如何去實(shí)現(xiàn)JESD204B時(shí)鐘?

如何采用系統(tǒng)參考模式設(shè)計(jì)JESD204B時(shí)鐘

JESD204B協(xié)議介紹

JESD204B的優(yōu)勢

JESD204B SystemC module 設(shè)計(jì)簡介(一)

JESD204B標(biāo)準(zhǔn)及演進(jìn)歷程

JESD204B使用說明

JESD204B學(xué)習(xí)手冊

JESD204B學(xué)習(xí)手冊

評論