鎖相環整數分頻和小數分頻的區別是什么?

鎖相環(PLL)是一種常用的電子電路,用于將輸入的時鐘信號與參考信號進行同步,并生成輸出信號的一種技術。在PLL中,分頻器模塊起到關鍵作用,可以實現整數分頻和小數分頻兩種方式。本文將詳細探討整數分頻和小數分頻的區別。

一、整數分頻

整數分頻是指將輸入信號的周期或頻率直接除以整數N,生成一個輸出信號。整數N通常是一個大于1的正整數。整數分頻的主要特點如下:

1. 簡單可靠:整數分頻的計算和處理都是基于整數,不需要進行復雜的計算和操作。這種簡單性使整數分頻的電路設計相對容易,且其性能較為穩定和可靠。

2. 效果明顯:整數分頻可以將輸入信號的頻率顯著降低或提高,達到適配不同應用的要求。例如,將輸入信號的頻率降低后,可以用于減小電路功耗、改善噪聲特性等。

3. 輸出穩定:整數分頻的輸出信號的頻率是輸入信號頻率的商,因此其輸出頻率在理論上是穩定的。這種穩定性使得整數分頻在某些對頻率要求較高的應用中非常實用,例如通信系統、音頻處理等。

4. 頻率選擇受限:由于整數分頻只能將頻率進行整數倍的變化,因此其輸出信號的頻率選擇性受到限制。當輸入信號的頻率與所需輸出頻率的整數倍存在較大差距時,整數分頻不能滿足要求。

二、小數分頻

小數分頻是指將輸入信號的周期或頻率按照一個小數分頻因子進行分頻,生成一個非整數倍的輸出信號。小數分頻的主要特點如下:

1. 精確靈活:小數分頻可以實現更加精確、靈活的頻率變換。分頻因子中的小數部分可以實現相當精細的調整,使得輸出頻率能夠準確地適配所需應用。

2. 高頻選擇范圍廣:小數分頻可以實現更大范圍的頻率變化。通過合適的分頻因子,輸入信號的頻率可以在很大的范圍內進行升高或降低,提供了更多應用場景的選擇。

3. 擴大倍頻系數:小數分頻可以將輸入信號的頻率擴大至更高的倍頻,以滿足高頻應用的需求。這在一些射頻通信、雷達等系統中非常重要。

4. 計算復雜度高:小數分頻需要進行復雜的計算和操作,包括除法和乘法等運算。這要求設計和實現小數分頻的電路存在一定的挑戰,更高的計算復雜度可能導致功耗增加。

三、整數分頻和小數分頻的應用差異

整數分頻和小數分頻由于其不同的特點,適用于不同的應用場景:

1. 整數分頻在一些對頻率要求非常高的應用中得到廣泛應用,例如通信系統、音頻處理等。整數分頻能夠提供穩定、可靠的頻率轉換,且操作簡單,適合于周期性精確信號的處理。

2. 小數分頻則更適用于那些需要頻率靈活精確調整的應用,例如射頻通信系統、調頻廣播、音視頻處理等。小數分頻可以提供更大范圍的頻率變換和擴大倍頻系數的功能,可以實現更加精細的頻率調整。

綜上所述,整數分頻和小數分頻是鎖相環中常用的兩種分頻方式,它們在處理頻率轉換和信號同步的過程中具有各自的特點和應用場景。

-

鎖相環

+關注

關注

35文章

593瀏覽量

88462 -

小數分頻

+關注

關注

0文章

7瀏覽量

6723 -

時鐘信號

+關注

關注

4文章

465瀏覽量

29074

發布評論請先 登錄

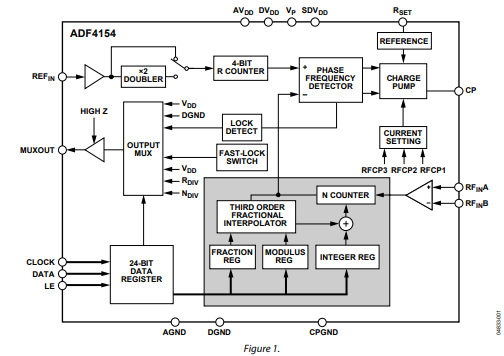

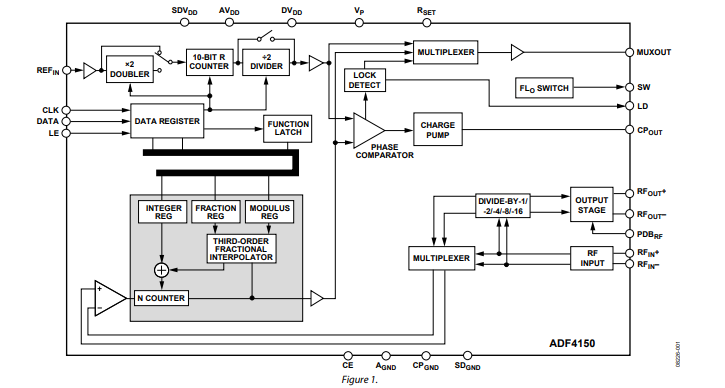

Analog Devices Inc. ADF4382x小數N分頻鎖相環 (PLL)數據手冊

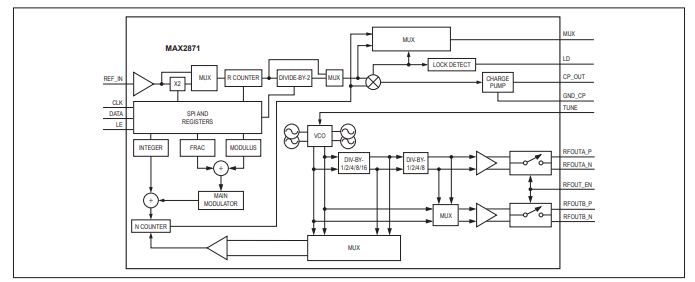

MAX2871 23.5MHz至6000MHz小數/整數N分頻頻率合成器/VCO技術手冊

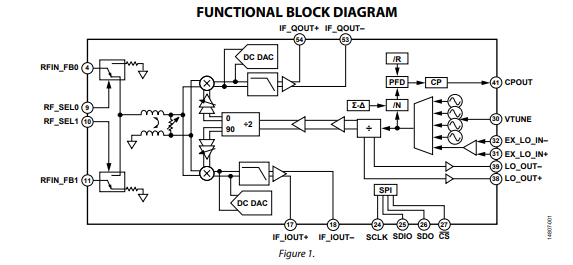

ADRF6821 450MHz到2800MHz,具有集成式小數分頻PLL和VCO的DPD RFIC技術手冊

請問頻率合成器像LMX2594,LMX2595,LMX2694這類芯片的同步功能是都需要在整數分頻模式下才能同步嗎?

請問LMX2694-EP輸出信號中有小數分頻雜散該如何解決?

CDCM6208V2G具有小數分頻器的2:8時鐘發生器/抖動消除器數據表

CDCM6208V1F具有小數分頻器的2:8時鐘生成器/抖動消除器數據表

具有小數分頻器的CDCM6208 2:8時鐘生成器/抖動消除器數據表

鎖相環整數分頻和小數分頻的區別是什么?

鎖相環整數分頻和小數分頻的區別是什么?

評論