概述

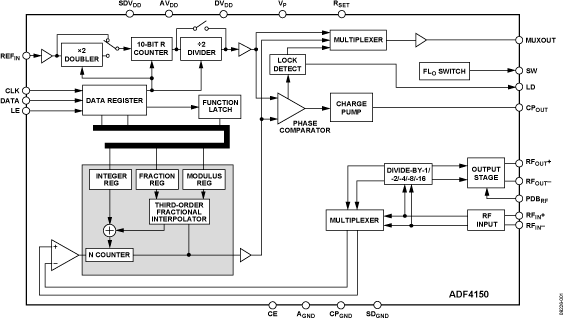

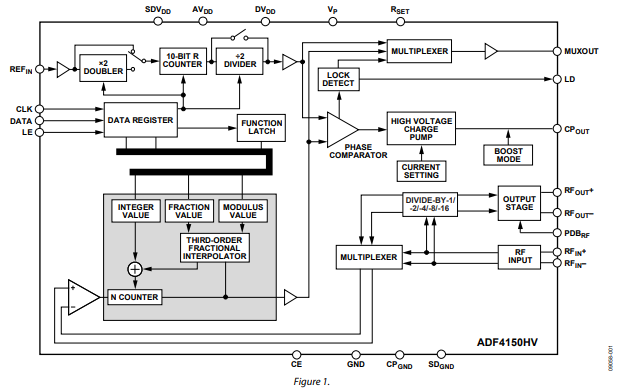

ADF4150結合外部電壓控制振蕩器(VCO)、環路濾波器和外部基準頻率使用時,可實現小數N分頻或整數N分頻鎖相環(PLL)頻率合成器。

它能夠與外部VCO器件配合使用,且與ADF4350軟件兼容。VCO頻率可進行1/2/4/8或16分頻,因此用戶可以產生低至31.25 MHz的RF輸出頻率。對于要求隔離的應用,RF輸出級可以實現靜音。靜音功能既可以通過引腳控制,也可以通過軟件控制。

所有片內寄存器均通過簡單的三線式接口進行控制。該器件采用3.0 V至3.6 V電源供電,不用時可以關斷。

ADF4150采用4 mm × 4 mm封裝。

數據表:*附件:ADF4150小數N 整數N分頻PLL頻率合成器技術手冊.pdf

應用

特性

- 小數N分頻頻率合成器和整數N分頻頻率合成器

- 可編程1/2/4/8/16分頻輸出

- 5.0 GHz RF帶寬

- 3.0 V至3.6 V電源供電

- 1.8 V邏輯兼容

- 獨立的電荷泵電源 (V

P) 可在3 V系統中提供擴展的調諧電壓 - 可編程雙模預分頻器:4/5或8/9

- 可編程輸出功率水平

- RF輸出靜音功能

- 三線式串行接口

- 模擬和數字鎖定檢測

- 開關帶寬快速鎖定模式

- 周跳減少

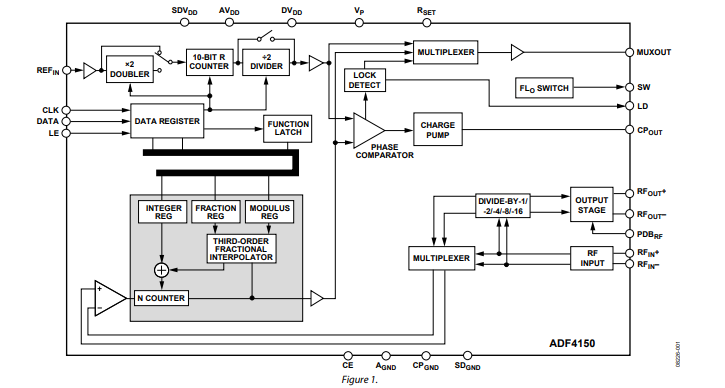

框圖

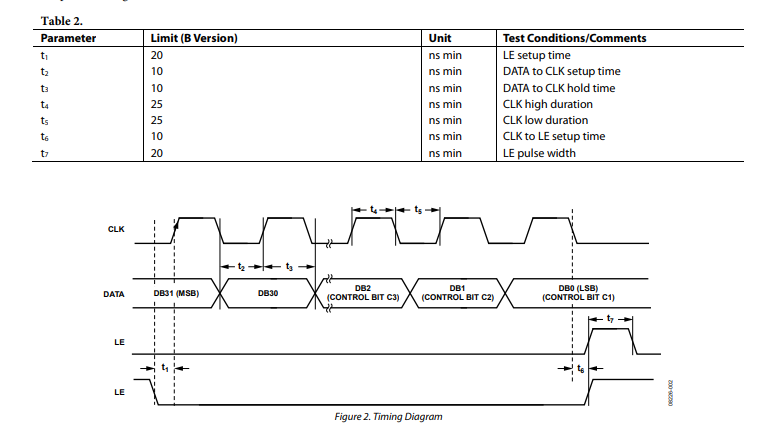

時序特征

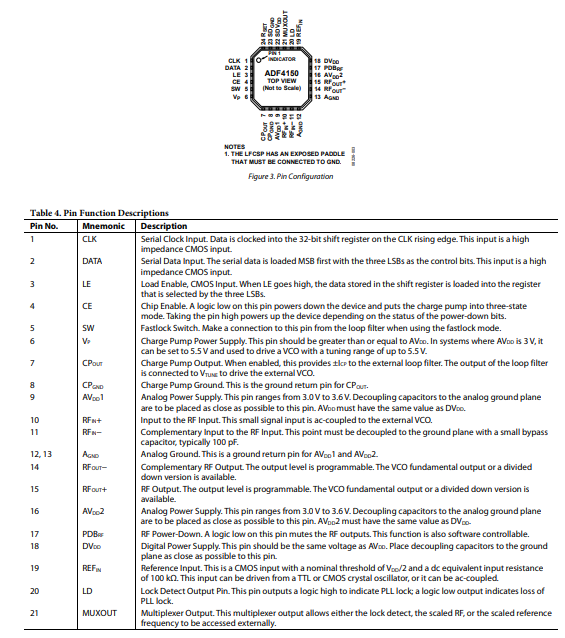

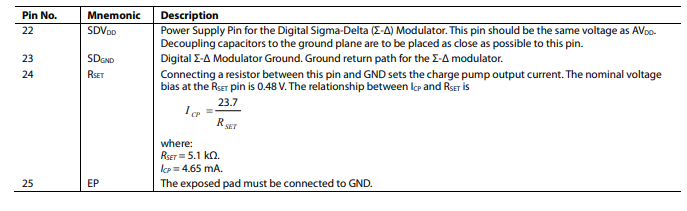

引腳配置描述

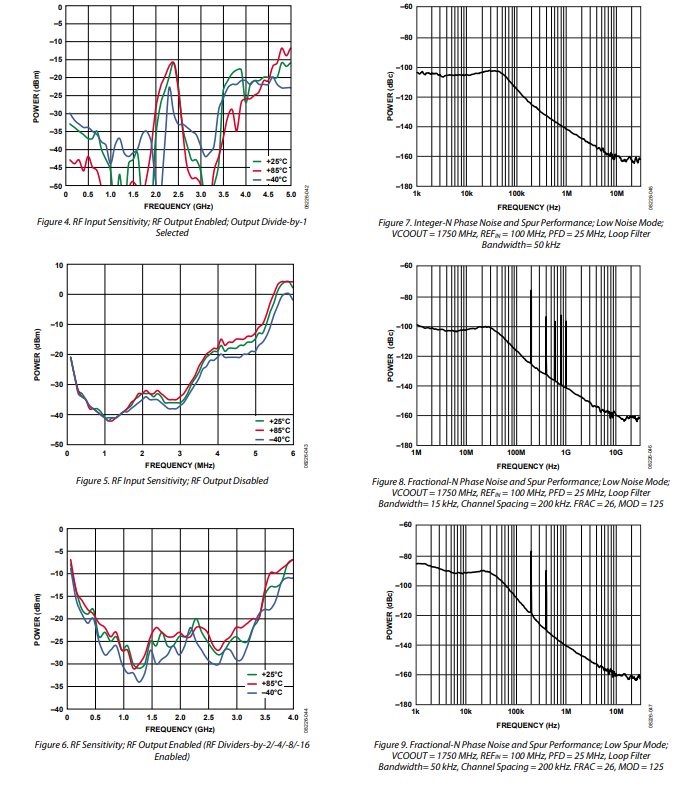

典型性能特征

電路描述

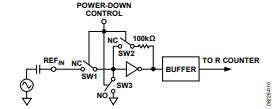

參考輸入部分

參考輸入級如圖14所示。SW1和SW2通常是閉合的開關,SW3通常是斷開的開關。當啟動掉電模式時,SW3閉合,SW1和SW2斷開。這確保了在掉電期間**REF_{IN}**引腳不會有負載。

圖14. 參考輸入級

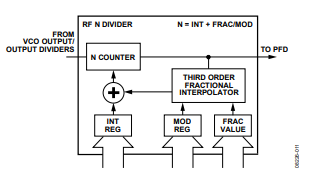

射頻N分頻器

射頻N分頻器可在鎖相環(PLL)反饋路徑中實現分頻比。該分頻比由INT、FRAC和MOD值決定。

圖15. 射頻整數分頻器

INT、FRAC、MOD和R計數器關系

INT、FRAC和MOD值與R計數器配合,能夠生成間隔為鑒頻鑒相器(PFD)頻率分數倍的輸出頻率。更多信息請參見“射頻合成器——實例”部分。

射頻壓控振蕩器(VCO)頻率(RF_{OUT})公式為:

[ RF_{OUT}=f_{PFD}times(INT+(FRAC/MOD)) ] (1)

其中:

- **RF_{OUT}**是外部壓控振蕩器(VCO)的輸出頻率。

- INT是16位二進制計數器的預設分頻比(對于4/5預分頻器,為23至32,767;對于8/9預分頻器,為75至65,535 )。

- FRAC是分數除法的分子(0至MOD - 1)。

- MOD是預設分數模數(2至4095 )。

PFD頻率(f_{PFD})公式為:

[ f_{PFD}=REF_{IN}timesfrac{(1 + D)}{(Rtimes(1 + T))} ] (2)

其中:

- **REF_{IN}**是參考輸入頻率。

- D是**REF_{IN}**倍頻位(0或1)。

- R是10位二進制可編程參考計數器的預設分頻比(1至1023 )。

- T是**REF_{IN}**二分頻位(0或1 )。

整數N模式

如果FRAC = 0且寄存器2中的DB8(LDF)位設為1,合成器將在整數N模式下運行。寄存器2中的DB8(LDF)位應設為1,以實現整數N模式下的數字鎖定檢測。此外,如果將抗鋸齒脈沖寬度減小到3ns,可實現更低的相位噪聲。此模式對分數N應用無效。

R計數器

10位R計數器可對輸入參考頻率(REF_{IN})進行分頻,以產生PFD的參考時鐘。允許的分頻比范圍為1至1023。

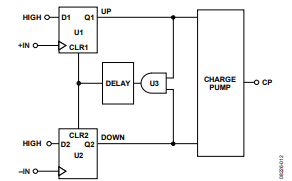

鑒頻鑒相器(PFD)和電荷泵

鑒頻鑒相器(PFD)對R計數器和N計數器進行計數,并輸出與兩個計數器之間的相位和頻率差成比例的信號。圖16是PFD的簡化示意圖。

圖16. PFD簡化示意圖

PFD包含一個可編程延遲元件,用于設置抗鋸齒脈沖的寬度。此脈沖可確保PFD轉換功能中不存在死區,并提供一致的參考雜散電平。

-

頻率合成器

+關注

關注

5文章

293瀏覽量

32695 -

pll

+關注

關注

6文章

880瀏覽量

136022 -

VCO

+關注

關注

13文章

311瀏覽量

69964

發布評論請先 登錄

ADF4150 小數N/整數N分頻PLL頻率合成器

ADF4150小數N/整數N分頻PLL頻率合成器技術手冊

ADF4150小數N/整數N分頻PLL頻率合成器技術手冊

評論