每隔三四年都會(huì)更新一個(gè)版本。到目前為止,已經(jīng)更新到了PCIe 6.0。 7月2日,PCI-SIG公布了最新的PCIe 6.0最新的草案0.71版本。與PCIe 5.0 相比,PCIe 6.0 再次實(shí)現(xiàn)了

2021-07-05 09:33:58 6088

6088 2019年年初,PCI-SIG組織對(duì)外發(fā)布PCIe 5.0 0.9版規(guī)范。隨后,2019年5月29日,PCI-SIG正式宣布完成PCIe 5.0規(guī)范,傳輸速率達(dá)到32GT/s,帶寬可達(dá)128GB/s

2021-09-29 08:48:07 5200

5200 ?/s?;到了剛發(fā)布的PCIe 6.0,實(shí)現(xiàn)了帶寬速率全面翻倍,而且PCIe?6.0對(duì)底層信令進(jìn)行了改進(jìn)。 是德科技剛剛發(fā)布了針對(duì)PCIe?5.0/6.0的完整測(cè)試方案,至此能夠提供全方位的物理層測(cè)試

2022-04-28 16:43:31 2054

2054

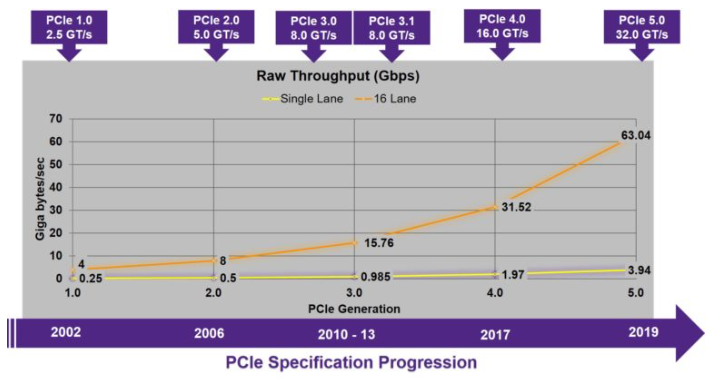

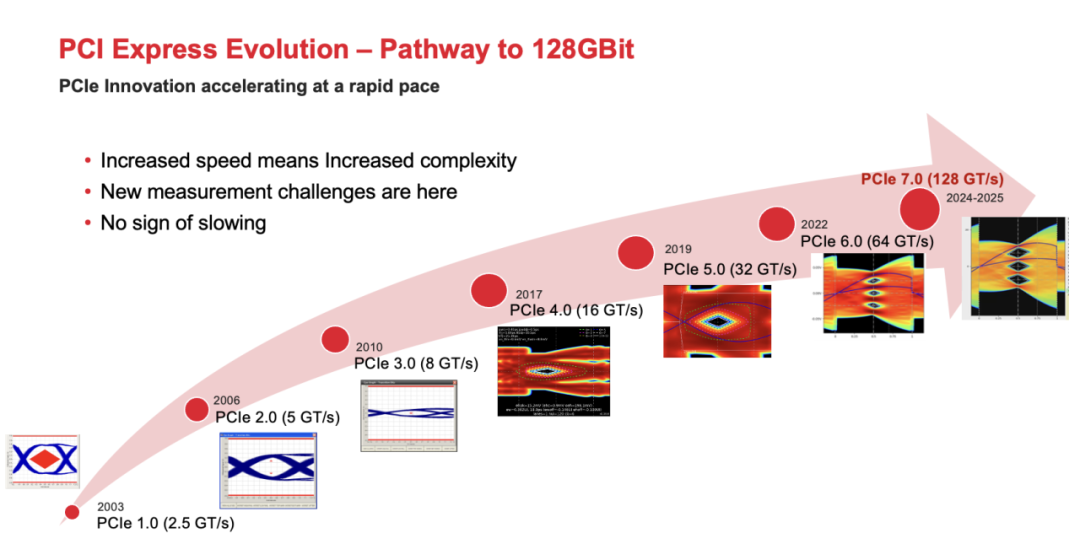

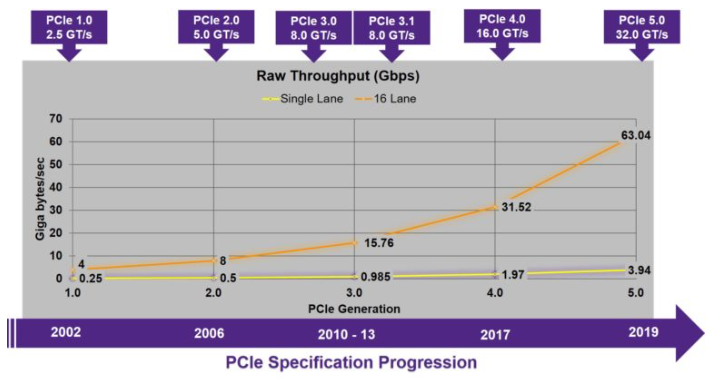

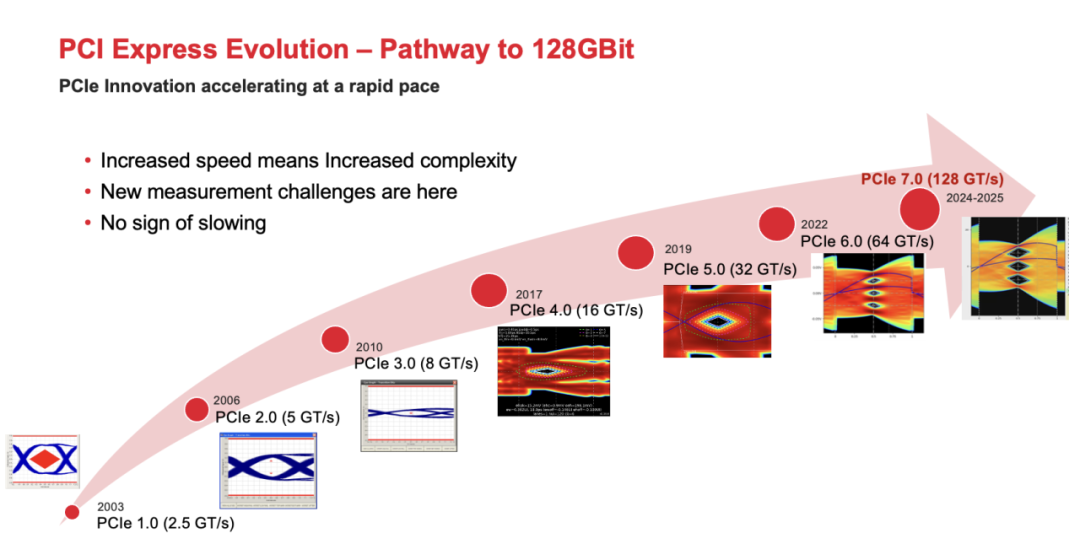

2010年,PCIe 3.0 將數(shù)據(jù)速率提高到了 8.0 GT/s ,并采用了新的 128b/130b 編碼機(jī)制,使每個(gè)引腳的帶寬比 PCIe 2.0 翻了一番。新的編碼機(jī)制通過(guò)采用三個(gè)隨機(jī)位翻轉(zhuǎn)檢測(cè)的故障模型確保了高可靠性

2023-01-04 11:17:04 11312

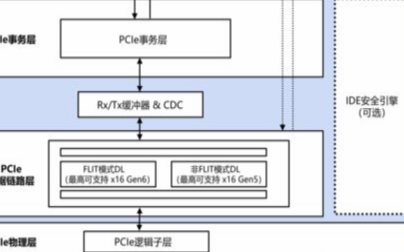

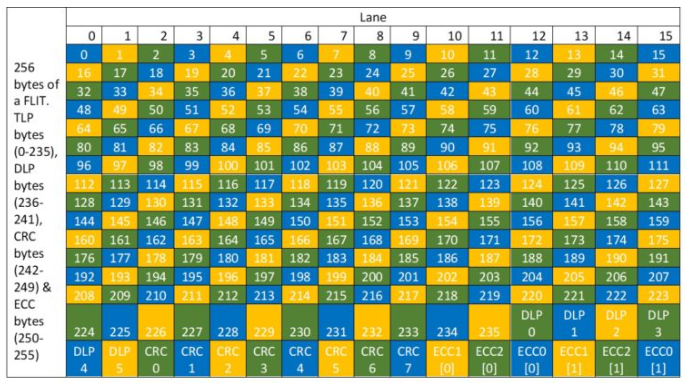

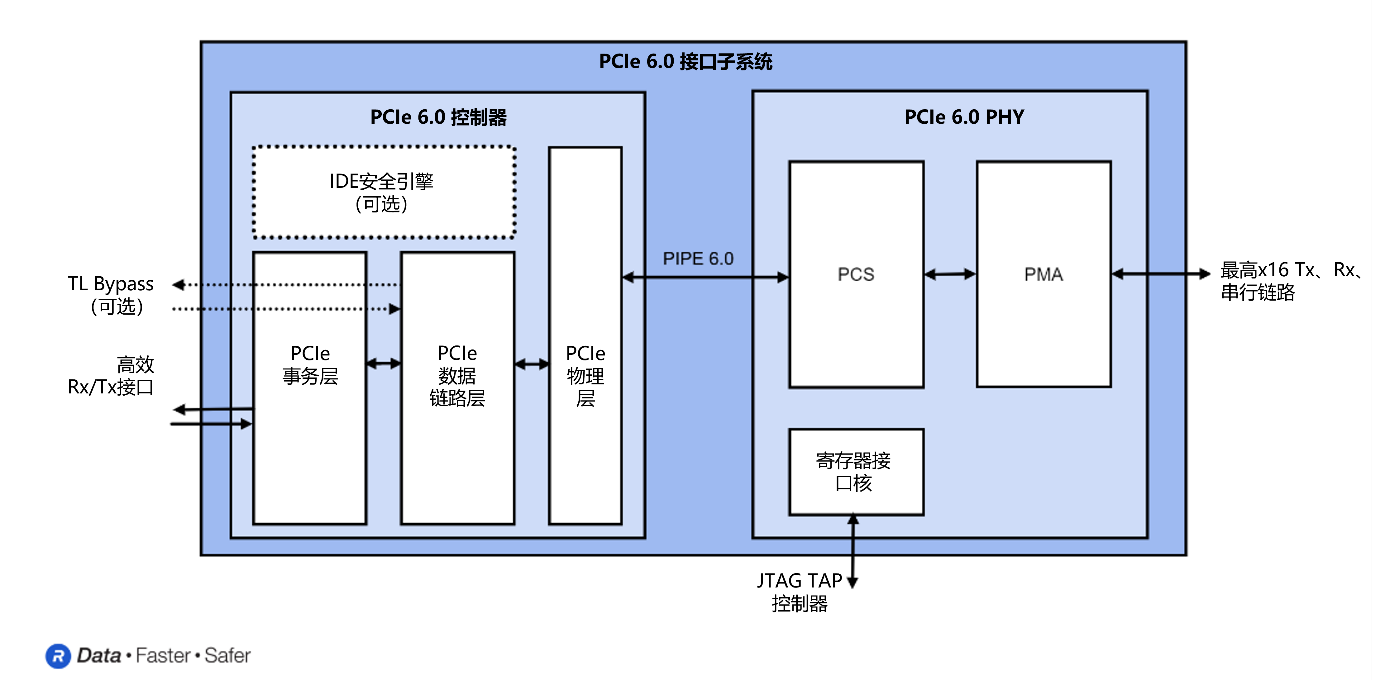

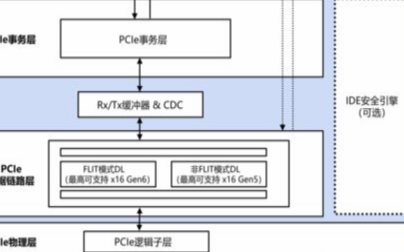

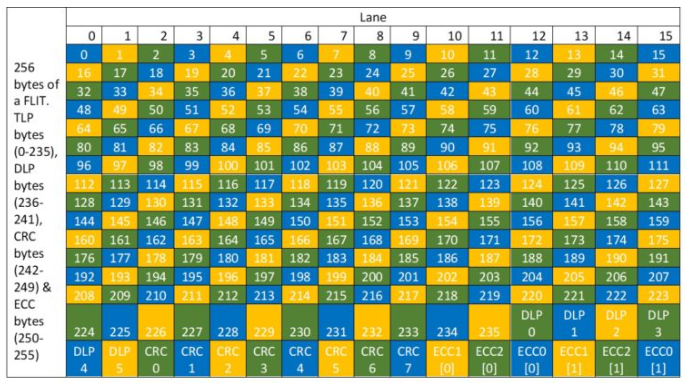

11312 PCIe 6.0 規(guī)范于 2021 年發(fā)布,采用 PAM4 調(diào)制(即 4 電平脈沖幅度調(diào)制),使數(shù)據(jù)傳輸速度翻倍,達(dá)到 64GT/s。同時(shí),PCIe 6.0 規(guī)范使用 FLIT(流量控制單元)作為新的數(shù)據(jù)傳輸單元,顯著提高了傳輸效率。

2025-02-27 15:44:34 734

734

隨著 PCIe 6.0 標(biāo)準(zhǔn)剛剛進(jìn)入市場(chǎng),PCI-SIG 組織已著手推動(dòng)下一代標(biāo)準(zhǔn)——PCIe 7.0,預(yù)計(jì)將在 2025 年正式發(fā)布,持該標(biāo)準(zhǔn)的設(shè)備預(yù)計(jì)將在 2026 年問(wèn)世,而大規(guī)模商用

2025-03-06 11:29:42 571

571

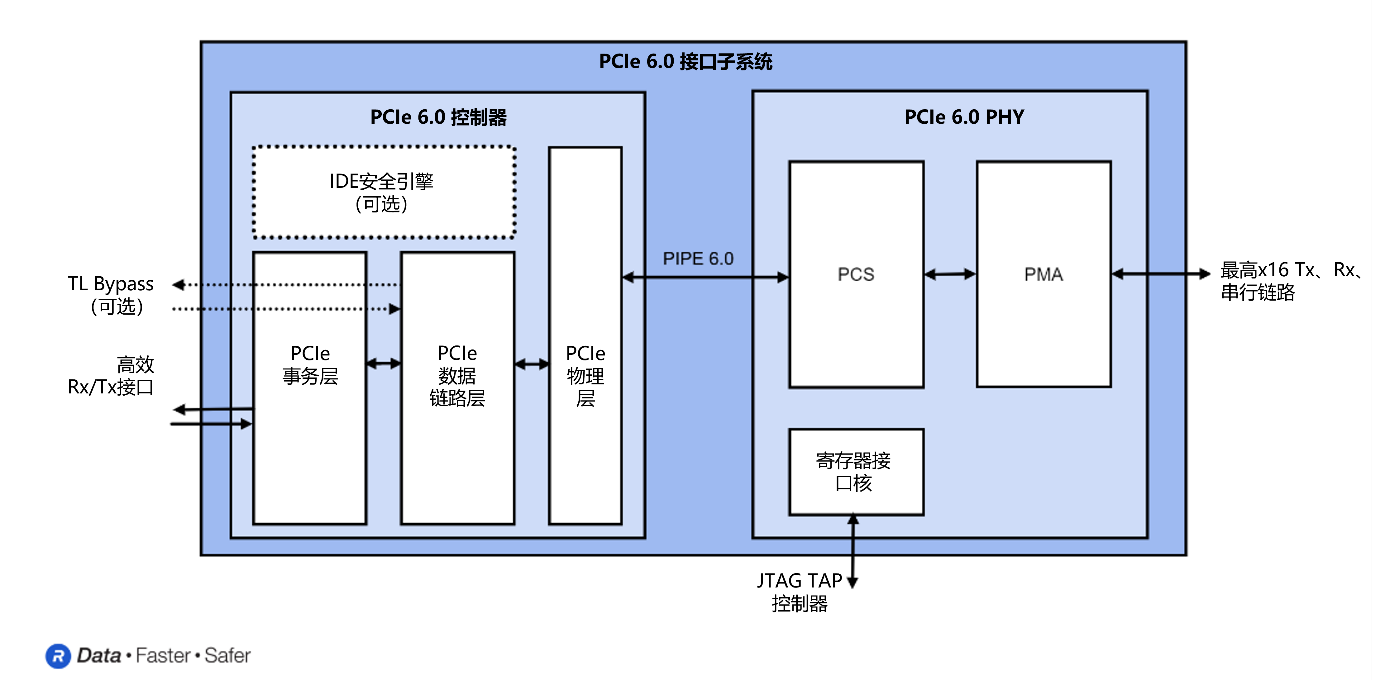

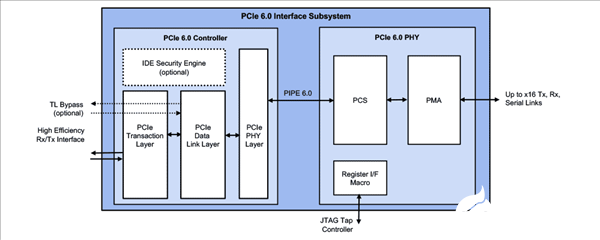

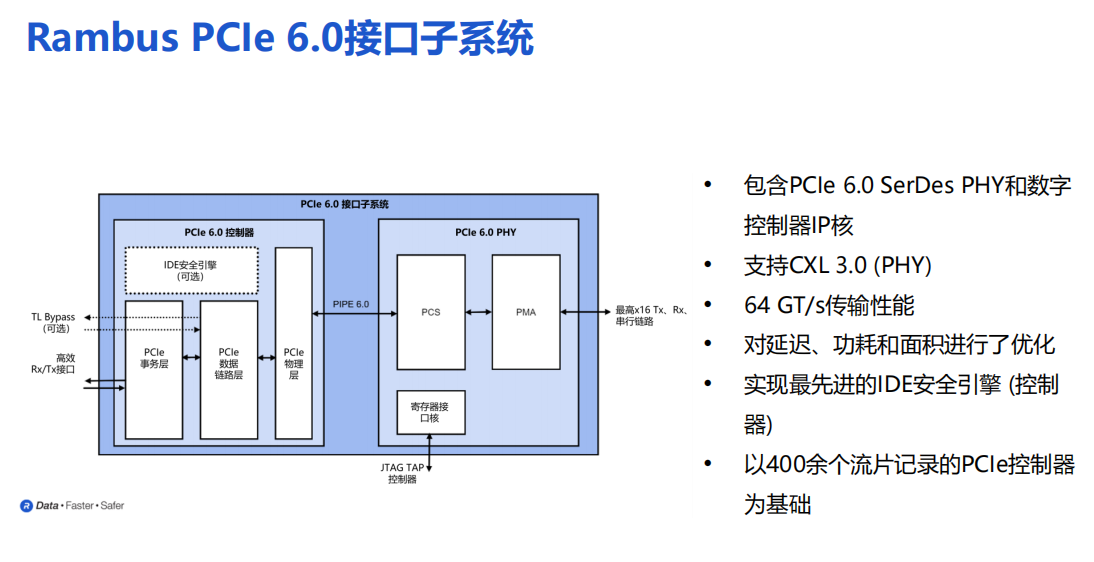

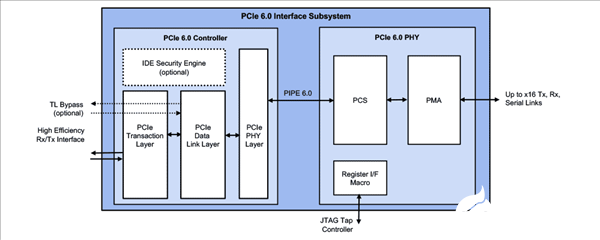

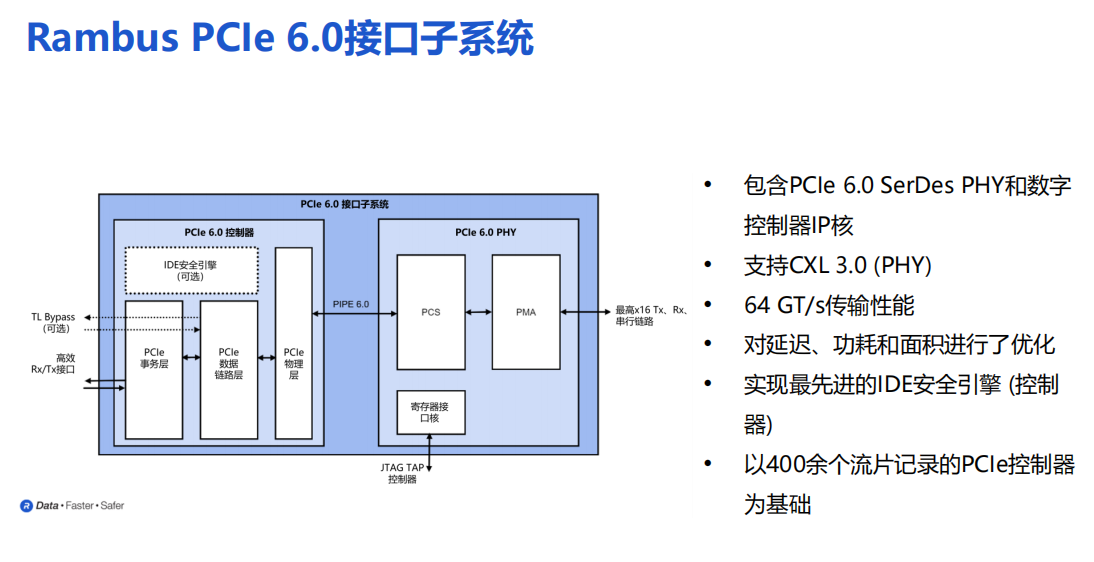

將高性能工作負(fù)載的數(shù)據(jù)傳輸速率提升至最高64 GT/s 支持PCIe 6.0的全功能,提供對(duì)CXL 3.0的PHY支持 對(duì)延遲、功耗和面積進(jìn)行優(yōu)化,提供完整的IP解決方案 提供最先進(jìn)的安全性,保護(hù)

2022-12-01 13:39:25 633

633

是PCIe問(wèn)世近20年來(lái),變化最大的一次。 根據(jù)PCI-SIG的介紹,PCIe 6.0主要有三大變化:數(shù)據(jù)傳輸速率從32GT/s翻倍至64GT/s;編碼方式從NRZ 信令模式轉(zhuǎn)向PAM4信令模式;從

2023-01-31 09:23:22 2465

2465 ,最新版本將PCIe??5.0規(guī)范的 數(shù)據(jù)速率提高了一倍 ,并保持了 向后的兼容性 。 最新的PCIe??6.0規(guī)范的主要特點(diǎn)包括: 01? 64 GT/s數(shù)據(jù)速率,通過(guò)x16配置可達(dá)到 256Gbps;

2023-05-11 10:30:39 1066

1066

電子發(fā)燒友網(wǎng)報(bào)道(文/周凱揚(yáng))2022年1月,PCI-SIG發(fā)布了PCIe 6.0規(guī)范,正式拉開(kāi)了接口帶寬大幅升級(jí)的序幕。然而,在規(guī)范公布的兩年時(shí)間里,也已經(jīng)更新了6.0.1和6.1版本,PCIe

2024-01-31 09:02:24 3018

3018 開(kāi)發(fā)環(huán)境:windows開(kāi)發(fā)平臺(tái):QT5.11.31、PCIE上位機(jī)測(cè)試過(guò)程FPGA將數(shù)據(jù)傳到芯片中,通過(guò)pcie再將芯片算完的數(shù)傳給上位機(jī)。目標(biāo):1.實(shí)現(xiàn)上位機(jī)的速度測(cè)試,經(jīng)測(cè)試pcie的傳輸速度

2022-01-13 16:44:54

的16GT/s數(shù)據(jù)速率,再到PCIe 5.0的32GT/x。PCI-SIG組織實(shí)現(xiàn)了在速率翻倍的同時(shí),仍能保持使用普通的FR4 板材 和廉價(jià)接插件,主要源自?xún)蓚€(gè)方面的改進(jìn),一是使用128b/130b編碼來(lái)

2020-11-25 06:19:43

了兩倍,達(dá)到32GT/s。這樣的性能提升對(duì)于AI/ML和數(shù)據(jù)中心來(lái)說(shuō)尤為重要,CPU、GPU、FPGA和ASIC加速器之間更快速地移動(dòng)數(shù)據(jù)成為了可能,而SSD作為存儲(chǔ)介質(zhì),同樣成了直接受益者。一如既往

2021-12-11 08:00:00

SSD的性能,特別是延遲的能力。相比PCIe閃存卡的形式,以往外置SSD要經(jīng)過(guò)SAS/SATA,延遲高,在性能上存在差距,因此在需要數(shù)據(jù)加速的應(yīng)用場(chǎng)景,如數(shù)據(jù)庫(kù)的OLTP應(yīng)用,PCIe閃存卡就成為了不二

2019-06-24 05:00:55

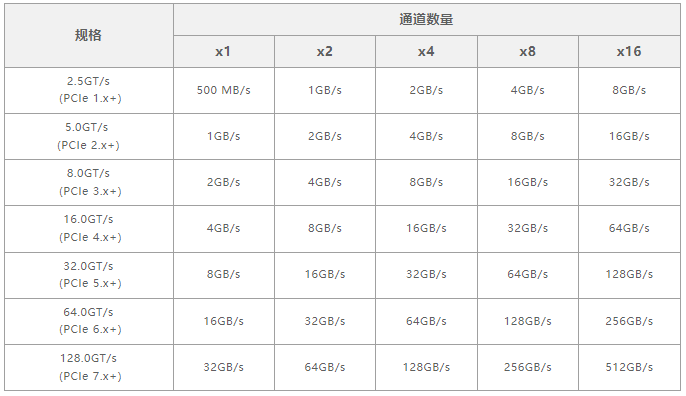

,x4,x8,x16和x32的連接寬度。每個(gè)LAN的原始數(shù)據(jù)傳輸速率是2.5Gbps @ 1.25GHz。

2019-06-03 07:09:56

上的速率接近 1.25Gb/s,這種 8 通道(x8)PCIe 總線的誕生恰逢其時(shí)。 第一代 PCIe x8 總線在每個(gè)方向上的速率為 2GB。當(dāng)時(shí) 16 通道( x16 )的插槽尚未問(wèn)世,服務(wù)器主板一般

2021-01-07 17:31:57

具有 16 G 每秒傳輸 (GT/s) 的比特率。第 4 代的規(guī)范預(yù)計(jì)將在 2014 或 2015 年發(fā)布。表 1:各代 PCIe 的數(shù)據(jù)吞吐量隨著數(shù)據(jù)速率的提升,參考時(shí)鐘需求也在不斷提高。本文將重點(diǎn)

2018-09-17 16:12:25

= 2500MT/s = ( 2500 / 10 ) MB/s

PCIe gen3 x1 傳輸速率 8GT/s = 8000MT/s = ( 8000 / 130 ) x ( 128/8 ) MB/s

2023-11-02 09:31:28

%。 五、散熱系統(tǒng) 采用無(wú)風(fēng)扇被動(dòng)式散熱。 六、應(yīng)用領(lǐng)域 FPGA硬件加速。 七、接口測(cè)試軟件DDR4 數(shù)據(jù)速率2400Mb/s IP測(cè)試。 PCIe 3.0 x8 IP測(cè)試。 程序加載測(cè)試。

2019-10-25 16:00:50

不同系列的PCIE IP并不通用,不同的系列都需要安裝不同的PCIE IP包。

(3)參數(shù)配置,PCIE 的gen1是2.5GT/s,gen2是5GT/s,芯片集成的是gen2的硬核,所以選5GT/s

2023-11-17 14:35:30

to Host)的全雙工數(shù)據(jù)傳輸6.自適應(yīng)PCIe鏈路速率:PCIe 1.0,PCIe 2.0,PCIe3.0和PCIe 4.0和寬度:PCIe x1,PCIe x2,PCIe x4,PCIex8

2020-11-25 22:27:25

散熱。六、應(yīng)用領(lǐng)域FPGA硬件加速。七、接口測(cè)試軟件DDR4 數(shù)據(jù)速率2400Mb/s IP測(cè)試。PCIe 3.0 x8 IP測(cè)試。程序加載測(cè)試。北京太速科技有限公司在線客服:QQ:448468544公司網(wǎng)站:www.orihard.com聯(lián)系電話:***

2018-07-27 16:49:30

。 支持PCIe x1、x4、x8模式。 支持2x72bit(數(shù)據(jù)位寬64bit+ECC)DDR4存儲(chǔ),數(shù)據(jù)傳輸速率2400Mb/s。 DDR4單簇容量4GB,總?cè)萘繛?GB。 板載4個(gè)用戶(hù)可編程LED

2018-08-22 17:31:55

(見(jiàn)表 1)。第 3 代 PCIe 引入了全新的編碼方案,其可在不增加數(shù)據(jù)速率一倍的情況下,將數(shù)據(jù)吞吐量提升一倍。PCI-SIG 近期宣布推出的第 4 代 PCIe 具有 16 G 每秒傳輸 (GT/s

2022-11-22 08:04:25

如何提高PCIe數(shù)據(jù)速率?

2021-05-20 06:17:09

嗨,我將從一個(gè)新項(xiàng)目開(kāi)始。它涉及使用FPGA和GP / GPU加速PCIe板,這些板將被添加到常規(guī)計(jì)算機(jī)或服務(wù)器中。 GPU將是NVIDIA特斯拉。 FPGA板......還有待選擇。我確實(shí)看到了

2019-01-24 10:55:48

傳輸速率是根據(jù)PCIE的協(xié)議制定的嗎?2.如果我設(shè)置的速率超過(guò)5.0Gbps可以嗎?是否會(huì)出現(xiàn)數(shù)據(jù)的傳輸錯(cuò)誤等現(xiàn)象?3.不太理解PCIE中關(guān)于x1和x2的含義,文檔說(shuō)PCIE是one single interface link,那么對(duì)于單個(gè)端口而言,x2的含義僅僅是代表速率是x1速率的一倍嗎?

2018-06-19 04:36:26

PCI Express是一種高性能互連協(xié)議,被廣泛應(yīng)用于網(wǎng)絡(luò)適配、圖形加速器、網(wǎng)絡(luò)存儲(chǔ)、大數(shù)據(jù)傳輸以及嵌入式系統(tǒng)等領(lǐng)域。文中介紹了PCIe的體系結(jié)構(gòu),以及利用Altera Cyclone IV GX

2019-05-21 09:12:26

PCIE 3.0相對(duì)于它的前一代PCIE 2.0的最主要的一個(gè)區(qū)別是速率由5GT/s提升到了8GT/s。為了保證數(shù)據(jù)傳輸密度和直流平衡以及時(shí)鐘恢復(fù),PCIE 2.0中使用了8B/10B編碼,即將每8位有效數(shù)據(jù)編碼為10位

2012-12-03 11:45:13 55

55 的可靠性傳輸,熱插拔以及服務(wù)質(zhì)量(QOS)等功能。目前PCIe規(guī)范已經(jīng)發(fā)布到3.0版本,并且在行業(yè)內(nèi)得到了廣泛采用,但是其功能特性還可以進(jìn)一步提升。PCIe 4.0規(guī)范將于2017年初發(fā)布,其總線帶寬是3.0版規(guī)范的2倍,數(shù)據(jù)傳輸速率將大幅提高,由8GTps增長(zhǎng)

2017-02-08 04:18:09 1126

1126 規(guī)范不斷演進(jìn),也成為存儲(chǔ)、云計(jì)算、移動(dòng)和汽車(chē)領(lǐng)域的主要設(shè)計(jì)規(guī)范。PCI-SIG在2011年11月發(fā)布最新PCIe 4.0 16 GT/s (Gen4) 規(guī)范,但早在兩年前,該機(jī)構(gòu)就已經(jīng)積極開(kāi)始這一工作

2017-11-15 19:57:01 10738

10738 歷史上,PCIe系統(tǒng)設(shè)計(jì)人員把通用低成本FR4 PCB材料和引線鍵合(wirebond)封裝用于 高達(dá) 8GT/s 數(shù) 據(jù) 速率(Gen3)的大多數(shù)應(yīng)用,這種做法已被證明是成功的。但是,在32GT/s的數(shù) 據(jù)速率下 使用 這 種材料 和封裝并不可行。

2018-05-04 16:13:34 7783

7783

去年10月底,PCIe 4.0標(biāo)準(zhǔn)正式誕生,傳輸速率翻番為16GT/s,x16規(guī)格可提供多達(dá)64GB/s的雙向帶寬。

2019-03-26 14:06:18 1250

1250 PCIe無(wú)疑是最為流行的傳輸總線標(biāo)準(zhǔn),這幾年的更新?lián)Q代也十分頻繁:PCIe 3.0目前還是最普及的,PCIe 4.0正在快速崛起,PCIe 5.0即將和大家見(jiàn)面,PCIe 6.0也正在快速推進(jìn)制定中。

2020-02-24 11:31:25 4883

4883

美國(guó)微芯(Microchip)發(fā)布了兩款 Retimer 芯片,特點(diǎn)是支持 PCIe 5.0 的 32GT/s 鏈接速率。兩款 XpressConnect 芯片的型號(hào)分別為 RTM-C 8xG5

2020-11-12 16:25:54 2608

2608 PCIe 4.0已經(jīng)逐漸普及,PCIe 5.0即將登場(chǎng),PCIe 6.0躍躍欲試……PCIe標(biāo)準(zhǔn)這幾年的步伐不可謂不快。

2021-02-05 11:36:32 3690

3690 電子發(fā)燒友網(wǎng)報(bào)道(文/吳子鵬)2019年年初,PCI-SIG組織對(duì)外發(fā)布PCIe 5.0 0.9版規(guī)范。隨后,2019年5月29日,PCI-SIG正式宣布完成PCIe 5.0規(guī)范,傳輸速率達(dá)到

2021-10-09 16:46:43 5143

5143 中國(guó)上海,2021 年 10 月 22 日——楷登電子(美國(guó) Cadence 公司,NASDAQ:CDNS)宣布發(fā)布支持 TSMC N5 工藝的 PCI Express(PCIe)6.0 規(guī)范

2021-10-26 14:28:00 4482

4482 負(fù)責(zé)制定廣為采用的PCI Express? (PCIe?)標(biāo)準(zhǔn)的組織PCI-SIG?今天宣布正式推出PCIe 6.0規(guī)范,傳輸速度達(dá)到64GT/s。 PCIe 6.0規(guī)范的特點(diǎn) 64GT/s原始數(shù)據(jù)

2022-01-13 09:32:20 4882

4882 在 PCI-SIG工作組發(fā)布PCIe 6.0 基本規(guī)范和驗(yàn)證要求僅幾周后,全球測(cè)試與測(cè)量領(lǐng)導(dǎo)者泰克公司推出了業(yè)界首個(gè)基于最新規(guī)范PCIe 6.0的發(fā)射器測(cè)試解決方案。

2022-02-21 10:11:46 1236

1236 高性能應(yīng)用提供高達(dá)每秒64GT的數(shù)據(jù)傳輸速率。此外,該控制器還提供最先進(jìn)的安全性,其完整性和數(shù)據(jù)加密(IDE)引擎可以監(jiān)控和保護(hù)PCIe鏈路免受物理攻擊。

2022-03-10 11:26:20 1897

1897

2022年1月11日,PCI-SIG正式發(fā)布了PCI Express(PCIe) 6.0最終版本1.0,標(biāo)志著各大IP、芯片廠商可以開(kāi)始著手設(shè)計(jì)、開(kāi)發(fā)自己技術(shù)和產(chǎn)品了。從技術(shù)上來(lái)說(shuō),PCIe 6.0是PCIe問(wèn)世近20年來(lái),變化最大的一次。

2022-04-13 13:50:55 5187

5187 2022年4月14日,北京――是德科技(NYSE:KEYS)發(fā)布新款端到端的 PCIe5.0/6.0 測(cè)試解決方案,使工程師能夠?qū)?PCIe 前沿科技設(shè)計(jì)進(jìn)行仿真、研發(fā)、評(píng)估、驗(yàn)證和一致性測(cè)試。

2022-04-14 14:39:08 1755

1755 提供PCIe5.0/6.0 從仿真到物理層到協(xié)議層的完整測(cè)試方案。

2022-04-18 11:35:35 1992

1992 雖然與前幾代相比,PCIe 6.0 的變化很大,但業(yè)界對(duì)其采用有著強(qiáng)大而廣泛的支持。PCIe 在每個(gè)現(xiàn)代計(jì)算架構(gòu)中無(wú)處不在,您應(yīng)該期望 PCIe 6.0 將在高性能計(jì)算和云計(jì)算空間、企業(yè)存儲(chǔ)和網(wǎng)絡(luò)空間以及新興應(yīng)用程序(如 AI/機(jī)器學(xué)習(xí)和汽車(chē)。

2022-06-01 17:15:50 2502

2502

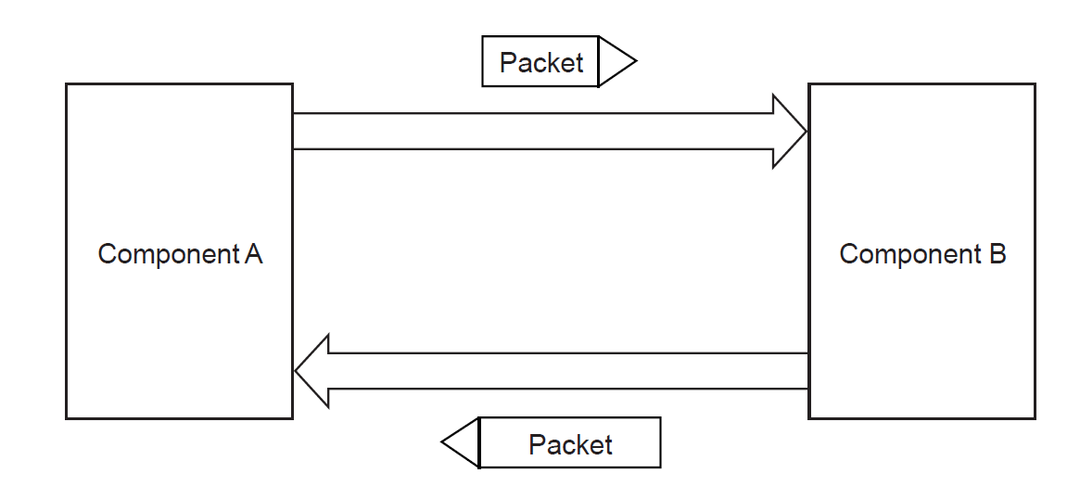

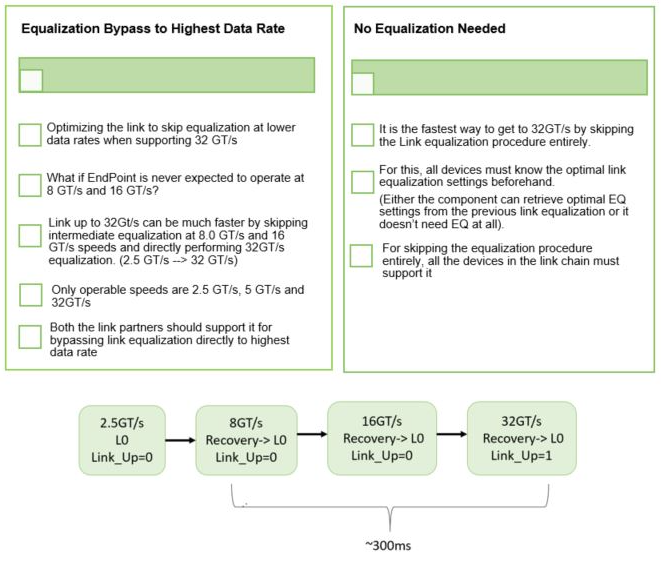

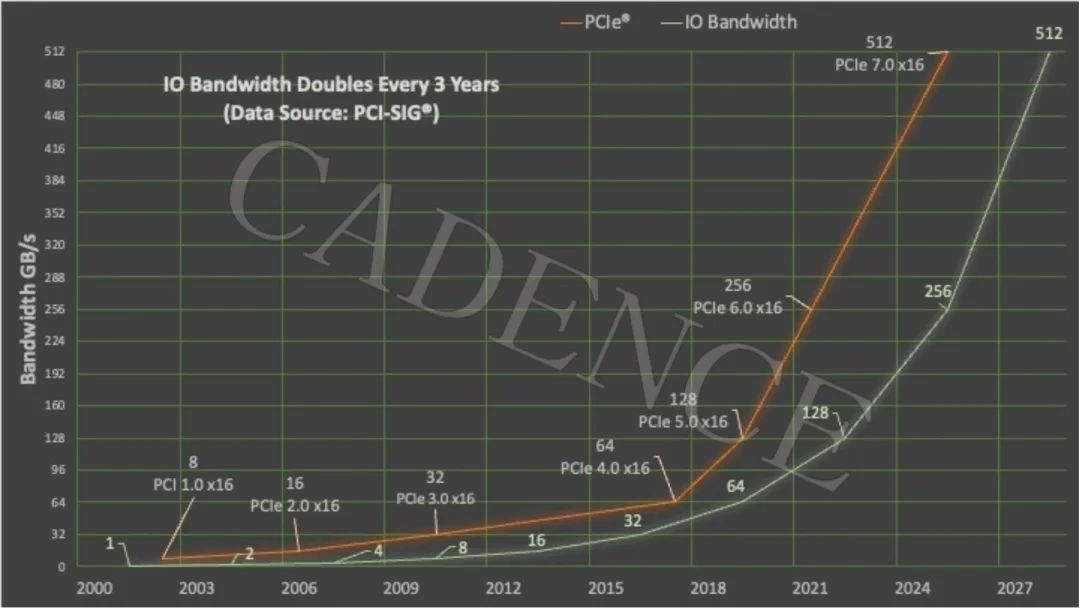

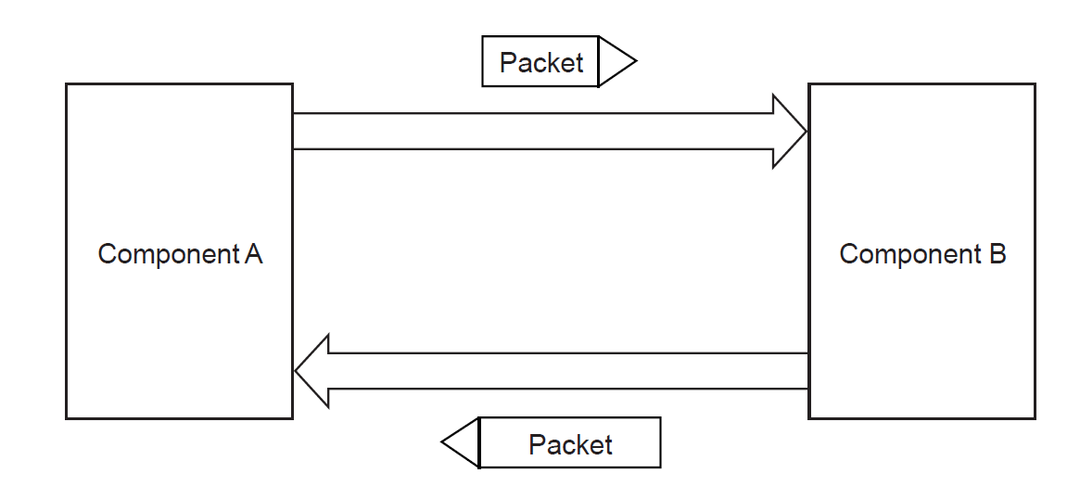

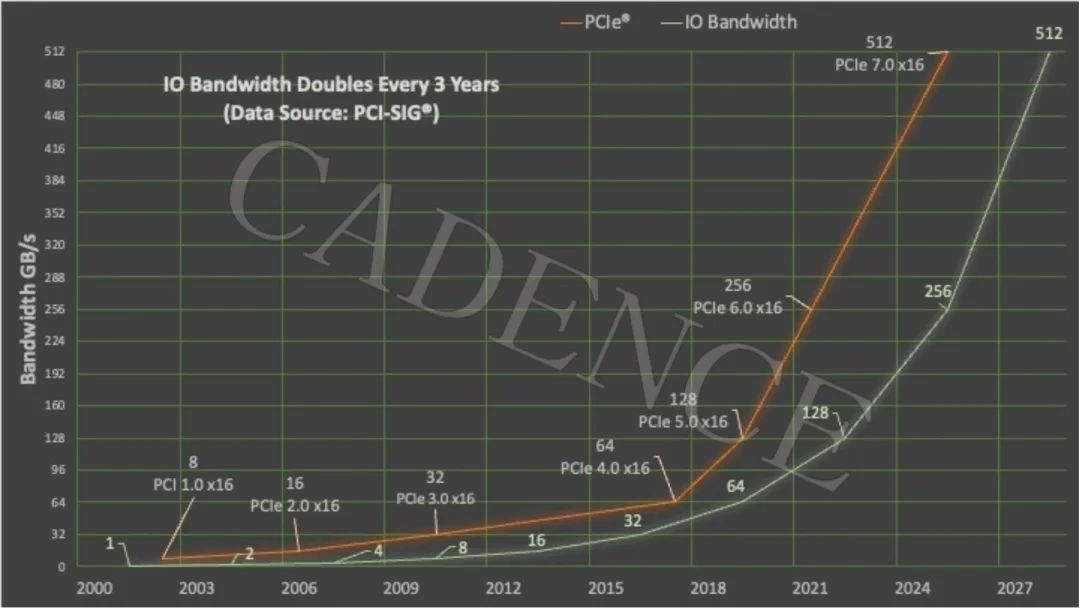

?) 已成為參考的高性能互連。利用高速串行通信,PCIe 提供高效的點(diǎn)對(duì)點(diǎn)連接,并通過(guò)增加通道數(shù)和信號(hào)傳輸速率,提供可擴(kuò)展的接口帶寬。 PCIe 1.0 規(guī)范于 2002 年發(fā)布,以每秒 2.5 千兆傳輸

2022-07-21 09:59:41 1821

1821

PCIe 7.0 接口將繼續(xù)使用 1b/1b flit 模式編碼和隨 PCIe 6.0 引入的 PAM4 信號(hào)技術(shù),這與PCIe 3.0 到PCIe 5.0 規(guī)范中使用的 128b/130b 編碼

2022-07-28 15:11:54 1330

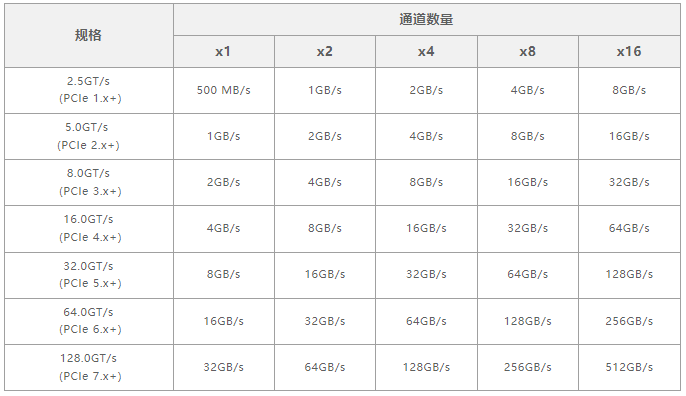

1330 傳輸速率為每秒傳輸量GT/s,而不是每秒位數(shù)Gbps,因?yàn)?b class="flag-6" style="color: red">傳輸量包括不提供額外吞吐量的開(kāi)銷(xiāo)位;比如 PCIe 1.x和PCIe 2.x使用8b / 10b編碼方案,導(dǎo)致占用了20% (= 2/10)的原始信道帶寬。

2022-08-02 09:45:34 2091

2091 PCIe 3.0協(xié)議支持8.0GT/s,即每一條Lane上支持每秒鐘傳輸8G個(gè)Bit。而PCIe 3.0的物理層協(xié)議中使用的是128b/130b編碼方案,即每傳輸128個(gè)Bit,需要發(fā)送130個(gè)Bit。

2022-08-29 16:09:17 3912

3912 6.0被認(rèn)為該標(biāo)準(zhǔn)誕生19年來(lái)最具革命性的一次飛躍,不僅數(shù)據(jù)傳輸率再次翻番最高可達(dá)64GT/s,x16單向帶寬128GB/s、雙向帶

2022-10-27 10:06:23 833

833

,并于 2019 年底隨著 AMD EPYCTM 7002(羅馬)處理器的推出在主流服務(wù)器中首次亮相。PCIe 4.0 將車(chē)道速度提高一倍,達(dá)到 16 GT/s。

2022-11-21 17:08:27 971

971 PCIe 6.0被認(rèn)為該標(biāo)準(zhǔn)誕生19年來(lái)最具革命性的一次飛躍,不僅數(shù)據(jù)傳輸率再次翻番最高可達(dá)64GT/s,x16單向帶寬128GB/s、雙向帶寬256GB/s,更是升級(jí)為1b/1b編碼的PAM4脈沖調(diào)制。

2022-11-23 15:51:30 1308

1308 受委托讓我整理一個(gè)關(guān)于PCIe的主題分享文章,半月有余實(shí)在沒(méi)辦法交差,首先,我自己本身,對(duì)PCIe并沒(méi)有做到胸有成竹,我的PCIe知識(shí)也只是停留在理論階段,我并沒(méi)有實(shí)際做過(guò)任何有關(guān)PCIe的東西

2022-11-28 10:25:52 7922

7922 關(guān)于PCIe6.0 你需要知道的都在這里 從正式發(fā)布至今,PCI Express(PCIe)發(fā)展迅速,已經(jīng)成為高性能計(jì)算、人工智能/機(jī)器學(xué)習(xí)(ML)加速器、網(wǎng)絡(luò)適配器和固態(tài)存儲(chǔ)等應(yīng)用不可或缺的一項(xiàng)

2022-12-07 07:40:08 5459

5459 速率增加幅度也非常顯著。每次推出一個(gè)全新版本的PCIe,它的數(shù)據(jù)傳輸速率對(duì)比上一代基本就是翻倍的。比如PCIe 6.0和上一代的5.0是64GT/s到32GT/s每秒的雙倍提升。 ? 今年年初,PCIe 6.0的規(guī)范和標(biāo)準(zhǔn)已經(jīng)正式提出,Rambus隨及發(fā)布了PCIe 6.0控制器的相關(guān)產(chǎn)品。現(xiàn)在

2022-12-14 11:22:10 3079

3079

本文轉(zhuǎn)載自《半導(dǎo)體行業(yè)觀察》 感謝《半導(dǎo)體行業(yè)觀察》對(duì)新思科技的關(guān)注 PCI Express (PCIe) 6.0規(guī)范實(shí)現(xiàn)了64GT/s鏈路速度,還帶來(lái)了包括帶寬翻倍在內(nèi)的多項(xiàng)重大改變,這也為SoC

2023-01-19 16:50:05 1091

1091 PCI Express (PCIe) 6.0規(guī)范實(shí)現(xiàn)了64GT/s鏈路速度,還帶來(lái)了包括帶寬翻倍在內(nèi)的多項(xiàng)重大改變,這也為SoC設(shè)計(jì)帶來(lái)了諸多新變化和挑戰(zhàn)。對(duì)于HPC、AI和存儲(chǔ)SoC開(kāi)發(fā)者來(lái)說(shuō),如何理解并應(yīng)對(duì)這些變化帶來(lái)的設(shè)計(jì)挑戰(zhàn)變得至關(guān)重要。

2023-02-03 10:23:44 2013

2013 基于Xilinx Artix-7系列FPGA芯片設(shè)計(jì)的M.2 M-Key FPGA加速卡,引出Artix7-484腳芯片的4條高速GT,最高支持PCIE2.0*4速率。

2023-03-24 09:13:17 5073

5073 能就會(huì)越出色。讓這一切成為可能的則是去年發(fā)布的PCI Express(PCIe)6.0規(guī)范。 與PCIe 5.0相比,PCIe 6.0支持的數(shù)據(jù)傳輸速率再次翻倍 ── 64 GT/s。數(shù)據(jù)傳輸速率越快,也就意味著高性能計(jì)算(HPC)、AI推理引擎、云端軟件等應(yīng)用以及數(shù)據(jù)中

2023-03-29 02:25:04 1046

1046 PCI Express? 6.0 (PCIe? 6.0) 規(guī)范由 PCI-SIG? 于 2022 年 1 月發(fā)布。最新一代的 PCIe 標(biāo)準(zhǔn)帶來(lái)了許多激動(dòng)人心的新功能,旨在提高計(jì)算密集型工作負(fù)載的性能,包括數(shù)據(jù)中心、 AI/ML 和 HPC 應(yīng)用程序

2023-05-22 17:27:51 7165

7165

PCIE中術(shù)語(yǔ) GT/s 用于指代在lane上每秒傳輸的編碼位數(shù),這里lane指的就是一組差分信號(hào)對(duì)(一對(duì)用于傳輸,一對(duì)用于接收)。 為了擴(kuò)展帶寬,一個(gè)鏈路可以聚合多個(gè)通道,表示為xN 其中 N 可以是任何

2023-05-22 17:29:34 3257

3257

PCIe 6.0 使用數(shù)據(jù)速率為 4GT/s 的 PAM-64 信令,而不是以較低數(shù)據(jù)速率使用的不歸零 (NRZ) 信令。這意味著發(fā)送和接收的信號(hào)現(xiàn)在將在一個(gè)單位間隔內(nèi)具有四個(gè)不同的電壓電平(2位

2023-05-25 16:06:38 3501

3501

5.0 的傳輸速率為每秒 32 千兆傳輸 (GT/s),而 PCIe 16.4 支持的傳輸速率為 0 GT/s。PCIe 64.5 具有每秒 0 千兆字節(jié) (GB/s) 的單向傳輸帶寬,以 128 GB/s 的雙向流量提供數(shù)據(jù)。

2023-05-26 10:23:14 2101

2101

PCI Express? 5.0規(guī)范,達(dá)到32GT / s的傳輸速率,同時(shí)保持低功耗和與前幾代技術(shù)的向后兼容性。為此,Synopsys 還宣布與 Astera Labs 合作開(kāi)發(fā)業(yè)界首款 PCIe

2023-05-26 10:41:48 2295

2295

隨著PCI Express 6.0 于去年初完成,PCI-SIG 迅速開(kāi)始著手開(kāi)發(fā)下一代 PCIe 7.0,這在去年的開(kāi)發(fā)者大會(huì)上宣布。針對(duì) 2025 年的發(fā)布,PCIe 7.0 的目標(biāo)是再次將

2023-06-19 15:24:58 2205

2205

和12位垂直分辨率,其傳輸速度更是達(dá)到行業(yè)領(lǐng)先的12.8GB/s(通過(guò)PCIe總線)。為實(shí)現(xiàn)最佳流速率,虹科數(shù)字化儀融合了16通道、Gen3和PCIe技術(shù)。數(shù)據(jù)采集后

2023-03-30 10:40:48 1165

1165

PCIe 7.0規(guī)范的數(shù)據(jù)傳輸速率將再次倍增,達(dá)到128 GT/s,大幅度高于PCIe 6.0的64 GT/s和PCIe 5.0的32 GT/s。一個(gè)PCIe 7.0 x16通道可以支持512 GB

2023-06-21 11:32:14 992

992

PCIe 7.0規(guī)范的數(shù)據(jù)傳輸速率將再次倍增,達(dá)到128 GT/s,大幅度高于PCIe 6.0的64 GT/s和PCIe 5.0的32 GT/s。一個(gè)PCIe 7.0 x16通道可以支持512 GB

2023-06-25 10:48:38 1119

1119

期間,PCI-SIG 宣布,PCI Express(PCIe)7.0 規(guī)范已達(dá)到 0.3 版。這意味著數(shù)據(jù)傳輸速率進(jìn)一步翻倍并達(dá)到 128GT/s。該標(biāo)準(zhǔn)預(yù)計(jì)將于 2025 年最終確定。 PCIe 標(biāo)準(zhǔn)大約每三年將

2023-06-28 12:20:01 852

852

)6.0在AI、HPC和數(shù)據(jù)中心中越來(lái)越受歡迎。PCIe 6.0運(yùn)行速度極快,達(dá)到64GT/s,是上一代的兩倍。目前,網(wǎng)絡(luò)服務(wù)器、固態(tài)驅(qū)動(dòng)器、交換機(jī)和AI加速器都已率先采用PCIe 6.0,網(wǎng)絡(luò)接口卡(NIC)和CPU主機(jī)芯片也即將采用該標(biāo)準(zhǔn),但開(kāi)發(fā)者該如何知道PCIe 6.0是否適合進(jìn)行下一款芯

2023-07-12 17:50:01 2066

2066 PCIe 標(biāo)準(zhǔn)之間的主要差異。 PCIe 3.0 PCIe2.0的傳輸速率為5 GT/s,但由于8b/10b編碼方案的開(kāi)銷(xiāo)占比為20%,因此單lane的傳輸帶寬為4Gb/s。PCIe 3.0及以后

2023-07-26 08:05:01 1809

1809

為了實(shí)現(xiàn)64GT/s的鏈路速度,PCIe 6.0采用脈沖幅度調(diào)制4級(jí) (PAM4) 信號(hào),在與32GT/s PCIe相同的單元間隔(UI)中提供4個(gè)幅度級(jí)別(2 位)。圖1顯示了三眼眼圖與此前的單眼眼圖的對(duì)比。

2023-08-05 09:33:13 1116

1116

,一種PCIe驗(yàn)證虛擬IP)對(duì)接Endpoint的仿真環(huán)境進(jìn)行說(shuō)明。 ? ? ? ? 1、選擇低速模式加速仿真 ? 在測(cè)試某些與速率

2023-08-17 09:42:22 1699

1699

:SNPS)近日宣布,新思科技PCI Express(PCIe)6.0 IP在端到端64GT/s的連接下,成功實(shí)現(xiàn)與英特爾PCIe 6.0測(cè)試芯片的互操作性。這一全新里程碑也將保證,在未來(lái)無(wú)論是集成

2023-10-12 15:11:45 516

516 新思科技PCIe 6.0 IP與英特爾 PCIe 6.0測(cè)試芯片實(shí)現(xiàn)互操作 在64GT/s 高速連接下成功驗(yàn)證互操作性,降低高性能計(jì)算SoC的集成風(fēng)險(xiǎn) 新思科技近日宣布,新思科技PCI

2023-10-16 09:22:56 970

970 數(shù)據(jù)密集型市場(chǎng)的重要且可擴(kuò)展的標(biāo)準(zhǔn),其主要進(jìn)步包括帶寬和能效比上一版本提高了一倍,原始數(shù)據(jù)傳輸率從5.0的32GT/s提高到6.0的64GT/s。 content 本期直播預(yù)告 本期云上大講堂,將由 泰克高級(jí)應(yīng)用工程師 李煜 為大家?guī)?lái): ■? PCIe最新進(jìn)展和6.0介紹 ■? PCIe For

2023-11-16 16:30:01 621

621

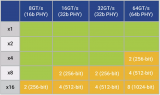

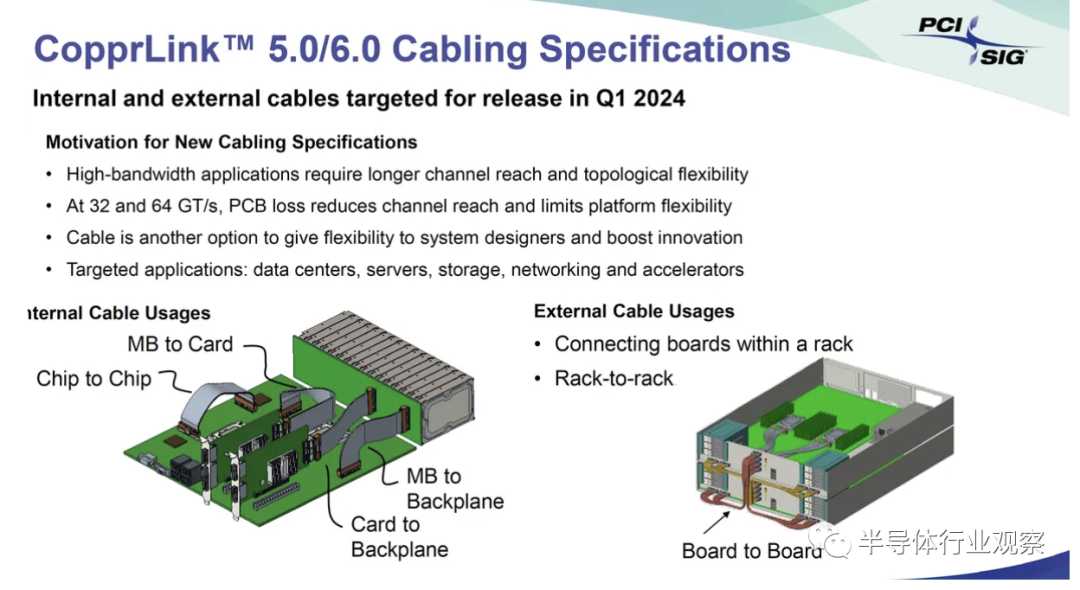

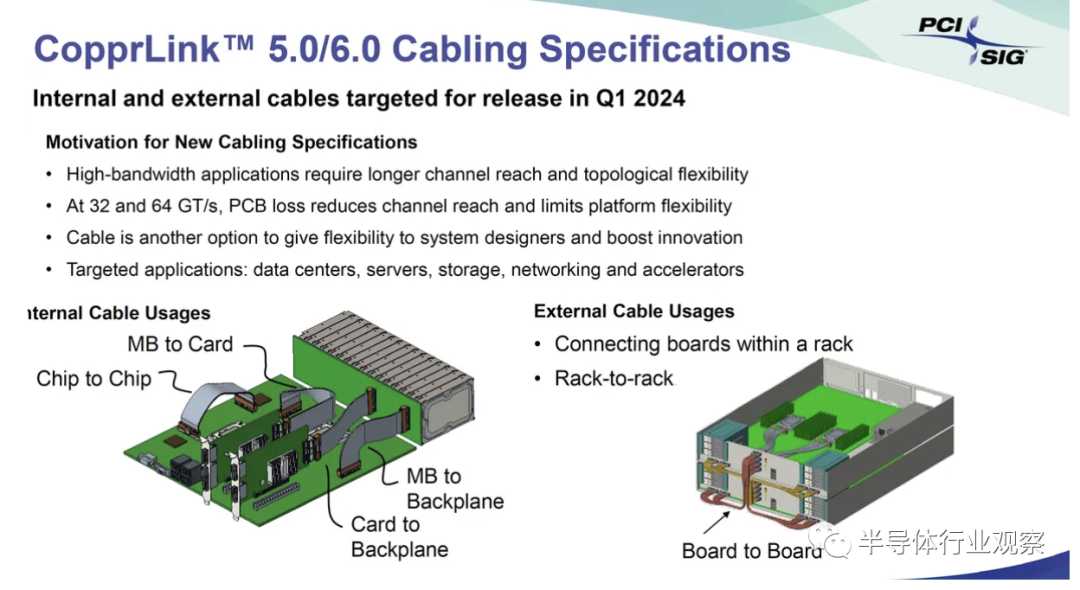

PCI SIG 本周表示,它正在開(kāi)發(fā) PCIe 5.0 和PCIe 6.0接口的布線規(guī)范,數(shù)據(jù)傳輸速率為 32 GT/s 和 64 GT/s。

2023-11-16 17:43:19 2518

2518

傳輸速率為每秒傳輸量GT/s,而不是每秒位數(shù)Gbps,因?yàn)?b class="flag-6" style="color: red">傳輸量包括不提供額外吞吐量的開(kāi)銷(xiāo)位;比如 PCIe 1.x和PCIe 2.x使用8b / 10b編碼方案,導(dǎo)致占用了20% (= 2/10)的原始信道帶寬。

2024-01-16 14:42:02 1715

1715

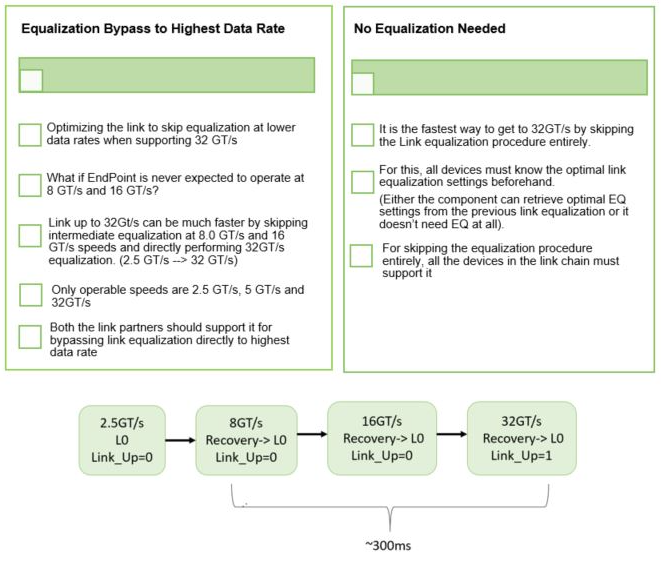

迫切。 一、PCIe 5.0 /6.0技術(shù)升級(jí) 1)信號(hào)速率方面 從PCIe 3.0、4.0、5.0 到 6.0,數(shù)據(jù)速率翻倍遞增,6.0支持64GT/s,16路雙向傳輸帶寬可達(dá)256GB/s。 圖1

2024-03-06 10:35:33 1419

1419

摘要/前言 即將發(fā)布的PCIe? 7.0 規(guī)范旨在實(shí)現(xiàn)128 GT/s的數(shù)據(jù)傳輸速率。它延續(xù)了PCIe 每一代產(chǎn)品速度翻番的趨勢(shì)。根據(jù)?PCI-SIG的說(shuō)法,"PCIe 7.0 技術(shù)的目標(biāo)是為人

2024-03-22 13:42:03 592

592

PCIe 7.0 規(guī)范的目標(biāo)是將 PCIe 6.0 規(guī)范(64 GT/s)的數(shù)據(jù)速率提高一倍,達(dá)到 128 GT/s。

2024-04-08 09:34:05 1339

1339 PCIe 7.0 IP解決方案,加速萬(wàn)億參數(shù)領(lǐng)域的芯片設(shè)計(jì) 新思科技推出業(yè)界首款完整的PCIe 7.0 IP解決

2024-06-29 15:13:32 799

799 由于全球數(shù)據(jù)流量呈指數(shù)級(jí)增長(zhǎng),PCIe 6.0 交換機(jī)的市場(chǎng)需求也出現(xiàn)了激增。PCIe 6.0 交換機(jī)在高性能計(jì)算(HPC)系統(tǒng)(尤其是數(shù)據(jù)中心)中為需要大帶寬和超低延遲的應(yīng)用提供了重要的數(shù)據(jù)傳輸

2024-07-05 09:45:18 811

811

速率、通道數(shù)量、功耗等方面有所不同。 PCIe 3.0是PCIe總線的第三個(gè)版本,于2010年發(fā)布。它的最大傳輸速率為8 Gbps,支持最多32個(gè)通道。PCIe 3.0在功耗、兼容性等方面進(jìn)行了優(yōu)化,使

2024-07-10 10:12:09 10108

10108 PCIe 1.0:2003年推出,數(shù)據(jù)傳輸速率為2.5 GT/s。 PCIe 2.0:2007年推出,數(shù)據(jù)傳輸速率提升至5 GT/s。 PCIe 3.0:2010年推出,數(shù)據(jù)傳輸速率

2024-07-10 10:16:23 5271

5271 在近期的博文《新思科技率先推出PCIe 7.0 IP解決方案,加速HPC和AI等萬(wàn)億參數(shù)領(lǐng)域的芯片設(shè)計(jì)》中,新思科技宣布推出綜合全面的PCIe Express Gen 7(PCIe 7.0)驗(yàn)證IP(VIP)解決方案,以支持高性能計(jì)算設(shè)計(jì)中人工智能(AI)應(yīng)用所需的高速度和低延遲。

2024-07-24 10:11:23 1114

1114

的吞吐量較上一代 PCIe 4.0 增加一倍。需要注意的是 PCIe 原始傳輸速率的單位是 GT/s ,而鏈路數(shù)據(jù)速率的單位是 Gb/s。 表 1:五代 PCIe 的對(duì)比表 需要注意,編碼方案從

2024-08-16 09:33:05 1416

1416

十多年來(lái),Cadence 對(duì) PCIe 技術(shù)的堅(jiān)定承諾和支持,在業(yè)界有目共睹。我們深知強(qiáng)大 PCIe 生態(tài)系統(tǒng)的重要性,并感謝 PCI-SIG 提供的平臺(tái)。在 PCI-SIG 開(kāi)發(fā)者大會(huì)迎來(lái) 32 周年之際,Cadence 宣布面向 HPC/AI 市場(chǎng)推出完整的 PCIe 7.0 IP 解決方案。

2024-08-29 09:14:57 785

785

4.0相較于PCIe 3.0,最直觀的提升就是帶寬的增加。PCIe 3.0的單通道帶寬為8 GT/s(Giga Transfers per second),而PCIe 4.0的單通道帶寬提升至16 GT

2024-11-06 09:22:07 9426

9426 1. PCIe 5.0和6.0的推出 PCIe 5.0和6.0是最新的PCIe標(biāo)準(zhǔn),它們提供了更高的數(shù)據(jù)傳輸速率。PCIe 5.0的數(shù)據(jù)傳輸速率可達(dá)32 GT/s,而PCIe 6.0則進(jìn)一步提升

2024-11-06 09:35:08 1391

1391 現(xiàn)代計(jì)算機(jī)系統(tǒng)中不可或缺的一部分。 PCIe接口的發(fā)展歷程 PCIe接口自2003年推出以來(lái),已經(jīng)經(jīng)歷了多次迭代和升級(jí)。從最初的PCIe 1.0,到現(xiàn)在的PCIe 5.0,數(shù)據(jù)傳輸速率從2.5 GT

2024-11-13 10:22:38 2712

2712 不同的版本和通道寬度,這決定了數(shù)據(jù)傳輸速率和帶寬。以下是一些常見(jiàn)的PCIe插槽規(guī)格: PCIe 1.0 :2.5 GT/s 數(shù)據(jù)傳輸速率,x1、x4、x8 和 x16 通道寬度。 PCIe 2.0 :5

2024-11-13 10:30:53 4062

4062 發(fā)展到了第五代。 一、帶寬和數(shù)據(jù)傳輸速率 PCIe總線的一個(gè)關(guān)鍵特性是其帶寬,即數(shù)據(jù)傳輸速率。PCIe 4.0的帶寬是PCIe 3.0的兩倍,達(dá)到了每通道16 GT/s(Giga Transfers

2024-11-13 10:35:28 11688

11688 規(guī)范的第四代,而PCIe 3.0是第三代。它們之間的主要區(qū)別如下: 帶寬與速率 : PCIe 4.0提供了高達(dá)16 GT/s(千兆傳輸率/秒)的雙向吞吐量,這意味著其理論最大帶寬為32 GB/s(千兆

2024-11-26 15:12:49 3302

3302 ,幫助您做出合適的選擇: 一、了解PCIe版本與性能 PCIe版本 :PCIe 4.0相比PCIe 3.0在帶寬方面有了顯著提升,提供了高達(dá)64GB/s(理論最大值,實(shí)際可能因設(shè)備差異而有所降低)的傳輸

2024-11-26 16:10:26 926

926 由于CPU、GPU、加速器和交換機(jī)的創(chuàng)新,超大規(guī)模數(shù)據(jù)中心的接口需要更快的數(shù)據(jù)傳輸,不僅在計(jì)算和內(nèi)存之間,還涉及網(wǎng)絡(luò)。PCI Express (PCIe?) 成為這些互連的基礎(chǔ),支持構(gòu)建 CXL

2025-01-02 08:43:28 442

442

批準(zhǔn) Draft 0.5版基礎(chǔ)規(guī)范,目前0.7版本基礎(chǔ)規(guī)范正在審核中,預(yù)計(jì)2025年敲定最終發(fā)行版本。 PCIe 7.0 規(guī)范包括以下功能目標(biāo): 通過(guò) x16 配置提供 128 GT/s 原始比特率和高達(dá) 512 GB/s 的雙向比特率。 利用 PAM4信令, 以實(shí)現(xiàn)更高效的信號(hào)傳輸和更高的數(shù)據(jù)吞吐量

2025-02-10 10:03:37 219

219

電子發(fā)燒友網(wǎng)報(bào)道(文/黃晶晶)PCIe 5.0作為新一代高速接口標(biāo)準(zhǔn),其帶寬大幅提升至32 GT/s,相較于PCIe 4.0翻了一番。這種高效的數(shù)據(jù)傳輸能力使得PCIe 5.0在處理高質(zhì)量圖像、游戲

2025-01-27 00:03:00 4317

4317

6088

6088 5200

5200 2054

2054

11312

11312 734

734

571

571

633

633

2465

2465 1066

1066

3018

3018 55

55 1126

1126 10738

10738 7783

7783

1250

1250 4883

4883

2608

2608 3690

3690 5143

5143 4482

4482 4882

4882 1236

1236 1897

1897

5187

5187 1755

1755 1992

1992 2502

2502

1821

1821

1330

1330 2091

2091 3912

3912 833

833

971

971 1308

1308 7922

7922 5459

5459 3079

3079

1091

1091 2013

2013 5073

5073 1046

1046 7165

7165

3257

3257

3501

3501

2101

2101

2295

2295

2205

2205

1165

1165

992

992

1119

1119

852

852

2066

2066 1809

1809

1116

1116

1699

1699

516

516 970

970 621

621

2518

2518

1715

1715

1419

1419

592

592

1339

1339 799

799 811

811

10108

10108 5271

5271 1114

1114

1416

1416

785

785

9426

9426 1391

1391 2712

2712 4062

4062 11688

11688 3302

3302 926

926 442

442

219

219

4317

4317 電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論