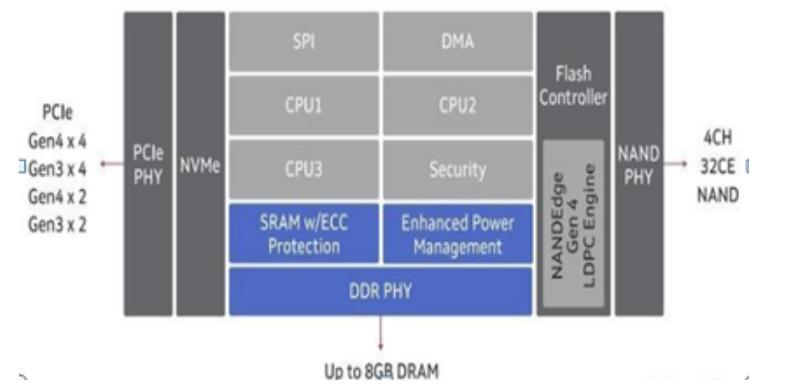

PCI Express? 5.0規范,達到32GT / s的傳輸速率,同時保持低功耗和與前幾代技術的向后兼容性。為此,Synopsys 還宣布與 Astera Labs 合作開發業界首款 PCIe 5.0 重定時器 SoC。人工智能、云、數據中心和 5G 等新興應用一直在推動帶寬需求的指數級增長,而 PCIe 已經不斷發展以滿足這些不斷增長的需求。

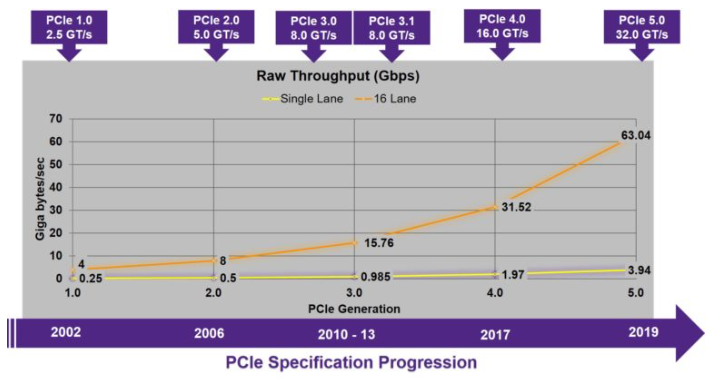

PCIe 協議在過去 15+ 年中迅速發展,從 2 年第 5 代的 2002.1GT/s 原始比特率,到今天最新的 PCIe 32.5 的 0GT/s。PCI Express 從桌面計算到云的采用,對增加吞吐量、減少延遲、占用空間和功耗的需求不斷增長,一直在推動 PCIe 標準的創新。

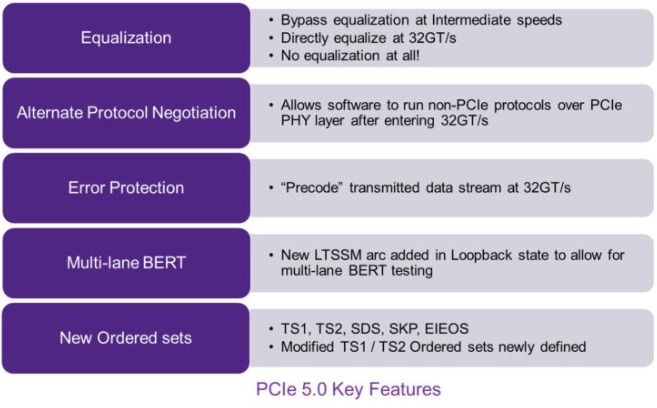

PCIe 5.0 增加了重要的新功能,例如新的均衡選項和備用協議協商 (APN),以滿足系統要求,具有可預測和穩定的帶寬、延遲和功率(見下文)。

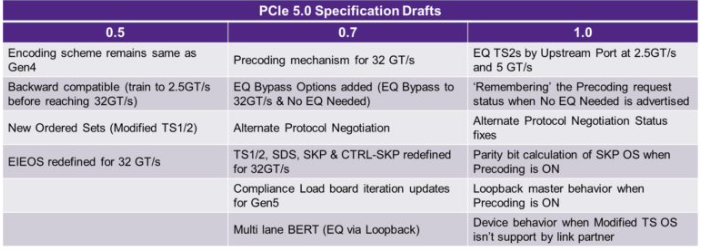

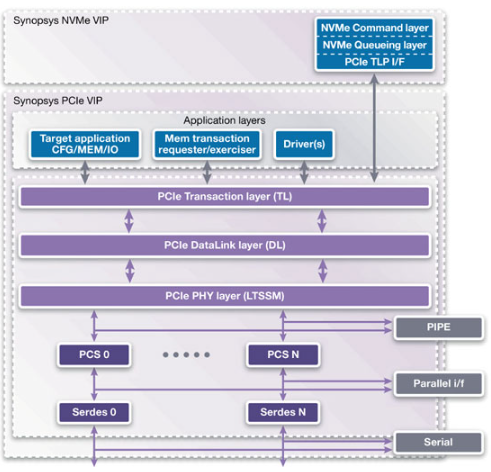

自規范最初構思以來,適用于 PCIe 5.0 的 Synopsys VIP 和源代碼測試套件已被從事下一代云、數據中心、5G 和 HPC 設計的行業領導者廣泛采用。VIP功能和測試套件與這些領先的PCIe Gen5采用者合作得到增強和成熟,以系統地降低每個規范草案中發布的新功能的設計實施風險(見下文)。

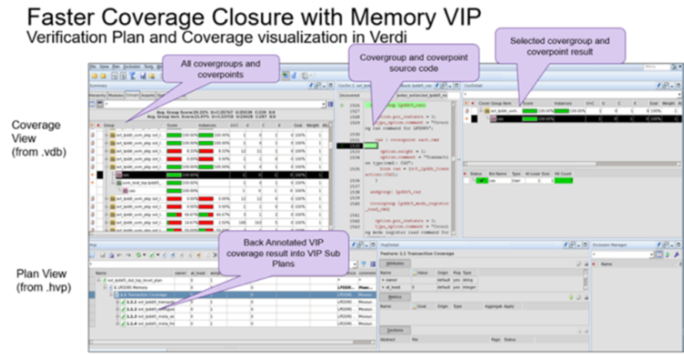

Synopsys VIP 通過其原生 SV/UVM 實施以及與 Synopsys VCS 和 Verdi Protocol Analyzer 的原生集成,提高了性能和驗證效率。Synopsys VIP 提供內置功能覆蓋范圍和源代碼第 5 代測試套件,以加快驗證收斂并實現一次性質量設計的流片。

審核編輯:郭婷

-

定時器

+關注

關注

23文章

3287瀏覽量

117199 -

數據中心

+關注

關注

16文章

5135瀏覽量

73190 -

人工智能

+關注

關注

1804文章

48691瀏覽量

246423

發布評論請先 登錄

硬盤開啟PCIe 5.0時代

Synopsys為更快速的SoC驗證推出下一代驗證IP

基于FPGA的PCIe總線接口的DMA控制器的實現并進行仿真驗證

PCIe 5.0時代正式拉開序幕

PCIe 5.0對互聯芯片的性能驗證要求

什么是 PCIe 5.0? PCIe 5.0規范以及挑戰

microchip全新的PCIe 5.0交換芯片怎么樣

Cadence推出新一代CXL VIP和系統VIP工具

覆蓋模型 – 填補內存VIP的漏洞

什么是PCIe?PCIe有什么用途?PCIe 5.0有何不同?

新思科技PCIe 7.0驗證IP(VIP)的特性

使用Synopsys VIP簽署PCIe 5.0驗證

使用Synopsys VIP簽署PCIe 5.0驗證

評論