在近期的博文《新思科技率先推出PCIe 7.0 IP解決方案,加速HPC和AI等萬億參數領域的芯片設計》中,新思科技宣布推出綜合全面的PCIe Express Gen 7(PCIe 7.0)驗證IP(VIP)解決方案,以支持高性能計算設計中人工智能(AI)應用所需的高速度和低延遲。

在《PCIe 7.0數據速率的光傳輸首秀,一睹為快!》一文中,可查看業界首個PCIe 7.0光傳輸Demo。

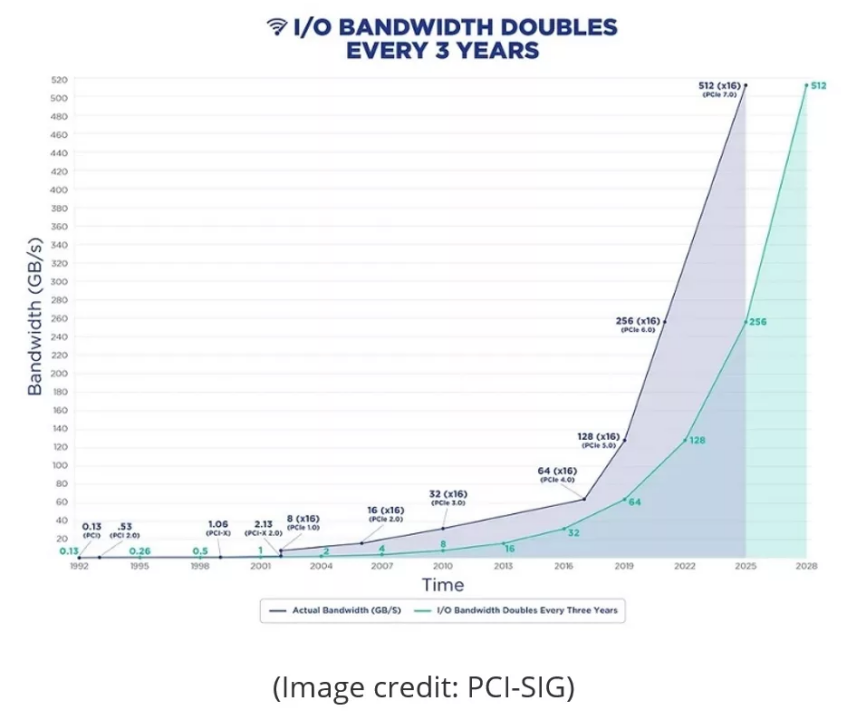

PCI Express的演進

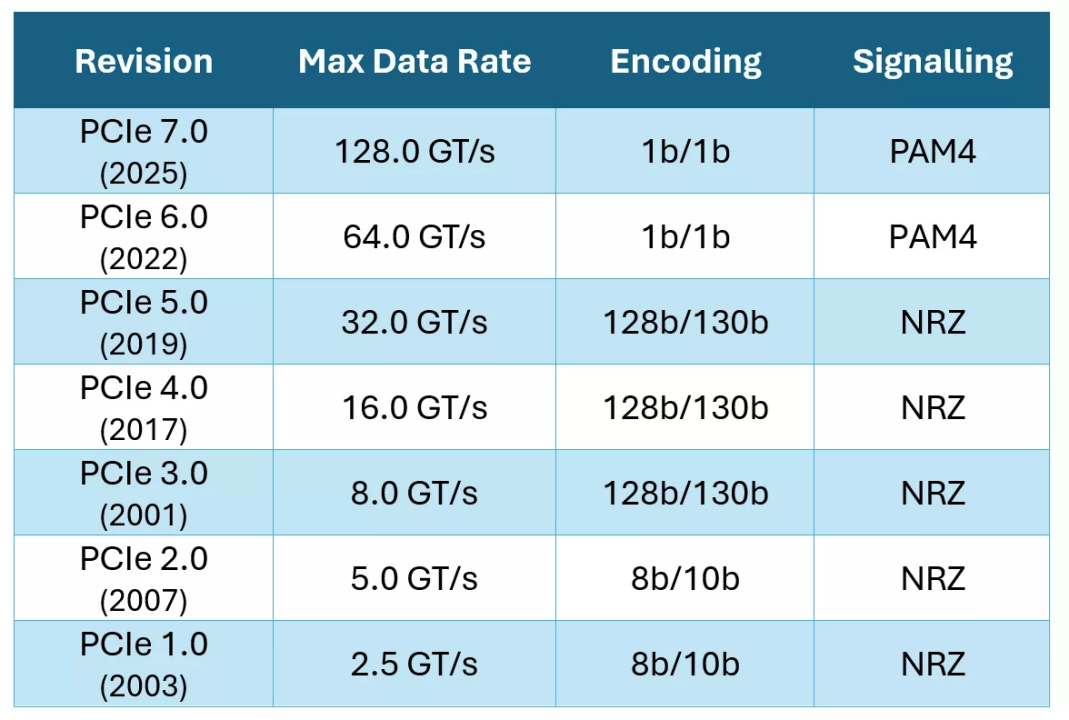

自2003年推出以來,PCI Express在技術、規格和傳輸速度方面不斷進步,成為了一項成功的標準化計劃倡議和數據傳輸協議。PCIe 5.0為云計算資源提供32G傳輸速度和CXL一致性;而在流量控制單元(FLITS)和PAM4調制的加持下,PCIe 6.0將性能提高至64G傳輸速率,實現了高效率、低延遲的通信和一致性。PCIe 7.0的加載-存儲功能和高達512 GB/s的安全數據傳輸帶寬,讓連接多個加速器并高效處理大型復雜人工智能和機器學習模型成為可能。

PCIe 7.0規范新增了哪些內容?

PCIe 7.0規范中包含以下特性:

經由x16鏈路,數據速率達128 GT/s,經由x16鏈路,雙向最高可達512 GB/s

PAM4信令

1b/1b FLIT模式編碼

前向糾錯(FEC)

更出色的功耗和成本效率

采用IDE協議,確保數據安全

向后兼容PCIe規范的早期版本

包含睡眠狀態,以提供靈活性和低功耗

新思科技PCIe 7.0驗證IP(VIP)的特性

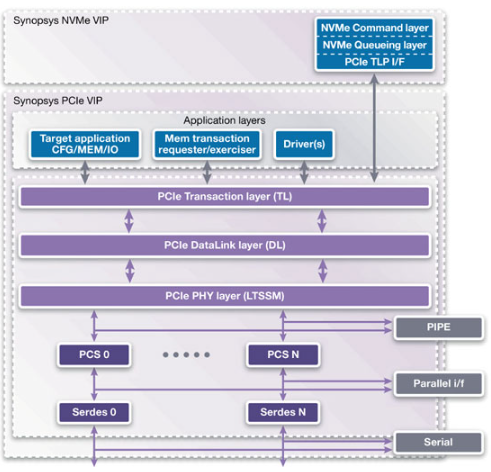

新思科技PCIe驗證IP可對基于各種PCIe規范(PCIe 1.0至7.0)的設計實現方案進行驗證,可用于SoC和系統級設計,以加速驗證收斂。

新思科技PCIe驗證IP解決方案支持PCIe 7.0,并利用了以下特性來解決設計驗證的復雜性:

支持每條通道最高128.0 GT/s的數據速率,同時保持RC和EP設備的向后兼容性,進而推動從PCIe 6.0無縫過渡到PCIe 7.0。

原生System/Verilog UVM架構,有助于輕松集成到仿真環境中并加快測試平臺開發。

集成驗證計劃、測試套件和功能覆蓋率,可加快驗證過程并贏取競爭優勢。

基于IDE的數據完整性和安全保護,可防止數據和系統泄露。

豐富的可配置選項和內置的協議檢查,有助于在已采用協議開發的市場中保持競爭力。

新思科技正在與早期客戶和伙伴合作,整合最新規范中提供的新功能,助其增強下一代設計的標準架構。

新思科技VIP原生集成了Verdi協議分析器調試解決方案和Verdi性能分析器。

要在SoC上運行系統級有效載荷,速度更快且基于硬件的流片前解決方案必不可少。基于新思科技IP的新思科技事務處理器、內存模型、混合和虛擬解決方案可在高速的驗證硬件,新思科技ZeBu硬件加速解決方案和新思科技HAPS原型系統上實現豐富的驗證工作和驗證用例。

-

PCIe

+關注

關注

16文章

1312瀏覽量

84600 -

人工智能

+關注

關注

1804文章

48599瀏覽量

245974 -

新思科技

+關注

關注

5文章

849瀏覽量

51126

原文標題:PCI 7.0 VIP如何解鎖萬億參數AI模型的高性能計算潛力?

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Synopsys為更快速的SoC驗證推出下一代驗證IP

Mentor Graphics推出新的Mentor EZ-VIP PCI Express驗證IP

新思科技推出業內首個DDR5 NVDIMM-P驗證IP 加速驗證工作完成

Synopsys為Arm AMBA CXS的VIP提供EDA驗證解決方案

Cadence推出15種新驗證 IP(VIP)解決方案

新思科技設計、驗證和IP解決方案助力Arm全面計算戰略

Cadence推出新一代CXL VIP和系統VIP工具

新思科技PCIe 6.0 IP與英特爾PCIe 6.0測試芯片實現互操作

新思科技成功實現與英特爾PCIe 6.0測試芯片的互操作性

新思科技推出業界首款PCIe 7.0 IP解決方案

新思科技發布PCIe 7.0 IP解決方案,賦能AI與HPC前沿設計

新思科技推出業界首款PCIe 7.0 IP解決方案

Cadence展示完整的PCIe 7.0 IP解決方案

新思科技PCIe 7.0驗證IP(VIP)的特性

新思科技PCIe 7.0驗證IP(VIP)的特性

評論