本文翻譯轉載于:Cadence Blog

作者:xinmu

PCIe 6.0 規范于 2021 年發布,采用 PAM4 調制(即 4 電平脈沖幅度調制),使數據傳輸速度翻倍,達到 64GT/s。同時,PCIe 6.0 規范使用 FLIT(流量控制單元)作為新的數據傳輸單元,顯著提高了傳輸效率。

PCIe 6.0 擁有眾多新功能和變化,我們將討論其中一項重要功能:FLIT。接下來,我們將結合自身的設計和驗證經驗,重點分析當前面臨的挑戰,探討相應的解決方案。

PCIe 6.0 中的 FLIT 是什么?

在先前版本中,事務數據以可變長度的形式存在,稱為 TLP。它們的包頭大小是固定的,但數據有效負載的長度有所不同。無論 TLP 有多長,都是使用 32 位 CRC 進行保護。在 PCIe 6.0 中,由于額外的信號狀態,PAM4 信號本身比 NRZ 信號更脆弱。新的調制需要 FEC 來緩解 PAM4 較高的誤碼率,且要求在固定大小的數據包上實現糾錯功能,因此在 PCIe 6.0 設計中使用了 FLIT(流控制單元)。

FLIT 的長度固定為 256 字節,其中包含 236 字節的 TLP、6 字節的 DLP、8 字節的 CRC 和 6 字節的 FEC。它去除了 1b/1b 編碼的同步頭、幀定界符等部分。FLIT 也具有類似的序列號概念,其中 DLP 的前 2 個字節包含專用于 FLIT 級別序列號、Ack/Nak、重試機制等方面的相關信息。

FEC(前向糾錯)是針對延遲而設計的,其復雜性會隨著糾正的符號數量增加而呈指數增長。6 字節的 FEC 負責 3 個交織組,每組有 2 個 FEC 字節,以防在少于 3 個字節時出現突發錯誤。

第一個挑戰涉及新的 FLIT 格式和編碼變化

在鏈路訓練、輪詢和配置階段開始時,使用 TS1 中“Data Rate Identifier(數據速率標識符)”字段(符號 4,位 0)中的“FLIT 模式支持”位,實現 FLIT 模式的啟用機制和協商。協商成功后,FLIT 模式將適用于所有數據速率,因此也支持 8b/10b 和 128b/130b(混合模式)。

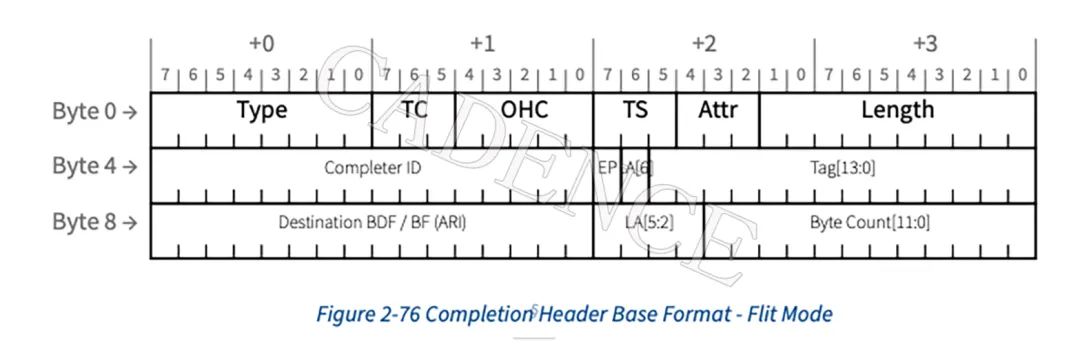

進入 FLIT 模式后,我們采用一種全新的 TLP Header 格式。先前的 TLP Header 存在諸多局限性,例如沒有為標簽尺寸增加預留空間。為了滿足 FLIT 模式的需求,PCI-SIG 對包頭進行了重新設計。在此期間,我們面臨的挑戰是需要測試所有新的組合。

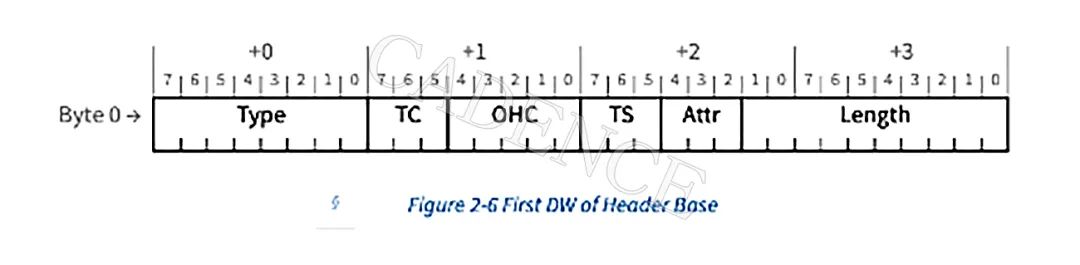

TLP Header 包含 3 到 7 個 DW TLP Header Base,后面跟隨 0 到 7 個額外 DW 的 OHC(正交頭內容)。

新引入的字段具有完全解碼的 8b Packet Type(數據包類型)字段。這意味著所有 256 個類型值都已被明確定義或預留用于特定群組,以確保正確實現幀定界和轉發。

此外,還為 FLIT 模式設計了新的填寫規則。未發布的 TLP 的填寫也有重大更新,包括 14 位標簽、使用 OHC-A5 的錯誤報告等。

據我們所知,236 字節可以容納 1 個完整的 TLP 或多個 TLP。如果遇到較長的 TLP,還可以將其拆分成多個 FLIT 進行傳輸。在每個 TLP 之間,如果沒有計劃發送更多的 TLP,可能會插入一個 NOP TLP。PCIe 6.0 規范中還有一些新的規定,例如在 FLIT 的 32 DW 邊界內,每個 FC/VC 最多只能包含 4 個 TLP(非 NOP)。

DLP 是一個 6 字節序列,其中前 2 個字節專門用于處理 FLIT 級別的 Ack/Nak、重試等信息,因此設計了新的格式。比如,“FLIT usage(FLIT 用途)”字段用于區分空閑 FLIT、NOP FLIT 或有效負載 FLIT;“Prior FLIT(前一個 FLIT)”字段用于標識非 NOP 或 NOP,避免重試錯誤的發生;“replay command(回放命令)”和“sequence number(序列號)”用于確定 Ack/Nak/Retry 的執行。

此外,在 FLIT 序列號和重試機制中,新定義了多種 FLIT 傳輸和交換規則。例如,CONSECTIVE_TX_EXPLICIT_SEQ_NUM_FLITS 和 CONSECUTIVE_TX_NAK_FLITS 計數器及其相關規則。

為了測試所有主要的編碼和格式變化,必須確保覆蓋所有新的數據包字段。針對上述新功能的通用解決方案是定義并實現良好的覆蓋范圍,以確保新功能得到充分測試。一個好的覆蓋模型有助于充分測試新功能。

除 FLIT 格式外,FLIT 模式帶來的另一項重大挑戰是新的序列號和重試機制

在驗證過程中,其中一項最難的挑戰是IMPLICIT_RX_FLIT_SEQ_NUM 規則。該計數器對于回放機制至關重要。隱式 FLIT 序列號未包含在 FLIT 中,因此完全依靠內部邏輯來處理。內部邏輯/計數器需要處理多種場景,以確保正確計算 IMPLICIT_EX_FLIT_SEQ_NUM。

確保 TX 重試緩沖區的準確性也非常重要,因為在接收 Ack 或 Nak 之前,所有 FLIT 都需要存儲在緩沖區。一個 FLIT 可能包含多個 TLP,或者一個大 TLP 可以分成多個 FLIT,因此需要保證重傳的 FLIT 不會跳過 TLP 或將額外的 TLP 添加在原始 FLIT 中。這對于 Posted TLP 至關重要,因為它沒有 Completion 通知。一旦 TLP 丟失,將導致無法糾正的錯誤。

借助新的標準 Nak/選擇性 Nak,發射器可以回放特定 FLIT 或多個 FLIT。相關規則對 TX 和 RX 重試緩沖區均有影響。此外,發送標準或選擇性 NAK 需要考慮具體的實施場景,因此有時很難預測和檢查是否存在協議違規行為。

FEC 算法是一項新功能,我們需要確保 TX 和 RX 兩端的計算都正確無誤。

基于上述要點,我們嘗試了使用以下解決方案來驗證設計

1. 除了按照規范正確實現 IMPLICIT_RX_FLIT_SEQ_NUM 計數器之外,我們還發現,將隱式 FLIT 序列號記錄在狀態寄存器中或顯示在調試日志中,能夠更方便地進行比較和調試。

2. 確保您的監視器可以存儲所有的 FLIT,將保存的 FLIT 與每個符號上的已退役 FLIT 進行比較,并報告相應的錯誤。

3. 必須確保 RTL 和監視器都具有足夠大的重試緩沖區,以便能夠應對在收到標準 NAK 后重新發送多個 FLIT 的情況。另外,需要采用一個檢查器,根據規范預測標準和選擇性 NAK 傳輸條件。最后,檢查回放的 FLIT 序列號是否與收到的選擇性 NAK 相匹配。

4.為了確保 FEC 算法邏輯的正確性,需要使用具有隨機符號位置的故障注入測試用例。

總而言之,PCIe 6.0 是一個復雜的協議,具有諸多驗證挑戰。要成功驗證該協議,必須了解新規范的變化,并制定完善的新功能驗證計劃以及受新功能影響的向后兼容性測試。Cadence 的 PCIe 6.0 驗證 IP 完全符合最新的 PCIe Express 6.0 規范,并為驗證 PCIe 6.0 接口交互的器件提供了一種高效且可靠的解決方案。適用于 PCIe 6.0 的 Cadence VIP 提供全面的驗證解決方案,可用于驗證基于 PCIe 的 IP 和 SoC。我們正在與早期采用者客戶密切合作,旨在加速每個驗證階段的進程。

-

調制

+關注

關注

0文章

165瀏覽量

30007 -

計數器

+關注

關注

32文章

2284瀏覽量

96021 -

PCIe

+關注

關注

16文章

1322瀏覽量

84656

原文標題:破解 PCIe 6.0 FLIT 模式帶來的新挑戰

文章出處:【微信號:gh_fca7f1c2678a,微信公眾號:Cadence楷登】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

解析PCIe 6.0中的正交頭內容(OHC)

PCIe 6.0元年,AI與HPC迎來新速度

一文詳解CXL鏈路層格式的定義

楷登電子發布PCIe 6.0規范Cadence IP

PCI-SIG?發布PCIe?6.0規范以助力大數據應用

PCIe 6.0的新變化與新挑戰

支援PCIe 6.0的Rambus解決方案

PCIe 7.0發布,速度高達512 GB/s

干貨:PCIE6.0技術剖析

面向高性能數據中心和人工智能SoC Rambus推出PCIe 6.0接口子系統

如何破解PCIe 6.0帶來的芯片設計新挑戰?

PCIe 6.0入門之什么是 PCIe 6.0

淺析PCIe標準和布線的開發

PCIe的基礎知識整理

詳解PCIe 6.0中的FLIT模式

詳解PCIe 6.0中的FLIT模式

評論