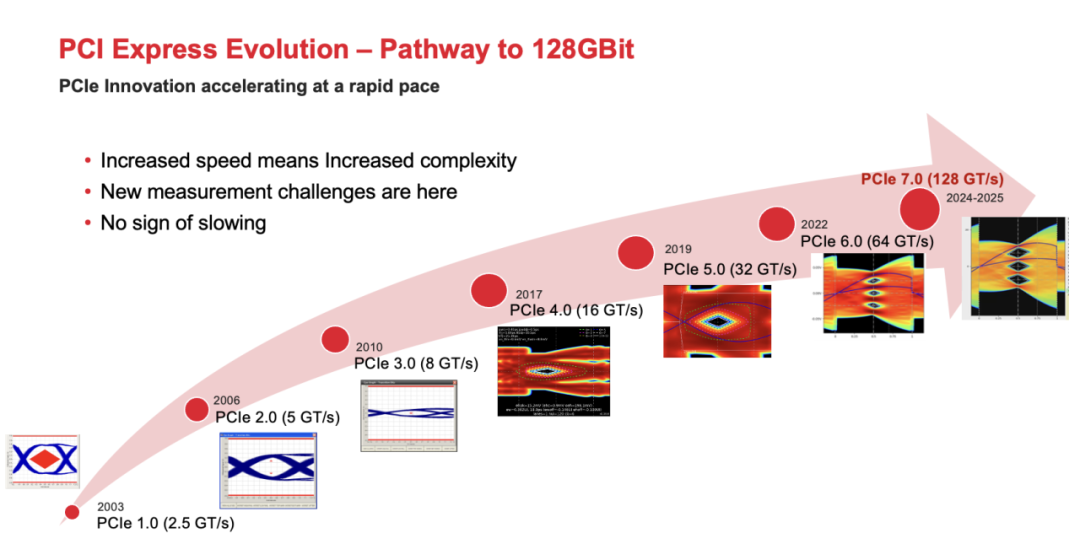

近日,PCI 特別興趣小組 (PCI-SIG) 將在圣克拉拉舉辦其年度開發(fā)者大會。業(yè)界卓越的擴展總線的開發(fā)人員和生態(tài)系統(tǒng)成員的年度聚會為硬件開發(fā)人員提供了大量的技術(shù)會議,但對于局外人來說,來自該展會的最重要的新聞往往是 SIG 的年度更新狀態(tài)生態(tài)系統(tǒng)。今年也不例外,他們更新了 PCIe 7.0 的開發(fā)狀態(tài),以及 PCIe 6.0 的采用和布線工作。

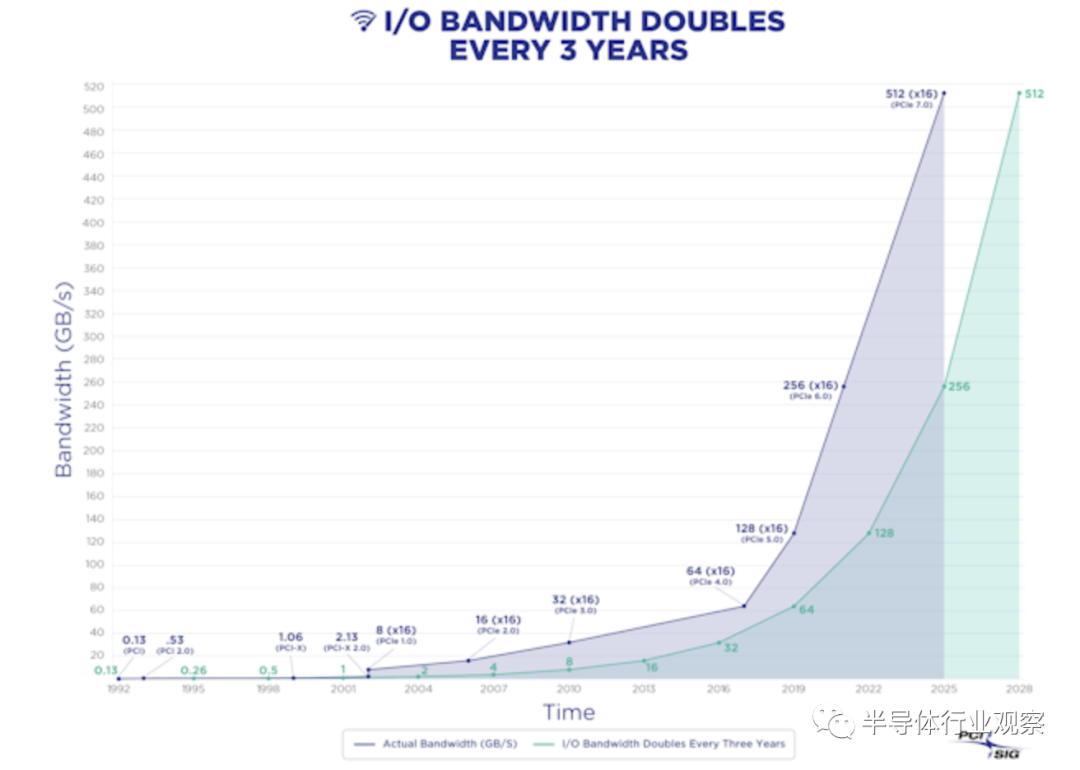

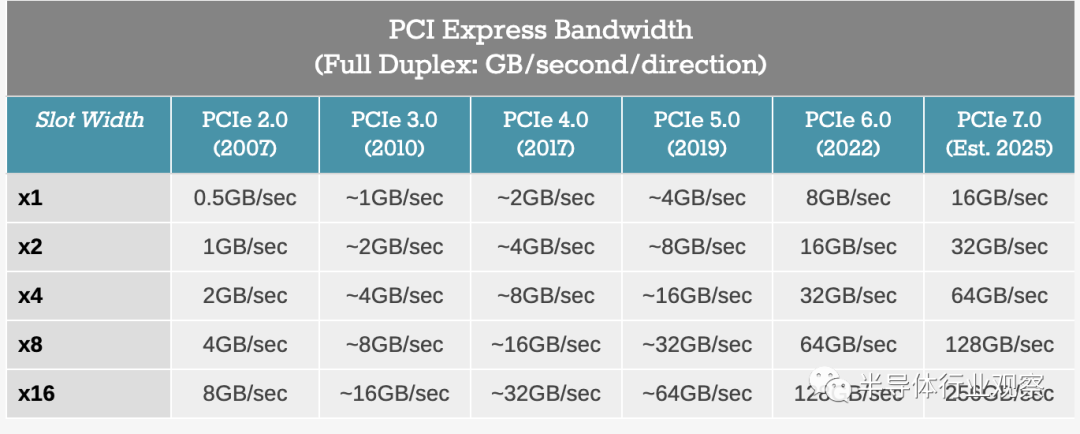

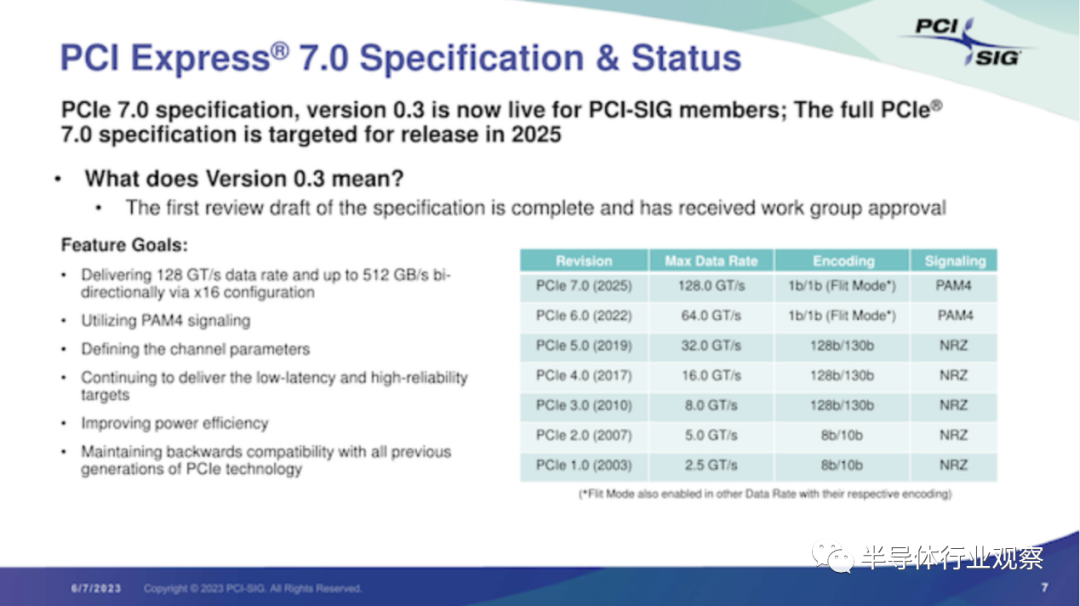

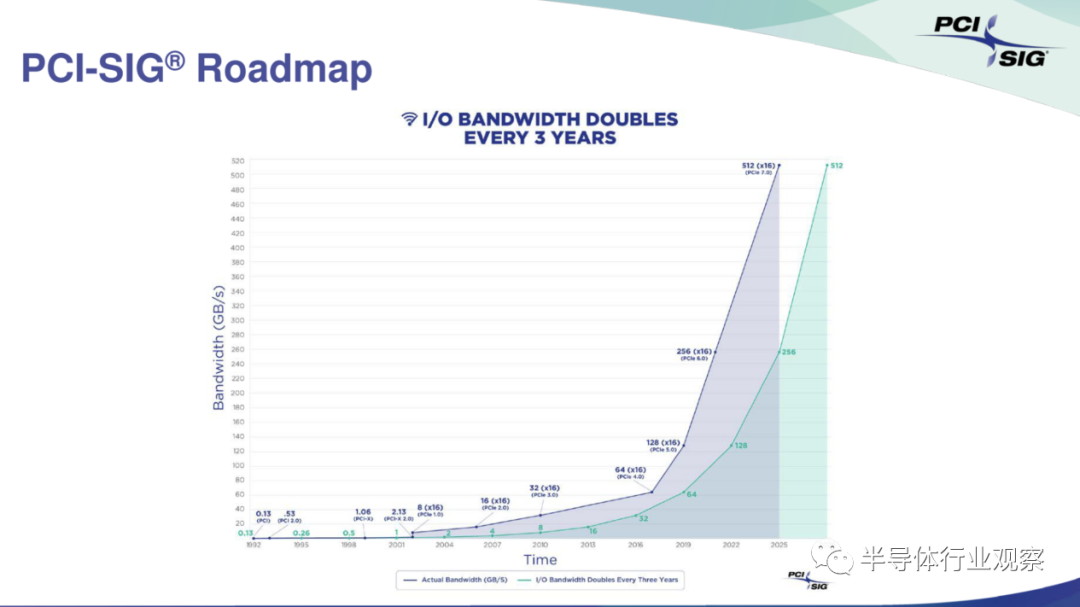

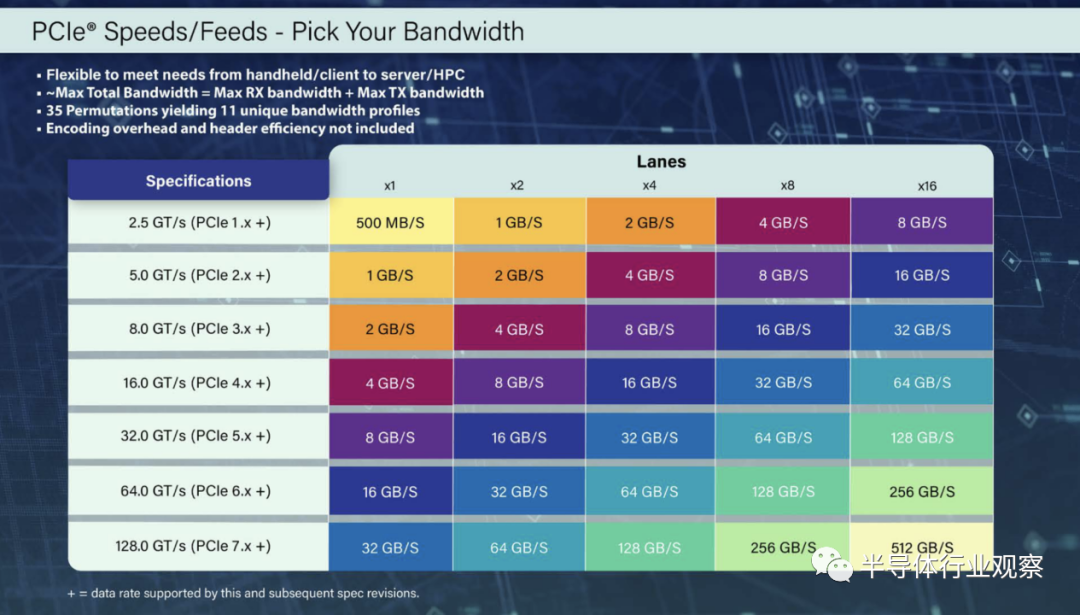

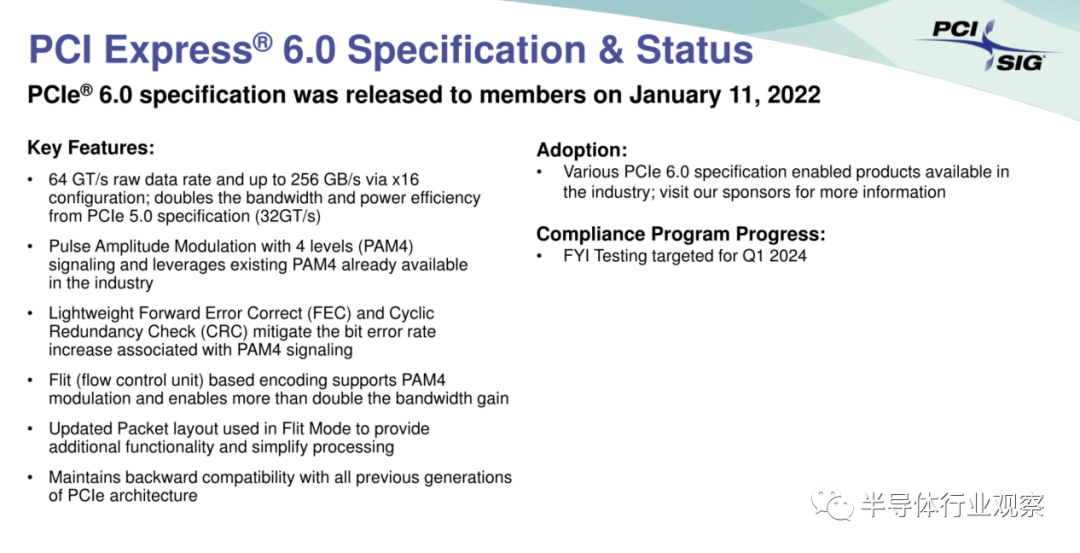

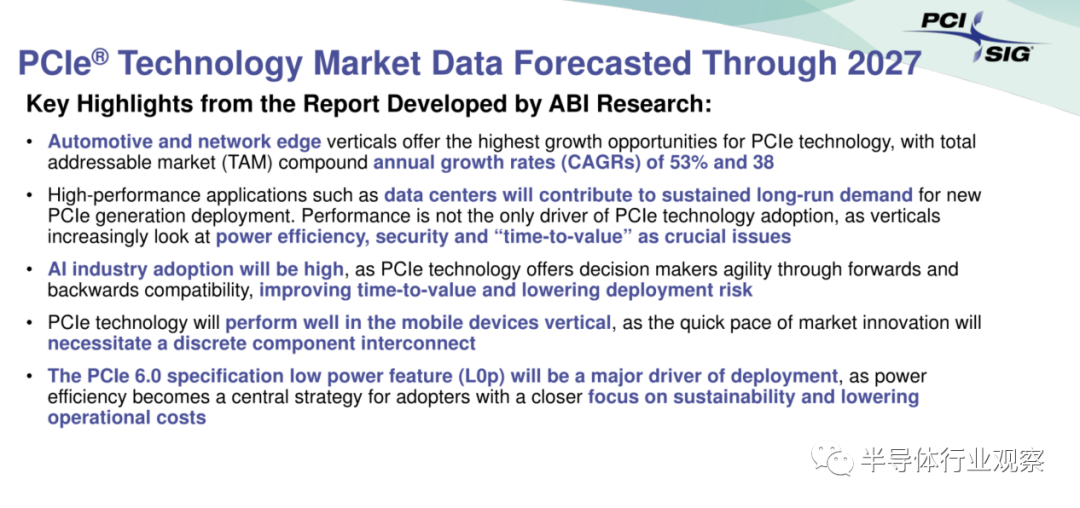

隨著PCI Express 6.0 于去年初完成,PCI-SIG 迅速開始著手開發(fā)下一代 PCIe 7.0,這在去年的開發(fā)者大會上宣布。針對 2025 年的發(fā)布,PCIe 7.0 的目標是再次將 PCIe 設(shè)備的可用帶寬量增加一倍,使單通道的全雙工雙向帶寬高達 16GB/秒——而流行的 x16 插槽在單通道中高達 256GB/秒每個方向。

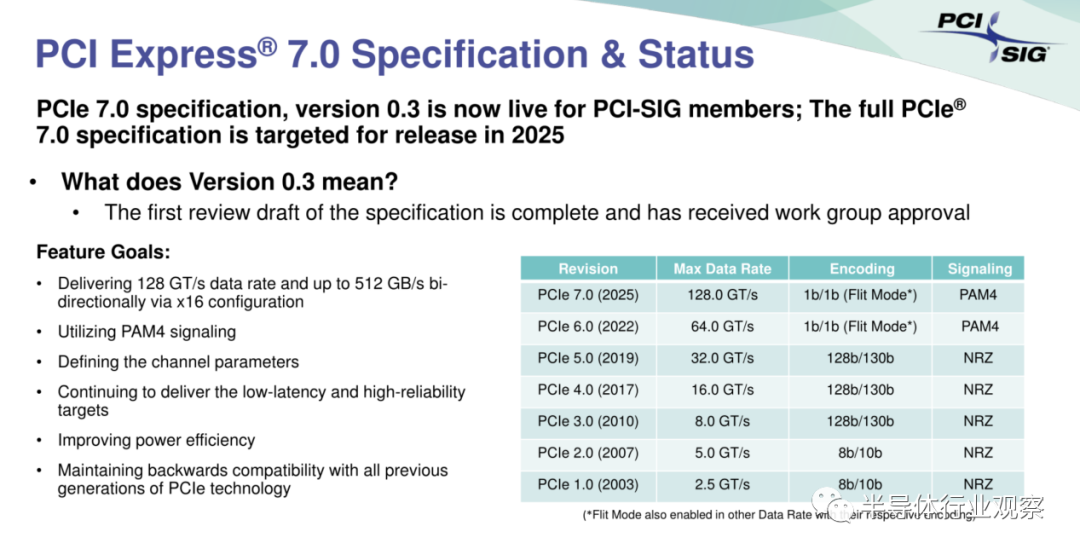

在去年發(fā)布公告時,PCIe 7.0 的早期工作才剛剛開始。對于 2023 年會議,PCI-SIG 已經(jīng)完成了規(guī)范的第一個草案版本 0.3 的發(fā)布,并準備分發(fā)給該組織的成員,這標志著該標準的下一步發(fā)展。

PCI-SIG 標準的早期草案往往不關(guān)注公共技術(shù)細節(jié),PCIe 7.0 v0.3 在這方面也不例外。因此,我們對規(guī)范本身知之甚少,而這些規(guī)范本身并沒有概述去年宣布的目標。

盡管如此,規(guī)范初稿的完成仍然很重要,因為它表明該小組已成功開發(fā)出更快的 PCIe 通信所需的核心技術(shù)基礎(chǔ)。這并非易事,因為 PCIe 7.0 需要將物理層的總線頻率加倍,這是 PCIe 6.0 使用 PAM4 信令回避的一項重大發(fā)展。即便如此,在改進數(shù)據(jù)信號方面也沒有什么是免費的,但是對于 PCIe 7.0,PCI-SIG 可以說是回到了硬模式開發(fā),需要再次改進物理層——這次是為了讓它能夠在大約30GHz。

在電氣方面,PCIe 7.0 與其前身一樣堅持使用 PAM4 + FLIT 編碼。因此,下一個標準在物理層開發(fā)上的花費,將主要用于邏輯層的開發(fā)。

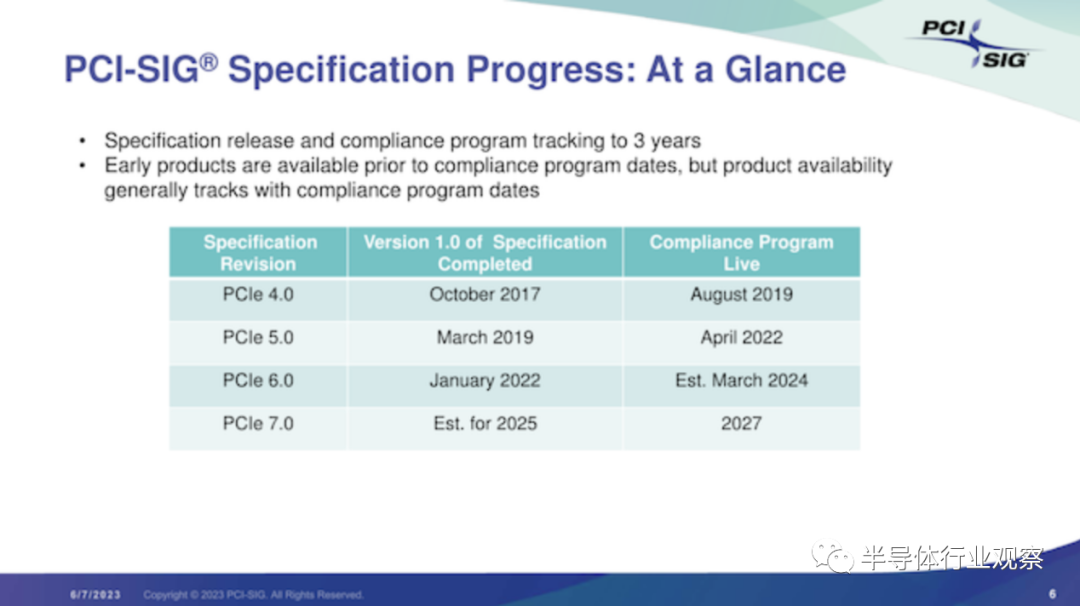

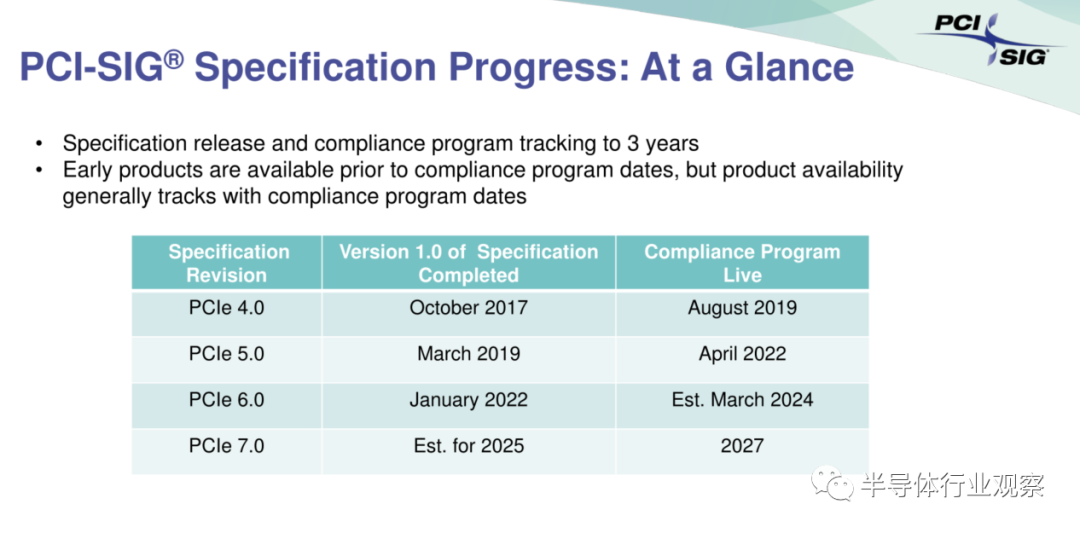

最終,PCI-SIG 的標準節(jié)奏基于三年的開發(fā)周期。因此,今年的公告草案對于該集團來說如期而至,預計它還有兩年的發(fā)展時間。假設(shè)其余的草案工作進展順利,PCI-SIG 預計將在 2025 年完成 PCIe 7.0 規(guī)范。

反過來,該規(guī)范的合規(guī)性計劃應在 2027 年啟動并運行。合規(guī)性計劃是硬件可用性的功能晴雨表,因為在使用新規(guī)范的任何大型商業(yè)硬件發(fā)貨之前,合規(guī)性測試和認證實際上是必要的. 除了少數(shù)例外,這些通常需要 2 到 2.5 年的時間才能組裝起來。所有這一切都表明,首批商用 PCIe 7.0 產(chǎn)品預計至少要到 2027 年——從現(xiàn)在起五年——這表明,在這個初始草案之后,PCIe 7.0 仍有很多工作要做。

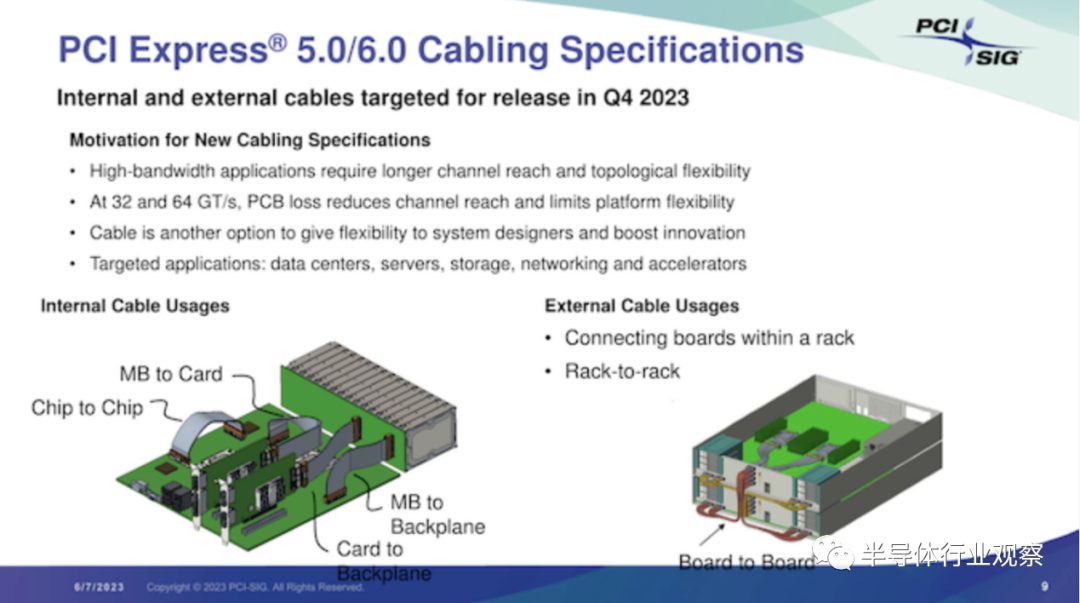

PCIe 5.0/6.0 布線將于 2023 年末推出

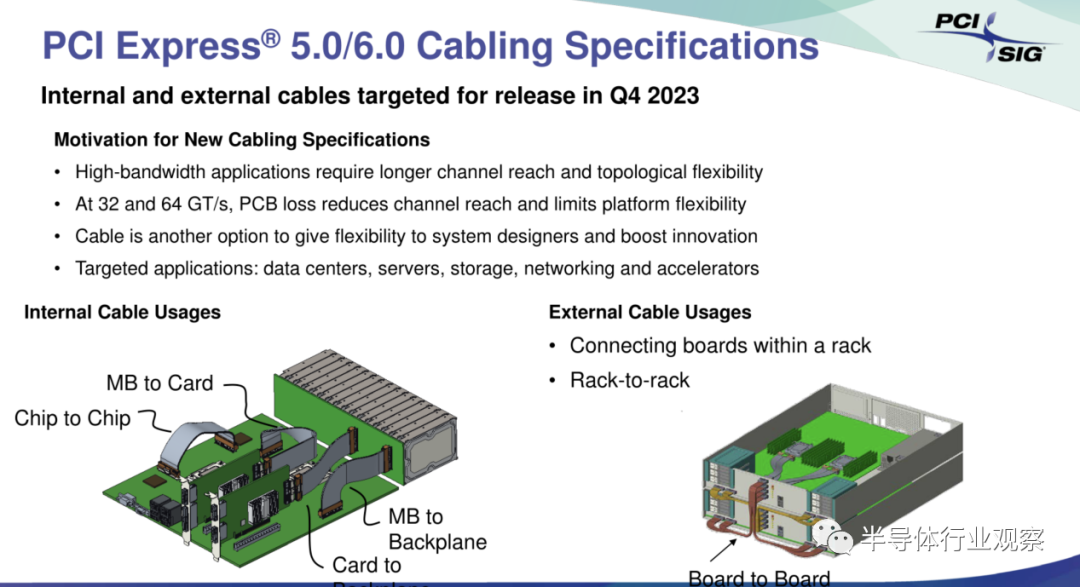

雖然 PCIe 7.0 正在開發(fā)中,但 PCIe 6.0 的第一個硬件仍在開發(fā)中,甚至 PCIe 5.0 設(shè)備也只有不到一年的時間。因此,在開發(fā)核心規(guī)范的同時,PCI-SIG 還在完成規(guī)范的一些輔助領(lǐng)域,特別是布線。

雖然我們傳統(tǒng)上首先將 PCIe 視為在印刷電路板上布線的總線,但該標準也始終允許布線。憑借其更新的標準,PCI-SIG 實際上預計在服務器和其他高端設(shè)備中布線的使用會增長,這是由于 PCB 的通道范圍限制,以及隨著信號頻率的增加而變得更糟。因此,隨著新技術(shù)和新材料正在為更好的電纜創(chuàng)造新的選擇,布線正在煥然一新,作為根據(jù)最新標準維持/擴展信道范圍的一種選擇。

為此,PCI-SIG 正在制定兩項布線規(guī)范,預計將于今年第四季度發(fā)布。規(guī)格將涵蓋 PCIe 5.0 和 PCIe 6.0(因為信號頻率不變),包括內(nèi)部和外部電纜的規(guī)格。內(nèi)部布線將把設(shè)備連接到系統(tǒng)內(nèi)的其他部分——包括設(shè)備和主板/背板——而外部布線將用于系統(tǒng)到系統(tǒng)的連接。

在信號技術(shù)和絕對信號速率方面,PCI Express 落后以太網(wǎng)一代左右。這意味著以太網(wǎng)工作組已經(jīng)解決了高速銅信號的大部分初始開發(fā)問題。因此,盡管仍需努力使這些技術(shù)適用于 PCIe,但基本技術(shù)已經(jīng)得到驗證,這有助于稍微簡化 PCIe 標準和布線的開發(fā)。

總而言之,與我們在消費者領(lǐng)域看到的相比,電纜開發(fā)無疑是該技術(shù)的更多服務器用例。但布線標準仍將是這些用例的重要發(fā)展,尤其是隨著公司繼續(xù)將更強大的系統(tǒng)和集群拼接在一起。

附:PCI-SIG 的最新進展

-

PCI

+關(guān)注

關(guān)注

5文章

678瀏覽量

131415 -

單通道

+關(guān)注

關(guān)注

0文章

392瀏覽量

18546 -

數(shù)據(jù)信號

+關(guān)注

關(guān)注

0文章

61瀏覽量

12098

原文標題:PCIe 7.0標準新進展,速度達到16GB/秒/單通道

文章出處:【微信號:Hack電子,微信公眾號:Hack電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

百度在AI領(lǐng)域的最新進展

谷歌Gemini API最新進展

華為公布AI基礎(chǔ)設(shè)施架構(gòu)突破性新進展

LPDDR4 16Gb 技術(shù)文檔詳解:SK hynix H9HCNNNBKUMLXR 規(guī)格書

上海光機所在皮秒激光器精密光同步研究方面取得新進展

PCIe 7.0 互連— PCIe的盡頭會是光嗎?

FF將發(fā)布FX品牌最新進展

Qorvo在射頻和電源管理領(lǐng)域的最新進展

pcie 4.0與pcie 5.0的區(qū)別

如何測試PCIe插槽的速度

PCIe 4.0與PCIe 3.0的性能對比

PCIe接口的工作原理 PCIe與PCI的區(qū)別

芯片和封裝級互連技術(shù)的最新進展

5G新通話技術(shù)取得新進展

新思科技PCIe 7.0驗證IP(VIP)的特性

PCIe 7.0標準新進展,速度達到16GB/秒/單通道

PCIe 7.0標準新進展,速度達到16GB/秒/單通道

評論