由于CPU、GPU、加速器和交換機的創(chuàng)新,超大規(guī)模數(shù)據(jù)中心的接口需要更快的數(shù)據(jù)傳輸,不僅在計算和內(nèi)存之間,還涉及網(wǎng)絡(luò)。PCI Express (PCIe?) 成為這些互連的基礎(chǔ),支持構(gòu)建 CXL?和 UCIe?等協(xié)議。CXL提供緩存一致性互連,支持多臺機器間的內(nèi)存擴展,提供最低延遲和最高帶寬。CXL和NVM Express?利用 PCIe 的物理層和簡便的協(xié)議適應(yīng)性。UCIe作為最新的Chiplet標準,也基于PCIe,支持可靠的數(shù)據(jù)傳輸和CXL緩存一致性。因此,PCIe 憑借其高速、低延遲和低功耗,成為處理節(jié)點之間數(shù)據(jù)傳輸?shù)臉藴省?/p>

本文討論了對PCI Express 6.0和未來標準的行業(yè)需求,合規(guī)性的重要性,如何通過 PHY 驗證成功實現(xiàn)互操作性,以及針對PCIe 6.0收發(fā)器的測量方法。Synopsys的PCI Express 6.0 IP和Tektronix的測試與測量解決方案正積極應(yīng)對這一最新的技術(shù)轉(zhuǎn)折點。

數(shù)據(jù)速率再次翻倍

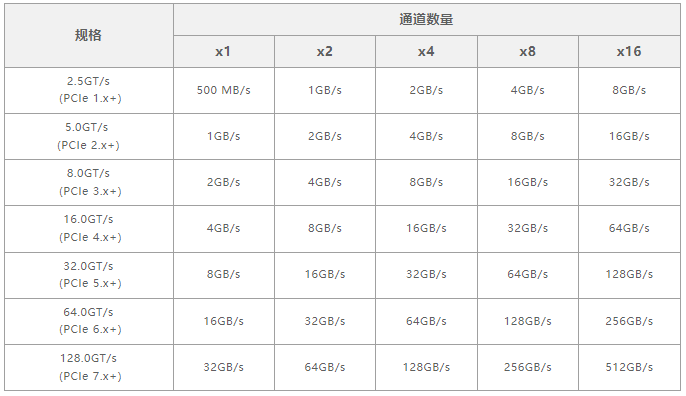

PCI-SIG? 聯(lián)盟是一個由900多家成員公司組成的開放行業(yè)標準組織,每三年發(fā)布一個新的PCIe版本。過去十年中,數(shù)據(jù)速率定期翻倍并保持完全向后兼容。PCIe 6.0.1引入 PAM4信號技術(shù),實現(xiàn)單通道64 GT/s傳輸速率,x16鏈路雙向傳輸達到256GB/s。2022年,PCI-SIG宣布了PCIe 7.0規(guī)范,將數(shù)據(jù)速率提升至128GT/s,并使用1b/1b flit編碼和PAM4信號技術(shù),在16通道下實現(xiàn)512GB/s雙向吞吐量,同時提高電源效率。除了超大規(guī)模數(shù)據(jù)中心,PCIe技術(shù)也被廣泛應(yīng)用于手持設(shè)備、服務(wù)器、汽車等領(lǐng)域,這些市場對可靠性和成本有嚴格要求,確保產(chǎn)品符合PCIe 6.0.1規(guī)范并實現(xiàn)互操作性是關(guān)鍵。

圖1:PCI-SIG各代帶寬

合理性和互操性測試

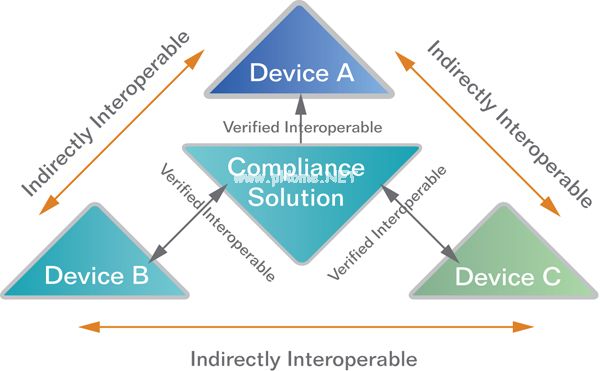

PCI-SIG的合規(guī)性和互操作性測試對于PCIe 6.0.1集成商至關(guān)重要。設(shè)計驗證、PHY驗證和合規(guī)性測試共同降低集成風險并提升產(chǎn)品質(zhì)量。PCIe系統(tǒng)有多種拓撲,涵蓋服務(wù)器、存儲、GPU托架等,所有配置需滿足16GHz奈奎斯特頻率下的32dB插入損耗預(yù)算。具體分配為Root Complex 23.5dB,Add-in card 8.5dB,其中包括PCB走線損耗和連接器預(yù)算。因主設(shè)備與最終設(shè)備間距離最小,主板可能需更高質(zhì)量的 PCB 材料和 Retimer。PCIe向后兼容性及速率升級(如64GT/s和128GT/s)增加了通道設(shè)計復雜性。

溫濕度影響可致插入損耗變化,先進PCB材料變化約±10%,主流材料約±25%。開發(fā)需考慮PHY對阻抗不連續(xù)性和PVT(工藝、電壓、溫度)變化的補償能力,通道均衡技術(shù)需適應(yīng)并持續(xù)調(diào)整以應(yīng)對環(huán)境變化,確保操作裕度。因此,與生態(tài)系統(tǒng)的廣泛互操作性驗證對確保PHY穩(wěn)健性至關(guān)重要。

用于PAM4信號的新測量方法

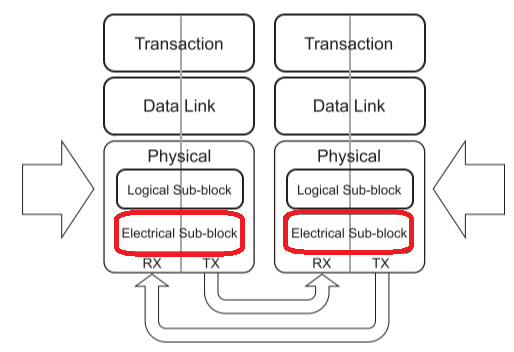

PCI Express 6.0.1基礎(chǔ)規(guī)范將PHY層劃分為邏輯子模塊和電氣子模塊(如圖2所示)。電氣子模塊的驗證是 PHY 層全面驗證的前提條件,這也是本文的重點。電氣子模塊包括發(fā)射器(Tx)、接收器(Rx)、參考時鐘(Refclk)和通道要求。支持新的64GT/s數(shù)據(jù)速率的收發(fā)器(Tx 和 Rx)還必須保持與較低速率(2.5、5.0、8.0、16.0和32.0GT/s)的向后兼容性。在6.0.1中引入的脈沖幅度調(diào)制方法(PAM4)要求有四個不同的信號級別,這允許在一個單位間隔(UI)內(nèi)傳輸兩位信息。從NRZ(兩個信號級別)到PAM4的轉(zhuǎn)換確保了通道損耗與PCIe 5.0(32GT/s)保持一致,因為這兩種速率的波特率都是32Gb/s,奈奎斯特頻率也為16GHz。

圖2:PCI Express模塊圖

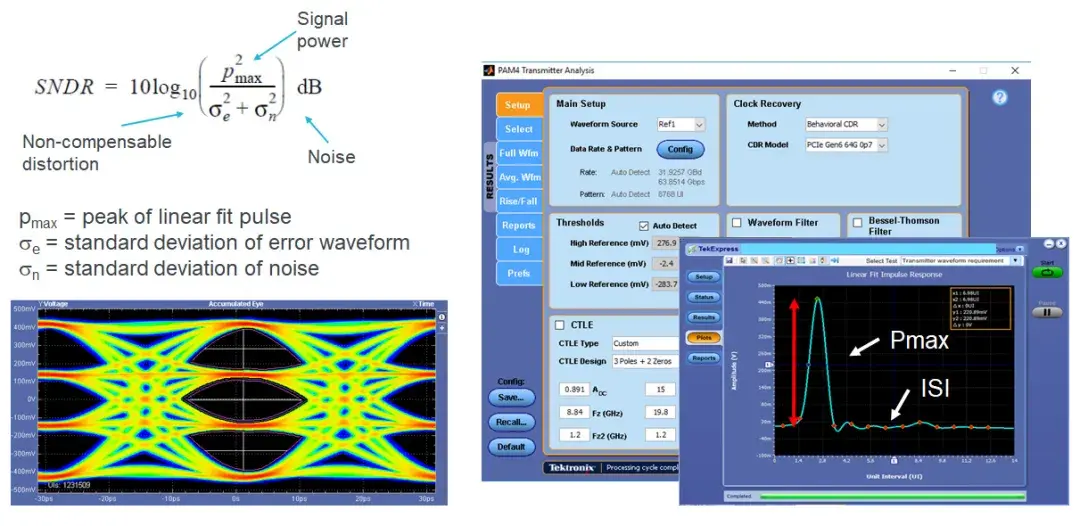

由于信號方案從NRZ變?yōu)镻AM4,垂直眼圖的開口減少了33%,因為我們從2個信號級別增加到4個信號級別。現(xiàn)在需要考慮3個眼圖,而不是單個NRZ眼圖。這種噪聲裕度的減少加劇了串擾干擾、信號反射和電源噪聲。為緩解增加的噪聲敏感性,PCIe 6.0.1還采用了格雷編碼以最小化比特錯誤,并采用預(yù)編碼來減少突發(fā)錯誤傳播。基于DAC和ADC/DSP的Tx和Rx均衡技術(shù)可以用于校正可補償?shù)膿p傷,如符號間干擾(ISI),其中相鄰比特由于通道影響(包括損耗和反射)而變得模糊不清。PCIe 6.0.1規(guī)范引入了信噪失真比(SNDR)來幫助量化這一新的設(shè)計挑戰(zhàn)。

圖3:信噪失真比 (SNDR)

SNDR建立在長期以來使用的信噪比 (SNR) 測量基礎(chǔ)之上,但引入了一個名為“σe”的變量,用于捕捉電信號中的不可補償損傷。為了簡化設(shè)計和直觀理解,我們大量依賴線性模型,這些模型只是對物理世界的近似。非線性行為確實存在于PCIe收發(fā)器和通信通道中。標準通過引入SNDR的“σe”項來捕捉這種影響。這一技術(shù)借用了IEEE標準的方法,并針對64GT/s的PCIe測量進行了定制。脈沖響應(yīng)是從 PRBS(偽隨機二進制序列)數(shù)據(jù)模式波形創(chuàng)建的,使用 IEEE 的線性擬合脈沖響應(yīng)方法,這成為確定信號幅度和“σe”的核心。準確的SNDR測量需要50GHz帶寬的實時示波器來捕捉信號,并使用DSP軟件進行波形后處理(如圖3所示)。

PAM4信號中一種預(yù)期的非線性情況發(fā)生在發(fā)射信號電平不均勻間隔時。假設(shè)靜態(tài)幅度,這將影響三個眼圖中的一個或多個,導致比特錯誤增加。在后硅驗證過程中對這種現(xiàn)象進行表征可以使收發(fā)器調(diào)整或設(shè)計更改以提高電平的線性度。為了解決這個問題,PCIe標準首次引入了電平失配比(RLM),以更好地理解和改進PAM4發(fā)射器的性能。這一基礎(chǔ)規(guī)范測量預(yù)計將在包括CEM形態(tài)的系統(tǒng)級驗證中擴展,CEM常用于顯卡和網(wǎng)絡(luò)接口卡 (NIC) 的實現(xiàn)。

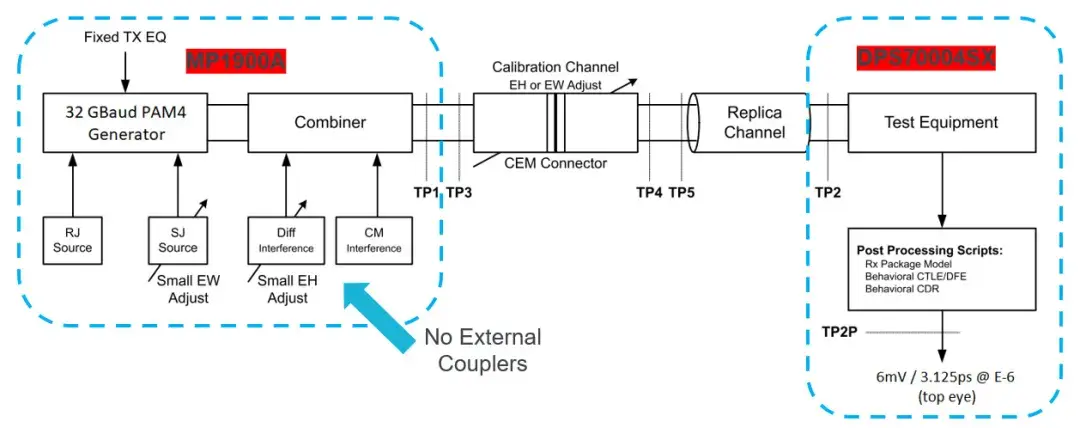

圖4:受損眼校準

從電壓到時序相關(guān)挑戰(zhàn)的過渡對在最新PCIe 6.0.1數(shù)據(jù)速率下實現(xiàn)穩(wěn)定鏈路具有重要意義。當信號從相鄰級別(例如,從電平1到電平2)過渡時的名義斜率將小于從電平0到電平3的過渡,導致更多的垂直噪聲被轉(zhuǎn)移到時序抖動中。此外,由于可能的電平過渡數(shù)量的增加,眼圖寬度固有地減小。高級測量儀器(例如實時示波器)的噪聲表征和補償技術(shù)首次被PCIe標準納入考慮,以減輕與測量相關(guān)的噪聲,并提高電壓和時序測量(例如非相關(guān)抖動)的準確性。

為PCIe 4.0和5.0接收器建立的測量方法隨著PCIe 6.0.1的Rx校準和測試得到了擴展。最差“壓力眼” 信號是使用允許的最高通道損耗創(chuàng)建的,并傳遞到被測 Rx,以量化其性能。Rx 將數(shù)字化模擬信號,然后使用回環(huán)模式從相應(yīng)的 Tx 重新發(fā)送比特流,以逐位比較來確定比特錯誤率 (BER) 或測量不同正弦抖動 (Sj) 頻率的抖動容限 (JTOL)。在64GT/s下運行的接收器需要能夠跟蹤低于10MHz的抖動增加量和高頻率下0.05 UI的抖動量。具有獨立時鐘的上下行端口時鐘架構(gòu)需要增加對33 kHz擴展頻譜時鐘 (SSC) 的容忍度。

壓力眼信號的校準是物理層驗證的復雜方面,涉及比特誤差率測試儀 (BERT)、物理通道、實時示波器 (scope) 和多個DSP軟件包。最終,這是對充當PCIe Tx的BERT脈沖模式發(fā)生器 (PPG) 的校準。圖4顯示了這個校準過程。目標是建立一個嵌入到基礎(chǔ)規(guī)范中定義的行為接收器鎖存器的眼圖,其中包括時鐘數(shù)據(jù)恢復器 (CDR) 和行為接收器均衡器。通過調(diào)整通道損耗、噪聲和抖動來實現(xiàn)目標眼圖,允許的頂部眼高度和眼寬度范圍被找到。通道調(diào)整帶來的符號間干擾 (ISI) 對眼圖提供了最大的調(diào)整,而正弦抖動 (Sj) 和使用差模干擾的串擾作為微調(diào)機制。業(yè)界越來越依賴軟件自動化來理解和實現(xiàn)接收器測試的壓力眼校準。

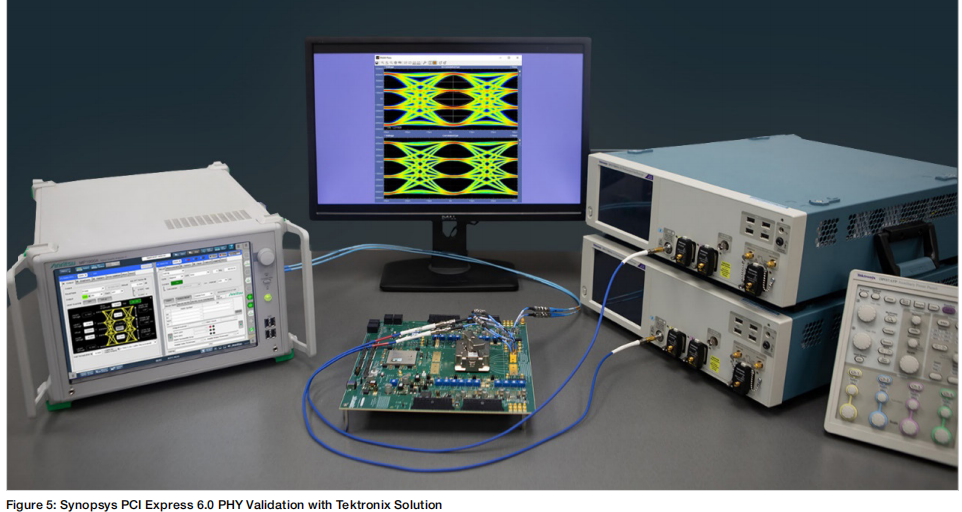

圖5:使用Tektronix解決方案進行Synopsys PCI Express 6.0 PHY 驗證

PCIe 6.0 解決方案

互操作性仍然是PCIe技術(shù)成功的支柱,推動了新興技術(shù)(如 CXL)的廣泛普及和采用,并被納入未來的Chiplet(die-to-die)設(shè)計中,例如 UCIe。實現(xiàn)互操作性始于IP設(shè)計或選擇,并涉及在基礎(chǔ)規(guī)范和系統(tǒng)級別的測試,以確保來自不同供應(yīng)商的設(shè)備能夠正確建立鏈路并在不同的工作電壓和溫度下保持穩(wěn)定。還必須考慮可制造性產(chǎn)品的可實現(xiàn)良率。例如,為了驗證Synopsys的PCI Express 6.0 IP,本文所述的測試設(shè)置包括Tektronix的DPS77004SX示波器、Tektronix 的測試自動化軟件以及Anritsu MP1900A BERT(如圖5所示)。

Synopsys提供了涵蓋該標準所有代數(shù)的完整PCI Express控制器、PHY和驗證IP解決方案,這些解決方案已在客戶產(chǎn)品中得到硅驗證,目標應(yīng)用包括重定時器、閃存控制器、加速器、SSD U.2/U.3、PCIe交換機和智能NIC。Synopsys IP已實現(xiàn)多次成功的第三方互操作性。Tektronix提供了一個完整的PCI Express 6.0基礎(chǔ)Tx/Rx自動化解決方案,并向下兼容較低的數(shù)據(jù)速率和特定外形的測試。

審核編輯 黃宇

-

PCI

+關(guān)注

關(guān)注

5文章

678瀏覽量

131418 -

PCIe

+關(guān)注

關(guān)注

16文章

1322瀏覽量

84656 -

PHY

+關(guān)注

關(guān)注

2文章

314瀏覽量

52478

發(fā)布評論請先 登錄

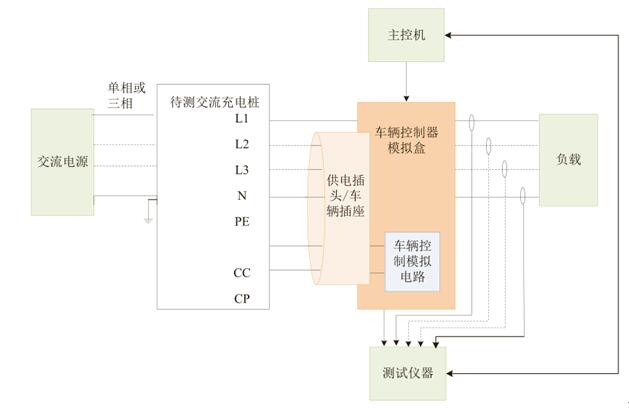

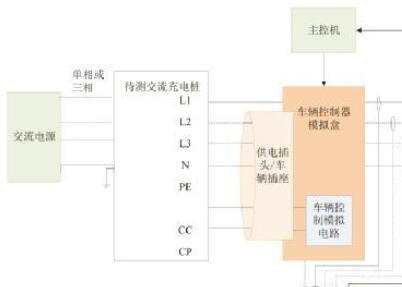

淺析交流充電樁的互操作性測試標準

10-Gbps以太網(wǎng)MAC和XAUI PHY互操作性硬件演示參考設(shè)計(PDF)中的說明進行操作

基于XML的現(xiàn)場總線設(shè)備互操作性研究

PCIe:緩和一致性與互操作性挑戰(zhàn)

交流充電樁的互操作性測試標準

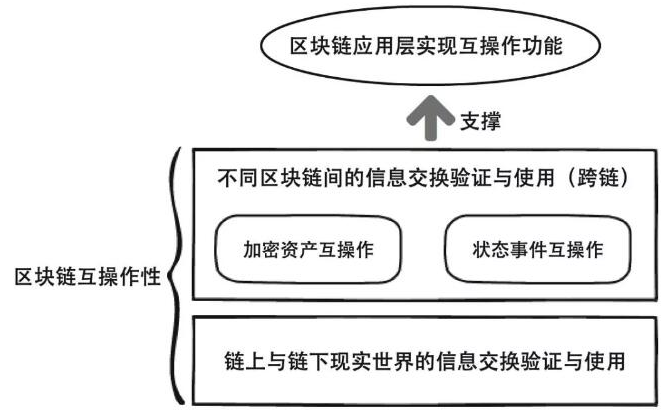

區(qū)塊鏈互操作性的三個類別

區(qū)塊鏈互操作性是什么

驗證ADI轉(zhuǎn)換器與Xilinx FPGA和JESD204B/C IP的互操作性

驗證ADI轉(zhuǎn)換器與Xilinx FPGA和JESD204BC IP的互操作性

PCIe 6.0 互操作性PHY驗證測試方案

PCIe 6.0 互操作性PHY驗證測試方案

評論