ICP(Inductively Coupled Plasma,電感耦合等離子體)刻蝕技術(shù)是半導體制造中的一種關(guān)鍵干法刻蝕工藝,廣泛應用于先進集成電路、MEMS器件和光電子器件的加工。以下是關(guān)于ICP刻蝕技術(shù)的詳細介紹:

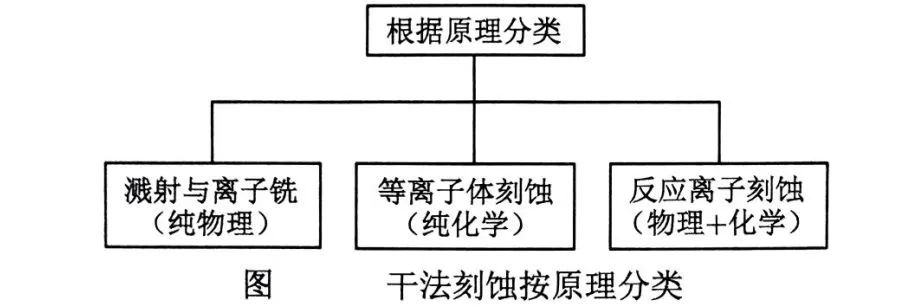

1. ICP刻蝕的基本原理

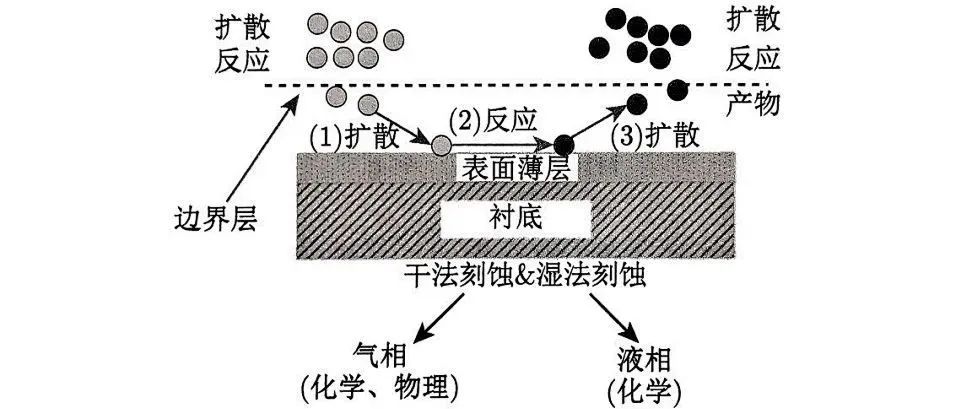

ICP刻蝕通過電感耦合方式產(chǎn)生高密度等離子體,利用物理和化學作用去除襯底材料。其核心過程包括:

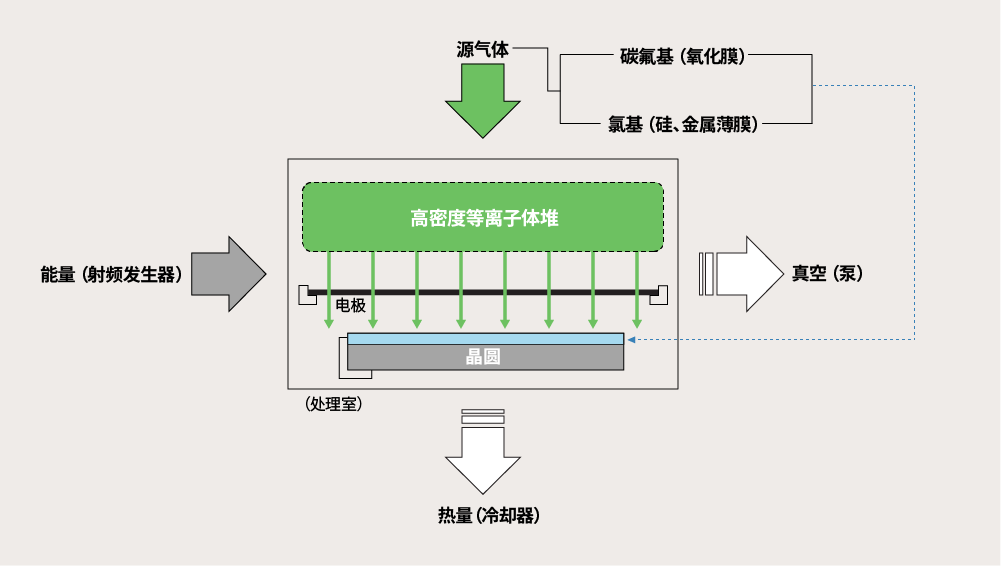

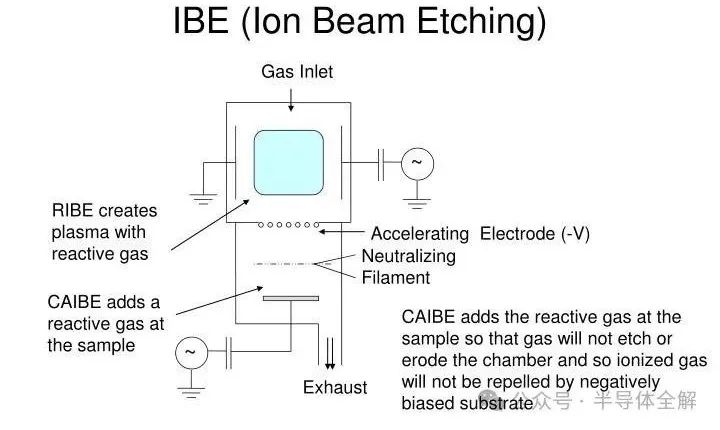

等離子體生成:通過射頻(RF)線圈在真空腔體內(nèi)產(chǎn)生強電場,電離氣體(如CF?、SF?、Cl?等)形成高濃度的等離子體。

活性粒子轟擊:等離子體中的離子和自由基與襯底表面發(fā)生化學反應(如氟基氣體蝕硅生成SiF?),同時離子物理轟擊增強刻蝕方向性。

副產(chǎn)物排出:反應生成的揮發(fā)性物質(zhì)(如SiF?、CO?等)由真空系統(tǒng)抽離腔體。

2. ICP刻蝕設(shè)備的核心結(jié)構(gòu)

ICP設(shè)備主要由以下部分組成:

真空腔體:容納晶圓和等離子體反應區(qū)域,通常由耐蝕材料(如鋁或石英)制成。

射頻(RF)源:

ICP線圈(通常為13.56 MHz):產(chǎn)生電感耦合等離子體。

偏壓電極(通常為低頻RF或直流):控制離子轟擊能量和方向性。

氣體分配系統(tǒng):精確調(diào)節(jié)蝕刻氣體(如SF?、Cl?)和惰性載氣(如Ar)的流量。

溫度控制系統(tǒng):維持晶圓溫度穩(wěn)定,避免過熱損傷。

3. ICP刻蝕的關(guān)鍵特點

高深寬比:通過調(diào)控離子轟擊能量和化學腐蝕速率,實現(xiàn)深孔、窄縫等高深寬比結(jié)構(gòu)的刻蝕(如TSV、FinFET鰭片)。

各向異性:離子垂直轟擊襯底,側(cè)向腐蝕極小,圖形邊緣陡峭。

高精度控制:可獨立調(diào)節(jié)等離子體密度、離子能量、氣體成分等參數(shù),適應不同材料和結(jié)構(gòu)需求。

選擇性刻蝕:通過選擇合適的氣體和工藝參數(shù),優(yōu)先蝕刻目標材料(如硅、金屬),保護掩膜層(如光刻膠或硬質(zhì)掩膜)。

4. ICP刻蝕的主要應用領(lǐng)域

集成電路制造:

晶體管結(jié)構(gòu)(如多晶硅柵極、源漏極)。

金屬互連層的通孔、溝槽刻蝕。

三維集成中的穿透硅通孔(TSV)。

MEMS器件:

硅基懸空結(jié)構(gòu)(如加速度計、陀螺儀的空氣懸架)。

深槽刻蝕(如微流體通道、腔體)。

光電子器件:

Ⅲ-Ⅴ族化合物(如GaAs、InP)的圖形化。

5. ICP刻蝕的工藝參數(shù)與調(diào)控

氣體類型與流量:

氟基氣體(如SF?、CF?):用于硅或金屬的化學腐蝕。

氯基氣體(如Cl?、BCl?):常用于氧化物或金屬刻蝕。

惰性氣體(如Ar):調(diào)節(jié)離子轟擊強度。

射頻功率:

ICP功率:影響等離子體密度和反應速率。

偏壓功率:控制離子轟擊能量和方向性。

溫度與壓力:低溫利于減少熱損傷,低氣壓可提升等離子體均勻性。

刻蝕時間:決定刻蝕深度,需與停止層或自動檢測結(jié)合防止過刻。

審核編輯 黃宇

-

ICP

+關(guān)注

關(guān)注

0文章

75瀏覽量

13142 -

刻蝕

+關(guān)注

關(guān)注

2文章

202瀏覽量

13327

發(fā)布評論請先 登錄

一文詳解濕法刻蝕工藝

半導體boe刻蝕技術(shù)介紹

半導體制造關(guān)鍵工藝:濕法刻蝕設(shè)備技術(shù)解析

最全最詳盡的半導體制造技術(shù)資料,涵蓋晶圓工藝到后端封測

中微公司ICP雙反應臺刻蝕機Primo Twin-Star取得新突破

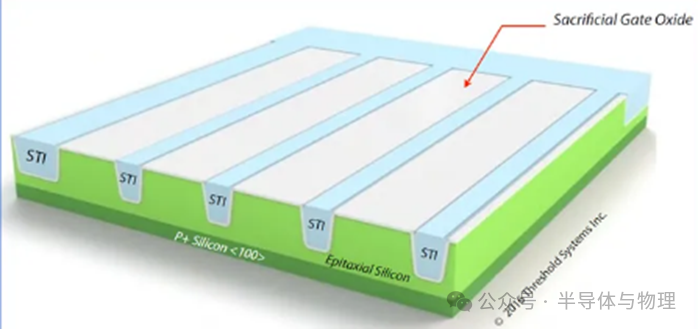

芯片制造中的淺溝道隔離工藝技術(shù)

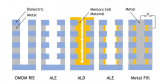

ALD和ALE核心工藝技術(shù)對比

深入剖析半導體濕法刻蝕過程中殘留物形成的機理

半導體濕法刻蝕殘留物的原理

半導體濕法和干法刻蝕

半導體濕法刻蝕設(shè)備加熱器的作用

半導體芯片制造技術(shù)之干法刻蝕工藝詳解

半導體刻蝕工藝技術(shù)-icp介紹

半導體刻蝕工藝技術(shù)-icp介紹

評論