半導體BOE(Buffered Oxide Etchant,緩沖氧化物蝕刻液)刻蝕技術(shù)是半導體制造中用于去除晶圓表面氧化層的關(guān)鍵工藝,尤其在微結(jié)構(gòu)加工、硅基發(fā)光器件制作及氮化硅/二氧化硅刻蝕中廣泛應用。以下是其技術(shù)原理、組成、工藝特點及發(fā)展趨勢的詳細介紹:

一、技術(shù)原理

BOE刻蝕液是一種以氫氟酸(HF)和氟化銨(NH?F)為基礎(chǔ)的緩沖溶液,通過化學腐蝕作用去除半導體表面的氧化層(如SiO?、SiN?)。其核心反應機制包括:

氟化物離子攻擊:

氟化銨(NH?F)提供F?離子,與氧化層中的硅原子(如SiO?)反應,生成可溶的氟硅化合物(如SiF?2?)。

反應式:

SiO2+4F?→SiF4?+2O2?

緩沖作用:

氟化銨作為緩沖劑,維持溶液的pH穩(wěn)定,避免氫氟酸過度反應導致蝕刻速率過快或不均勻。

選擇性刻蝕:

BOE對不同材料的蝕刻速率差異顯著(如SiO?快于SiN?),通過調(diào)整配方可實現(xiàn)高精度圖形化。

二、BOE刻蝕液組成

基礎(chǔ)成分:

氫氟酸(HF):提供F?離子,主導氧化層蝕刻。

氟化銨(NH?F):緩沖劑,調(diào)節(jié)pH并穩(wěn)定反應速率。

超純水:溶劑,控制溶液濃度和黏度。

添加劑:

表面活性劑:降低溶液表面張力,改善潤濕性(如聚乙二醇辛基苯基醚、氟碳類表面活性劑)。

消泡劑:抑制蝕刻過程中氣泡產(chǎn)生(如磷酸酯類、聚醚類消泡劑)。

納米粒子:填充蝕刻后表面孔洞(如環(huán)氧基改性納米碳、納米氮化硼),提升材料均勻性。

三、工藝特點

優(yōu)勢:

高選擇性:對氧化層(如SiO?)蝕刻速率快,對底層材料(如硅基底)損傷小。

均勻性好:緩沖體系避免局部反應劇烈,適合大面積或深孔結(jié)構(gòu)(如3D NAND孔洞)。

環(huán)保性:相比純HF溶液,BOE廢液處理更簡單,部分配方可回收利用。

挑戰(zhàn):

表面張力高:傳統(tǒng)BOE潤濕性差,需添加表面活性劑改善鋪展性。

顆粒污染:蝕刻副產(chǎn)物可能重新沉積,需結(jié)合兆聲波清洗或超純水沖洗。

復雜微觀表面處理:需優(yōu)化添加劑以提高對深孔、高深寬比結(jié)構(gòu)的滲透能力。

四、應用場景

氧化層去除:

光刻膠剝離后清洗殘留的SiO?層,為后續(xù)金屬鍍膜或刻蝕做準備。

氮化硅刻蝕:

用于MEMS傳感器、功率器件中的SiN?層圖形化,需調(diào)整BOE配方以適配不同蝕刻速率。

先進制程:

3D NAND閃存的垂直孔洞刻蝕、GAA晶體管的高深寬比結(jié)構(gòu)加工。

五、技術(shù)改進與趨勢

配方優(yōu)化:

添加納米粒子(如改性納米碳、氮化硼)填充蝕刻孔洞,減少表面缺陷。

開發(fā)低表面張力的復合表面活性劑,提升潤濕性與均勻性。

設備集成:

全自動BOE蝕刻機(如蘇州芯矽電子設備)集成高精度定位、封閉式腔體設計,防止揮發(fā)與污染。

實時監(jiān)測系統(tǒng)(如光學終點檢測)控制蝕刻深度,避免過度腐蝕。

環(huán)保與節(jié)能:

低濃度HF配方減少危廢處理壓力,能源回收系統(tǒng)降低運行成本。

BOE刻蝕技術(shù)通過化學緩沖體系實現(xiàn)精準氧化層去除,是半導體制造中不可或缺的工藝。其發(fā)展方向聚焦于配方優(yōu)化(如納米添加劑、環(huán)保型表面活性劑)、設備智能化(如自動化控制與終點檢測)以及高效環(huán)保(如廢液回收與低能耗設計)。隨著制程進步(如3nm以下節(jié)點),BOE技術(shù)需進一步提升選擇性、均勻性和微小結(jié)構(gòu)處理能力,以滿足先進器件的需求。

審核編輯 黃宇

-

半導體

+關(guān)注

關(guān)注

335文章

28489瀏覽量

231514 -

刻蝕

+關(guān)注

關(guān)注

2文章

201瀏覽量

13313 -

BOE

+關(guān)注

關(guān)注

0文章

141瀏覽量

8608

發(fā)布評論請先 登錄

半導體刻蝕工藝技術(shù)-icp介紹

半導體制造關(guān)鍵工藝:濕法刻蝕設備技術(shù)解析

最全最詳盡的半導體制造技術(shù)資料,涵蓋晶圓工藝到后端封測

深入剖析半導體濕法刻蝕過程中殘留物形成的機理

半導體濕法刻蝕殘留物的原理

半導體濕法和干法刻蝕

濕法刻蝕步驟有哪些

半導體濕法刻蝕設備加熱器的作用

中國半導體的鏡鑒之路

半導體封裝技術(shù)的類型和區(qū)別

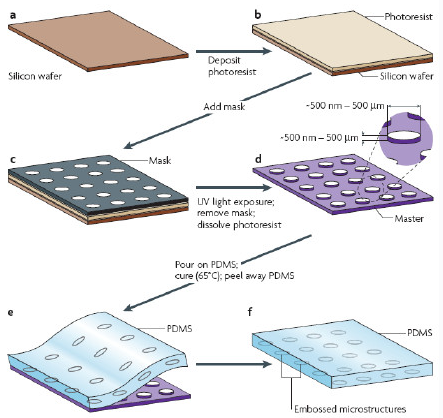

微流控芯片加工中的PDMS軟刻蝕技術(shù)和聚合物成型介紹

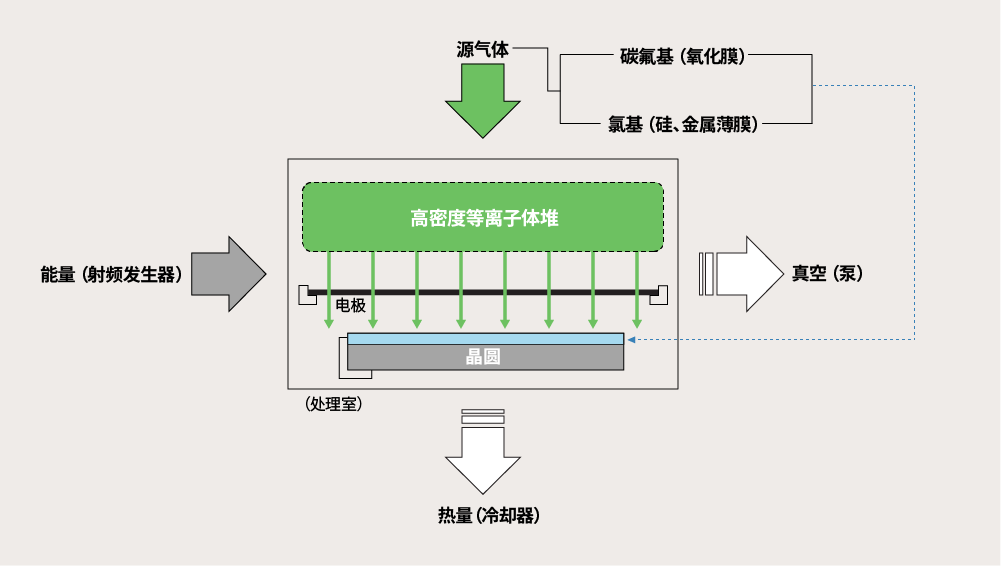

半導體芯片制造技術(shù)之干法刻蝕工藝詳解

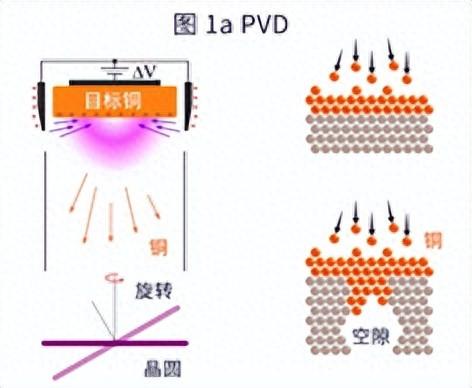

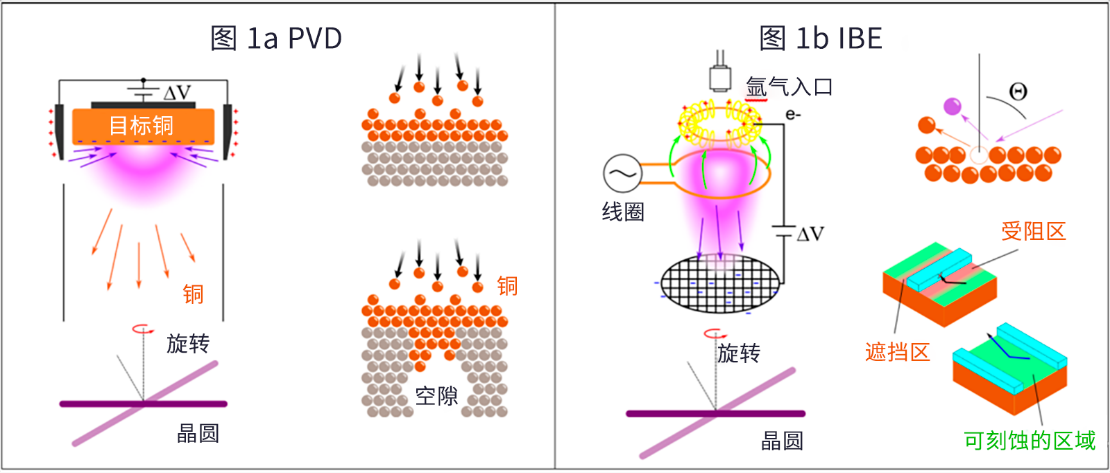

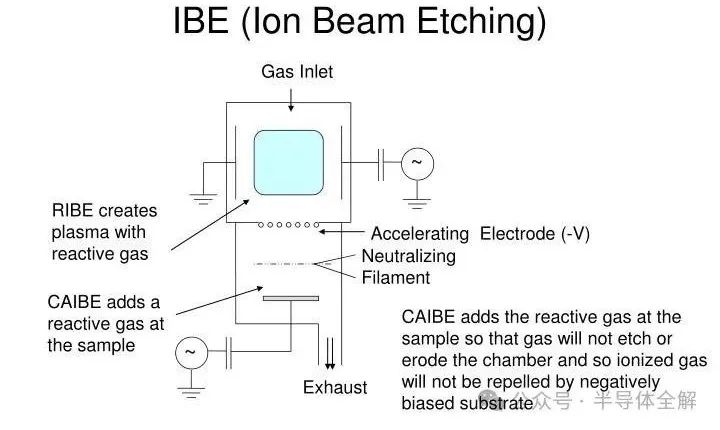

降低半導體金屬線電阻的沉積和刻蝕技術(shù)

降低半導體金屬線電阻的沉積和刻蝕技術(shù)

半導體boe刻蝕技術(shù)介紹

半導體boe刻蝕技術(shù)介紹

評論