作者:泛林集團 Semiverse Solutions 部門軟件應用工程師 Timothy Yang 博士

01 介紹

銅的電阻率由其晶體結構、空隙體積、晶界和材料界面失配決定,并隨尺寸縮小而顯著提升。通常,銅線的制作流程是用溝槽刻蝕工藝在低介電二氧化硅里刻蝕溝槽圖形,然后通過大馬士革流程用銅填充溝槽。但這種方法會生出帶有明顯晶界和空隙的多晶結構,從而增加銅線電阻。為防止大馬士革退火工藝中的銅擴散,此工藝還使用了高電阻率的氮化鉭內襯材料。

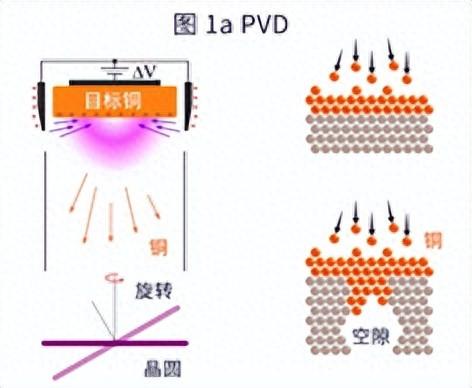

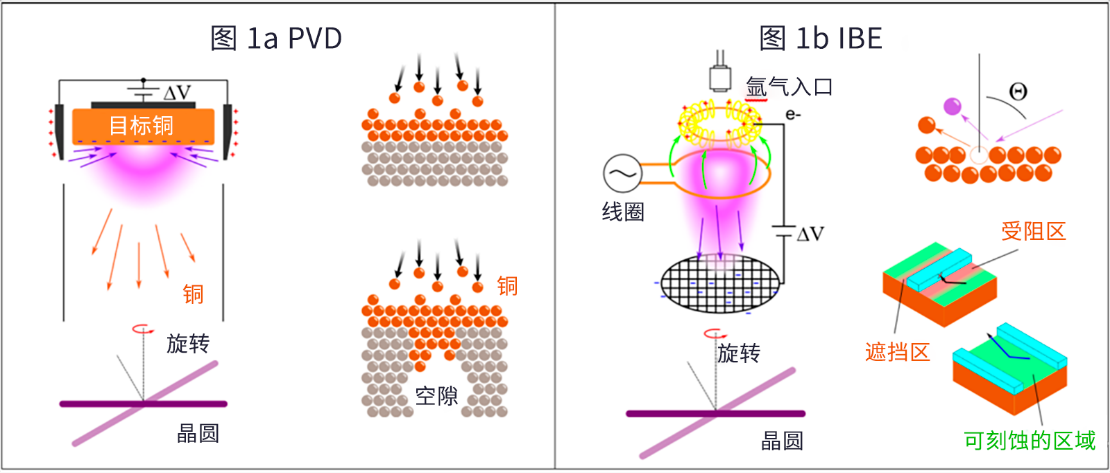

我們可以使用物理氣相沉積 (PVD) 以10至100電子伏特的高動能沉積銅,得到電阻低、密度高的單晶結構。但PVD的局限在于覆蓋性比較差,且只能在平面上均勻沉積,不能用于填充深孔或溝槽(圖1a)。

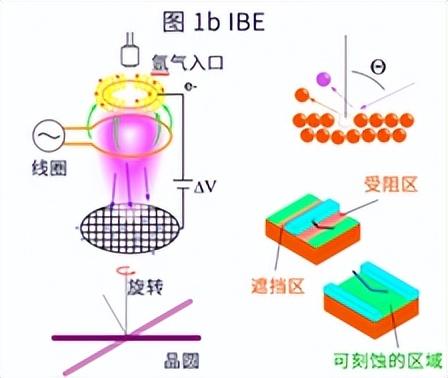

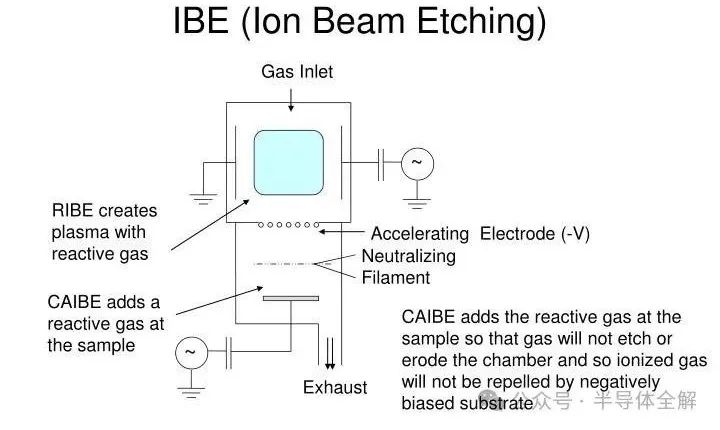

要得到獨立的金屬線,首先需要在平面上沉積均勻的銅層,隨后用離子束進行物理刻蝕。銅與活性氣體不產生揮發性化合物,因此不能使用反應離子刻蝕工藝。如果入射角非常高,離子束刻蝕 (IBE) 中產生的加速氬離子可以去除銅。但由于掩膜結構的遮擋效應,可刻蝕的區域將會受限。圖1b展示了當掩膜垂直于入射離子束時的不可刻蝕區域(紅色),這是由于掩膜遮擋導致的原子噴射路徑受阻所造成的。當掩膜與離子路徑平行時,所有未被掩蓋的區域都能被刻蝕。因此,IBE僅限于刻蝕任意長度的線形掩膜。

02 工藝步驟與虛擬制造工藝

為了解沉積與刻蝕對線電阻的影響,我們使用SEMulator3D?可視性沉積和刻蝕功能模擬PVD和IBE工藝。借助SEMulator3D,我們使用30°分散角的可視性沉積工藝再現PVD,該流程準確模擬出轟擊中噴射出的銅原子與氬離子的隨機狀態。同時,我們使用2°分散角與60°傾斜角的可視性刻蝕模擬出IBE,實現以較低的離子束發散反映網格加速離子的行為。兩個模擬都將晶圓視為在工藝過程中自由旋轉,并為適應IBE和PVD的局限之處,對其他工藝步驟進行了調整。圖2展示了使用大馬士革銅填充工藝(圖2a)和PVD/IBE工藝(圖2b)創建出的相同結構。為適應PVD/IBE的某些局限之處,并為所需的最終結構創建相同的形狀,我們還加入了額外的工藝步驟。

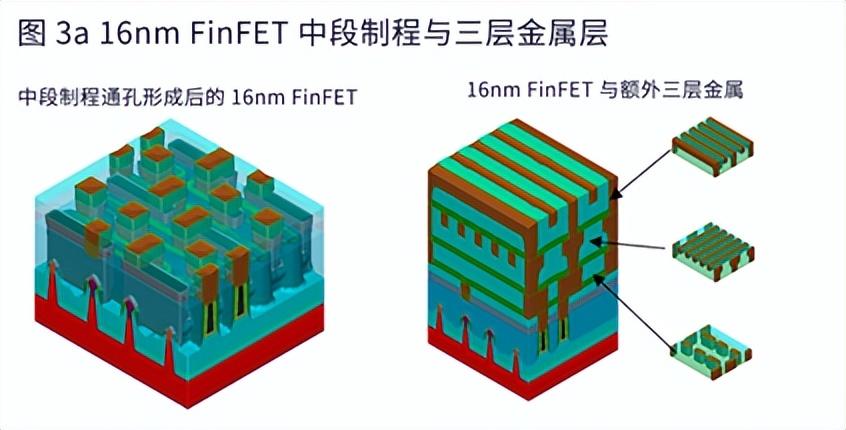

實驗證明,即使存在這些局限,依然可以用PVD/IBE線制造出同等的16nm SRAM(靜態隨機存取存儲器)電路單元。所有線路中段以上的金屬層都在平面上制作,所以它優于FinFET(鰭式場效應晶體管)器件復雜的互連拓撲結構,是PVD/IBE金屬線的可選方案。圖3展示了每個金屬層的獨立結構,以及使用PVD/IBE制作三層金屬FinFET結構的必要步驟。

圖3a和b展示了每個金屬層的獨立結構,以及使用PVD/IBE創建三層金屬FinFET結構的必要步驟。

l 圖3a:左圖展示成型的中段制程16nm FinFET結構,右圖展示具有三個完整金屬層的FinFET結構。中段制程之后表面是平坦的,銅PVD和IBE可以在該步驟進行。

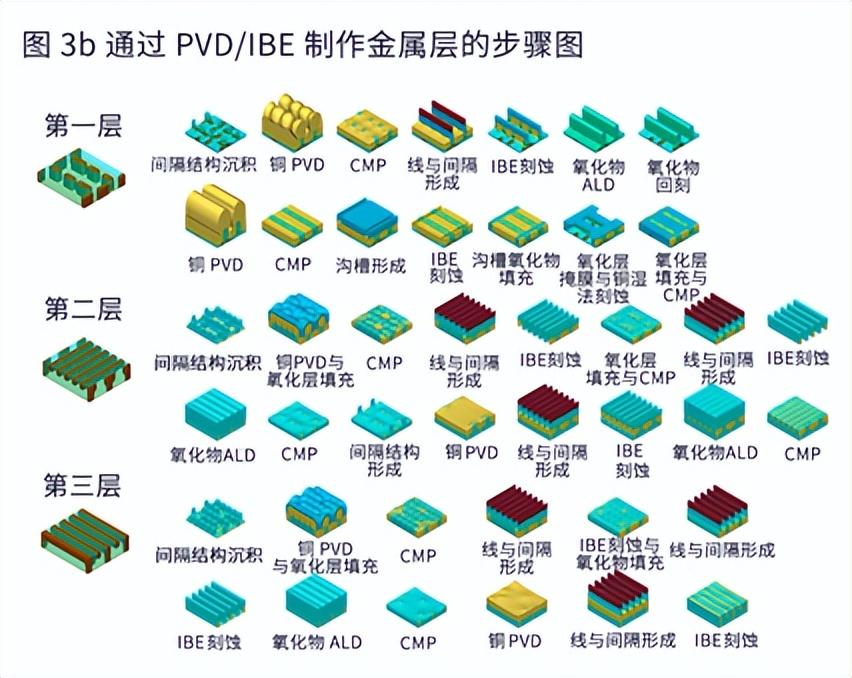

l 圖 3b:該圖展示了用PVD/IBE制造每個金屬層的步驟,并演示出在PVD和IBE存在局限的情況下為制造三個金屬層探索工藝和集成路徑的過程。每層都有相應配圖分步解析制造流程,且都部分涉及柱狀結構形成、銅PVD、化學機械拋光(CMP)、線與間隔的形成、氧化物填充、IBE刻蝕、原子層沉積 (ALD)、銅PVD及其他圖示的獨立工藝步驟。

為形成分隔開的金屬線,需要制造間隔和臺面充當絕緣阻擋層。磨平沉積物后,可以進行線和間隔的圖形化,以及X或Y方向上的任意長度刻蝕,從而制造對應方向的線。在制造通孔時,可進行交叉刻蝕,避免X和Y方向的線掩膜交叉受到刻蝕。不需要通孔的區域則可在金屬沉積前覆蓋絕緣間隔結構。

03 電阻結果與結論

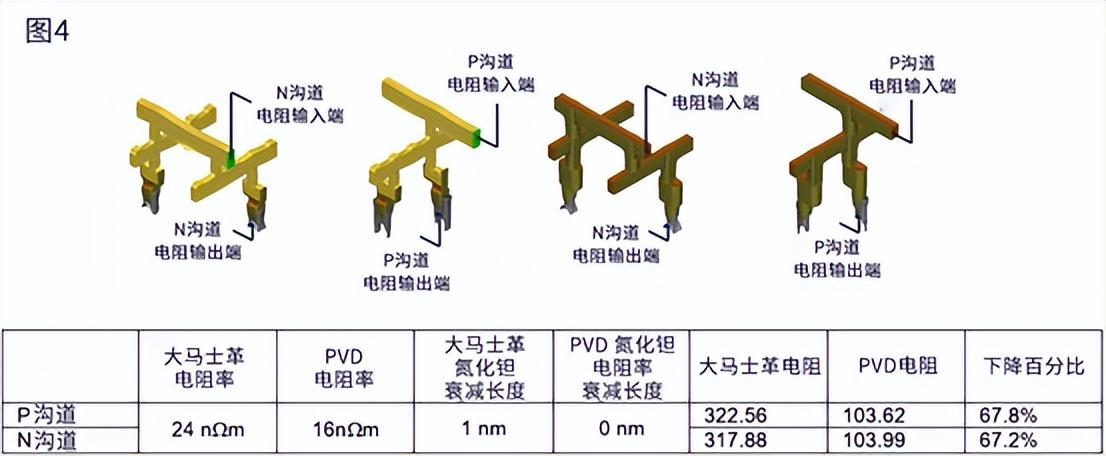

隨后,我們測量了大馬士革流程和PVD兩種工藝下,最頂層金屬到FinFET結構P和N溝道通孔的線電阻。圖4展示P和N通道電阻測量的起點和終點(其他所有絕緣材料透明)。為彌補氮化鉭內襯層和銅線間的接觸電阻,計算銅電阻時我們考慮了電子的表面散射效應,離氮化鉭界面越近,銅電阻率越高,電阻率的衰減長度設置為1nm。因為大馬士革填充銅沉積預計不是全晶,所以銅的電阻率提升50%。PVD/IBE銅工藝不使用氮化鉭內襯層,因此未應用指數衰減函數,并在此模型中使用了銅的體電阻率。圖4包含大馬士革流程與PVD的電阻率比較表格。

圖4展示了采用大馬士革流程和PVD工藝的FinFET器件3D模型圖,這些模型畫出P和N溝道的電阻測量點。3D模型下方的表格比較了P和N溝道的大馬士革和PVD電阻值。表格顯示,相比大馬士革沉積,使用IBE/PVD可降低67%的電阻。

從模型計算得出的電阻值表明,與傳統的溝槽刻蝕+大馬士革沉積方法相比,采用IBE/PVD制造方法可使電阻降低67%。這是因為IBE/PVD不需要氮化鉭內襯層,且該過程中銅線電阻率較低。該結果表明,在金屬線制造過程中,與大馬士革填充相比,IBE/PVD可以降低電阻率,但代價是制造工藝更為復雜。

【近期會議】

10月30-31日,由寬禁帶半導體國家工程研究中心主辦的“化合物半導體先進技術及應用大會”將首次與大家在江蘇·常州相見,邀您齊聚常州新城希爾頓酒店,解耦產業鏈市場布局!https://w.lwc.cn/s/uueAru

11月28-29日,“第二屆半導體先進封測產業技術創新大會”將再次與各位相見于廈門,秉承“延續去年,創新今年”的思想,仍將由云天半導體與廈門大學聯合主辦,雅時國際商訊承辦,邀您齊聚廈門·海滄融信華邑酒店共探行業發展!誠邀您報名參會:https://w.lwc.cn/s/n6FFne

聲明:本網站部分文章轉載自網絡,轉發僅為更大范圍傳播。 轉載文章版權歸原作者所有,如有異議,請聯系我們修改或刪除。聯系郵箱:viviz@actintl.com.hk, 電話:0755-25988573

審核編輯 黃宇

-

半導體

+關注

關注

335文章

28918瀏覽量

237942 -

刻蝕

+關注

關注

2文章

206瀏覽量

13414

發布評論請先 登錄

揭秘半導體電鍍工藝

半導體boe刻蝕技術介紹

最全最詳盡的半導體制造技術資料,涵蓋晶圓工藝到后端封測

半導體薄膜沉積技術的優勢和應用

深入剖析半導體濕法刻蝕過程中殘留物形成的機理

半導體濕法刻蝕殘留物的原理

【「大話芯片制造」閱讀體驗】+ 芯片制造過程和生產工藝

半導體濕法和干法刻蝕

半導體濕法刻蝕設備加熱器的作用

降低半導體金屬線電阻的沉積和刻蝕技術

降低半導體金屬線電阻的沉積和刻蝕技術

降低半導體金屬線電阻的沉積和刻蝕技術

評論