文章來源:半導體與物理

原文作者:jjfly686

淺溝道隔離(STI)是芯片制造中的關鍵工藝技術,用于在半導體器件中形成電學隔離區域,防止相鄰晶體管之間的電流干擾。本文簡單介紹淺溝道隔離技術的作用、材料和步驟。

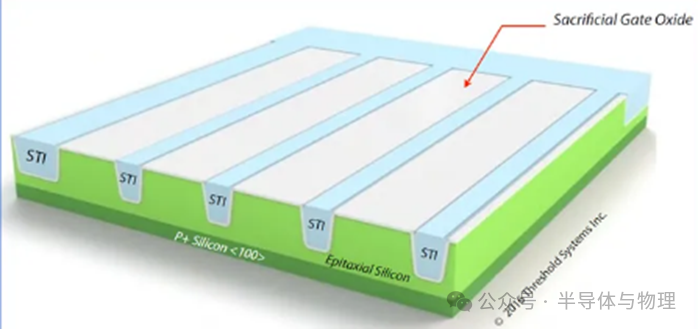

淺溝道隔離(STI)是芯片制造中的關鍵工藝技術,用于在半導體器件中形成電學隔離區域,防止相鄰晶體管之間的電流干擾。其核心是在硅襯底上刻蝕出淺層溝槽,并填充絕緣材料(如二氧化硅),從而將不同晶體管或電路模塊分隔開。例如,PMOS和NMOS晶體管通過STI結構實現物理隔離,避免因載流子聚集導致的漏電問題。

淺溝道隔離的作用

電氣隔離:防止相鄰器件間的電流串擾,提升芯片穩定性。

降低漏電:通過優化溝槽底部的內襯層結構,減少載流子聚集,避免漏電。

提升性能:采用多級溝槽設計(如寬度逐級遞減)可增加柵極溝道寬度,降低電阻,增強電流驅動能力。

工藝兼容性:與CMOS工藝高度兼容,適用于高密度集成電路制造。

淺溝道隔離的材料

STI結構的材料分為多個功能層:

| 層次 | 材料 | 功能描述 |

|---|---|---|

| 襯底材料 | 單晶硅片 Si | 提供基礎支撐 |

| 熱氧化層 | 二氧化硅SiO? | 在溝槽側壁和底部生長,鈍化表面缺陷 |

| 內襯層 | 氮化硅 SiN | 增強隔離效果,底部去除以防止載流子聚集 |

| 填充材料 | 氧化硅 SiO? | 使用SOD旋涂工藝填充溝槽,確保無空隙 |

淺溝道隔離的制程工藝

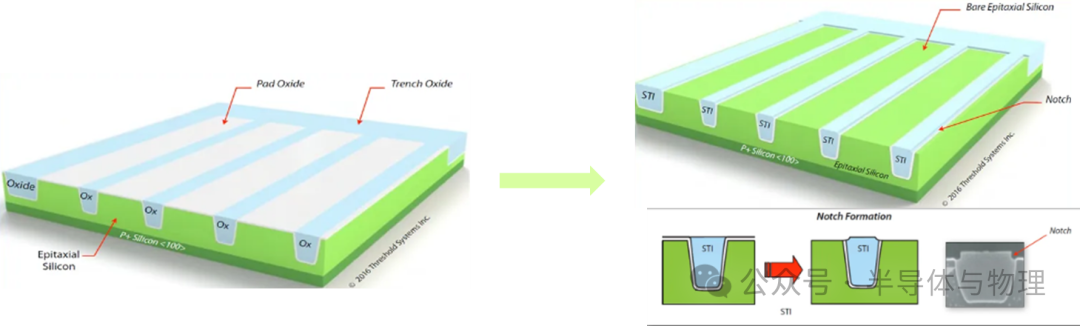

STI工藝主要包含以下核心步驟(圖2a-2d):

1. 溝槽刻蝕

在硅襯底上通過光刻和干法刻蝕形成淺溝槽(深度通常為0.2-0.5μm)。

2. 熱氧化層生長

在溝槽內壁生長一層SiO?(約10-20nm),修復刻蝕損傷并降低界面態密度。

3. 內襯層沉積與處理

沉積氮化硅等材料作為內襯,隨后選擇性去除溝槽底部的內襯層,避免漏電。

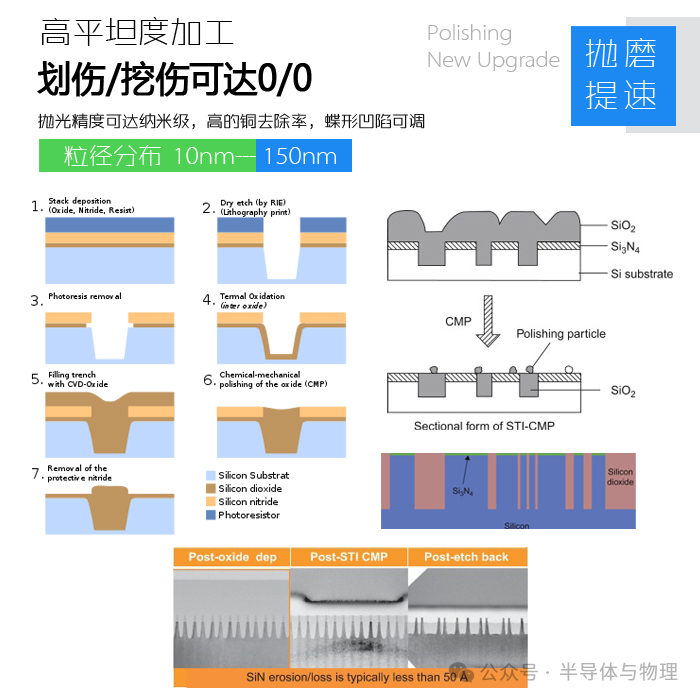

4. 高密度等離子體氧化物填充

使用SOD旋涂填充SiO?,之后進行回火工藝固化SiO?。

5. 化學機械拋光(CMP)

去除表面多余的氧化物,使硅片表面平坦化,為后續工藝(如柵極制作)做準備。

-

半導體

+關注

關注

335文章

28880瀏覽量

237440 -

晶體管

+關注

關注

77文章

10018瀏覽量

141586 -

芯片制造

+關注

關注

10文章

687瀏覽量

29712 -

工藝技術

+關注

關注

0文章

19瀏覽量

9659

原文標題:淺溝道隔離(STI)

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Sic mesfet工藝技術研究與器件研究

半導體工藝技術的發展趨勢

半導體工藝技術的發展趨勢是什么?

剛柔性PCB制造工藝技術的發展趨勢

ADI完成制造工藝技術的升級,有效提高晶圓制造效率

SONNET中的工藝技術層介紹

芯片制造中的淺溝道隔離工藝技術

芯片制造中的淺溝道隔離工藝技術

評論