離子植入制程是改變半導體電學特性非常重要的一個方式。

IMP的主要好處:

注入的摻雜離子不受靶材溶解度的限制,靈活多樣

精確控制

橫向擴散不嚴重

大面積均勻性

純度高同時也是相對低溫過程

化合物半導體的應用(第三代半導體)使得更加有價值

離子植入的基本要求:Ion Implantation: 1.精確的注入離子數量 2.精確的注入到靶內部的深度與分布 3.精確控制晶圓上注入的位置 4.完成注入后的晶格恢復與激活 離子植入需要知道的重點: 離子射程與濃度分布,通道效應與陰影效應,電子中和,快速退火 按以下的方式逐步展開:

?半導體的重要性質:可控制性

?P型半導體/N型半導體的基本原理與半導體應用場景

?離子注入的發展歷史

?離子注入機的基本運行原理

?離子注入方式:摻雜物種類/注入濃度/節深

?離子注入額外的問題:電荷中和/退火 RTA

展開敘述: ?半導體的重要性質:可控制性

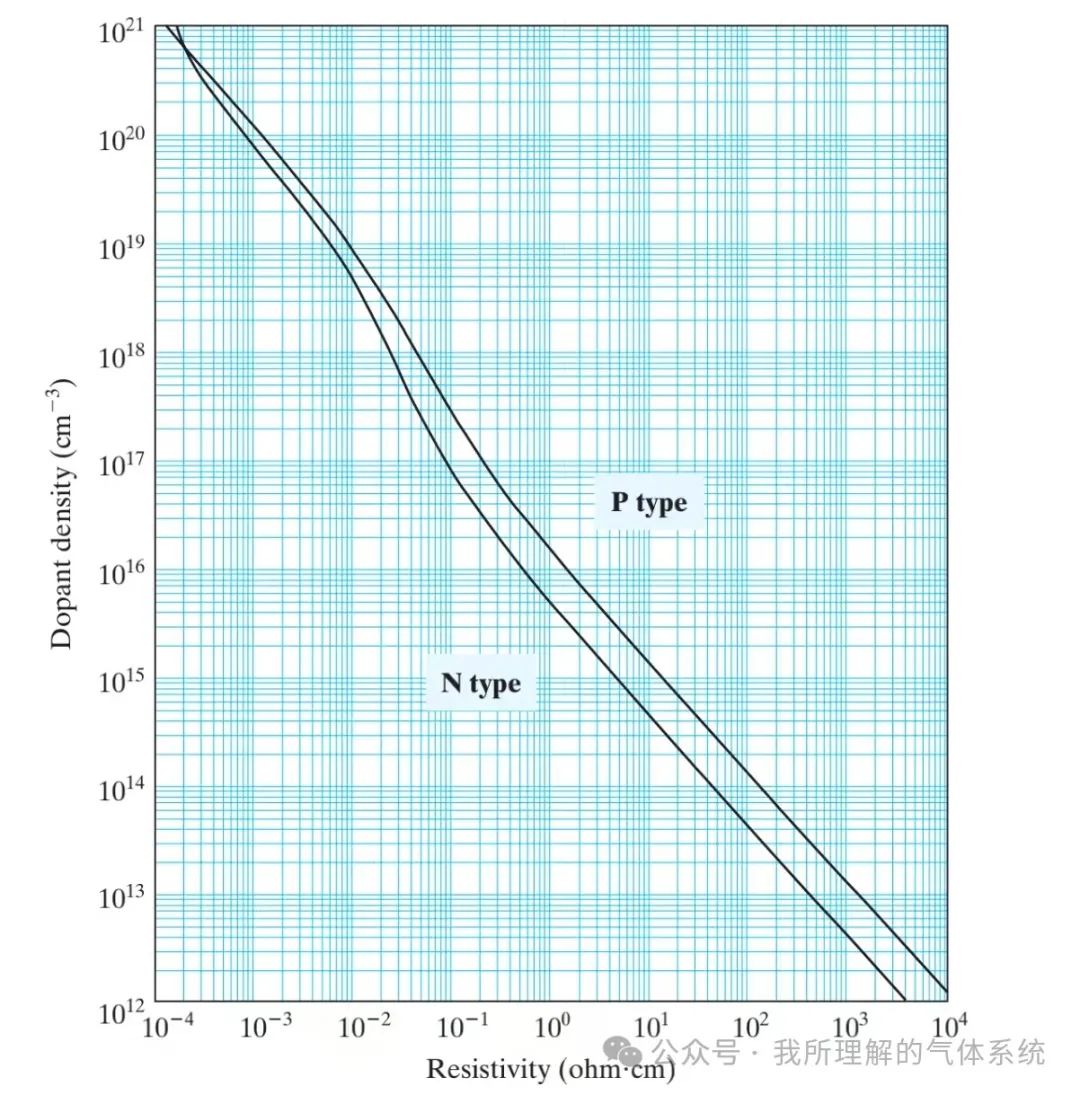

半導體材料為什么比絕緣體/導體更有優勢,一個重要的原因是半導體材料可以通過精確摻雜其他原子改變自身的電阻率即導電特性,人為控制電阻率 是半導體材料非常優良的特點

例如:室溫下,300K, 一百萬個Si原子中摻雜1個磷原子

電阻變化:

214000歐姆/厘米 降至 0.2歐姆/厘米,6個數量級的差距

故摻雜使用的氣體流量比較小,MFC選型比較小,少量的摻雜原子即可產生巨大的變化

?P型半導體/N型半導體的基本原理與半導體應用場景

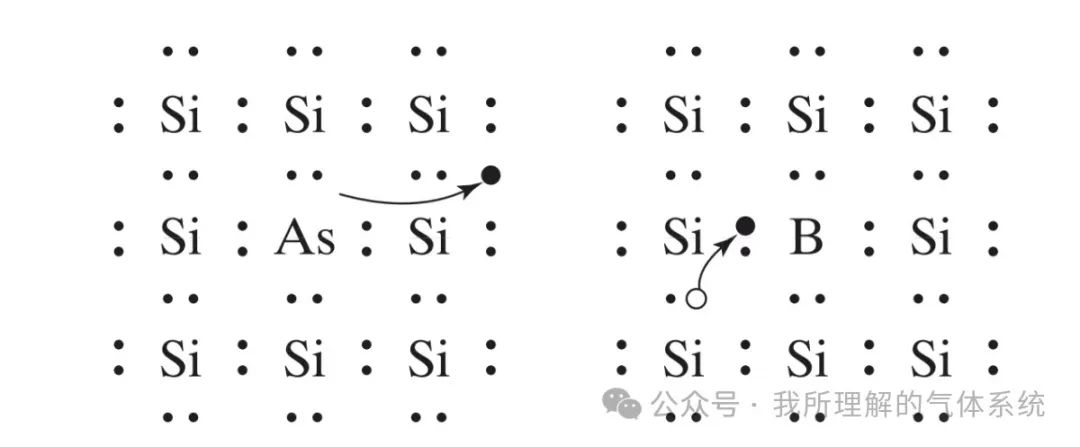

純的半導體材料通過摻雜不同的原子可形成2種類型的半導體:

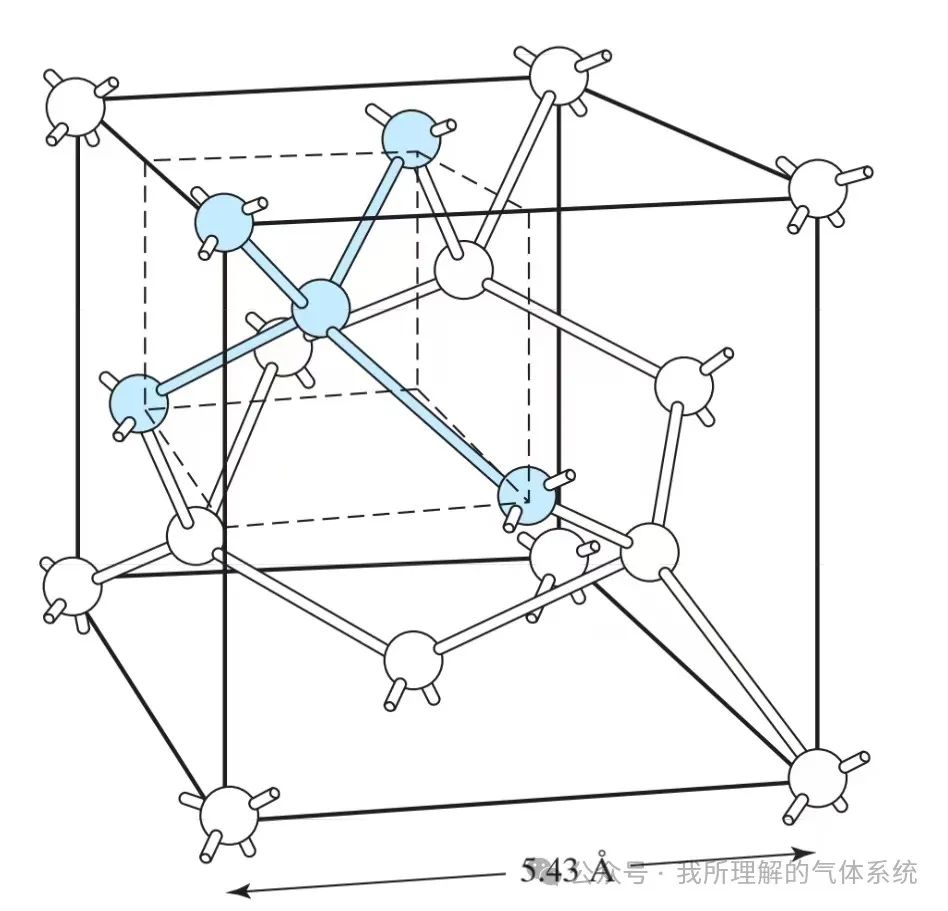

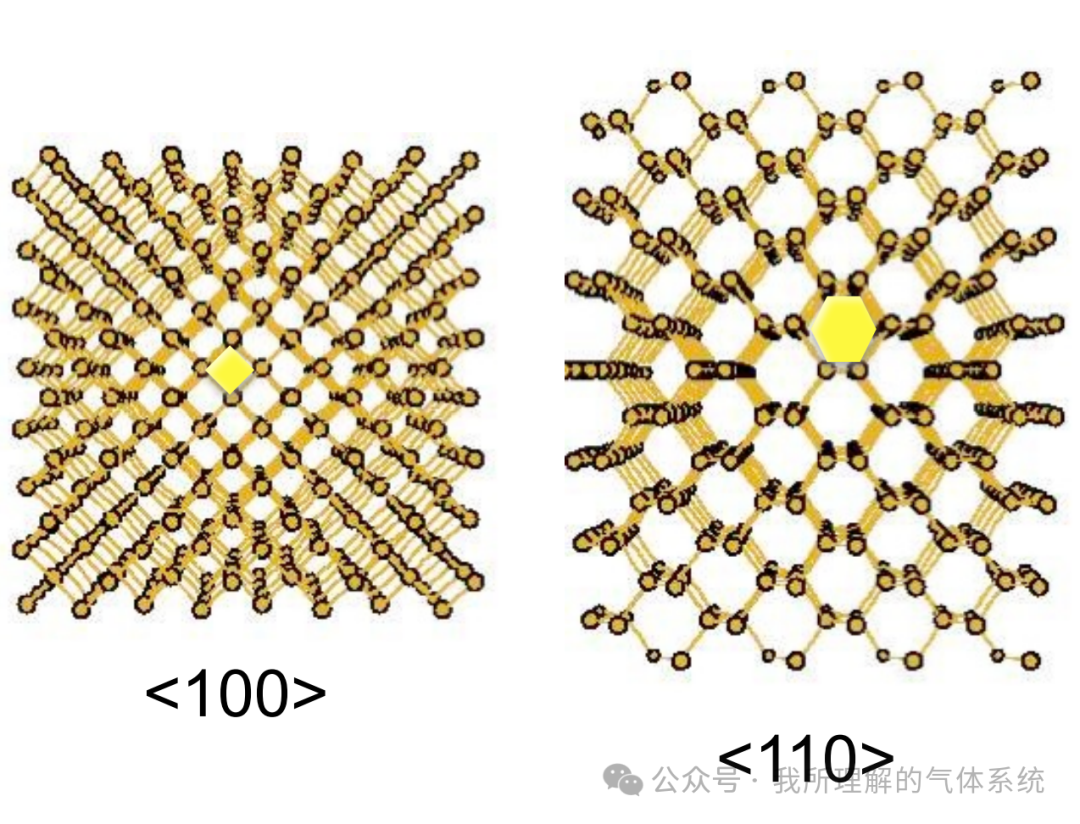

P型半導體:Positive,空穴作為載流子,N型半導體:Negative,電子作為載流子 Si的原子結構:并不是平面分布,這在離子注入的通道效應得到說明

當摻雜As或者B后:多出的電子或者空穴可以充當載流子。載流子相關性質與摻雜濃度之間的關系,可以參閱半導體物理

如何把原子注入到半導體固體材料中呢? 工業上,已廣泛采用離子注入(Ion Implantation)

離子注入可以認為是純物理過程,使用模型進行理論分析可以較為精準的預測,同時也意味著理解那些公式將非常具有挑戰性

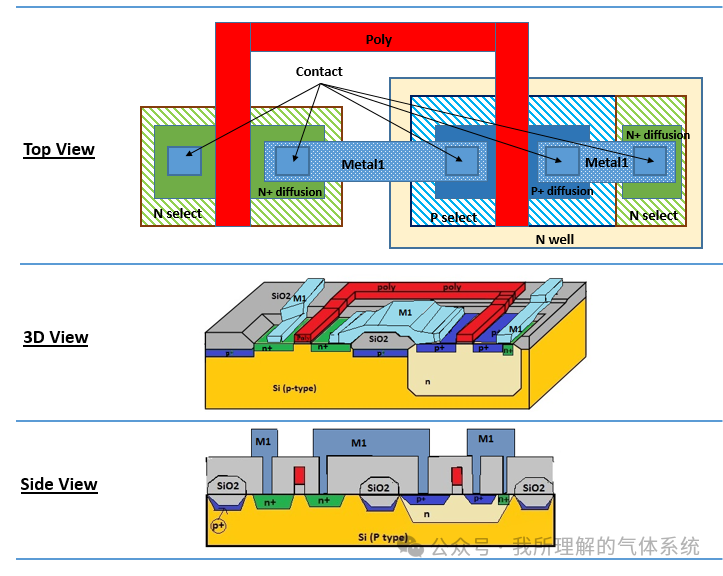

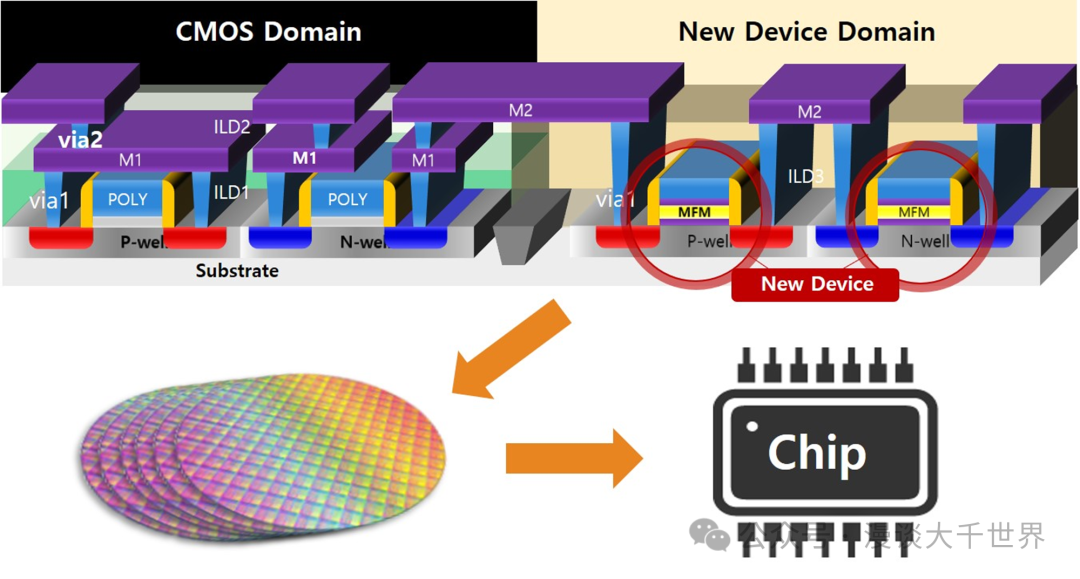

前已解釋過CMOS反相器的工作原理,CMOS是重要的半導體器件,器件需要很多的PN結,制作這些P/N型區域采用IMP工藝

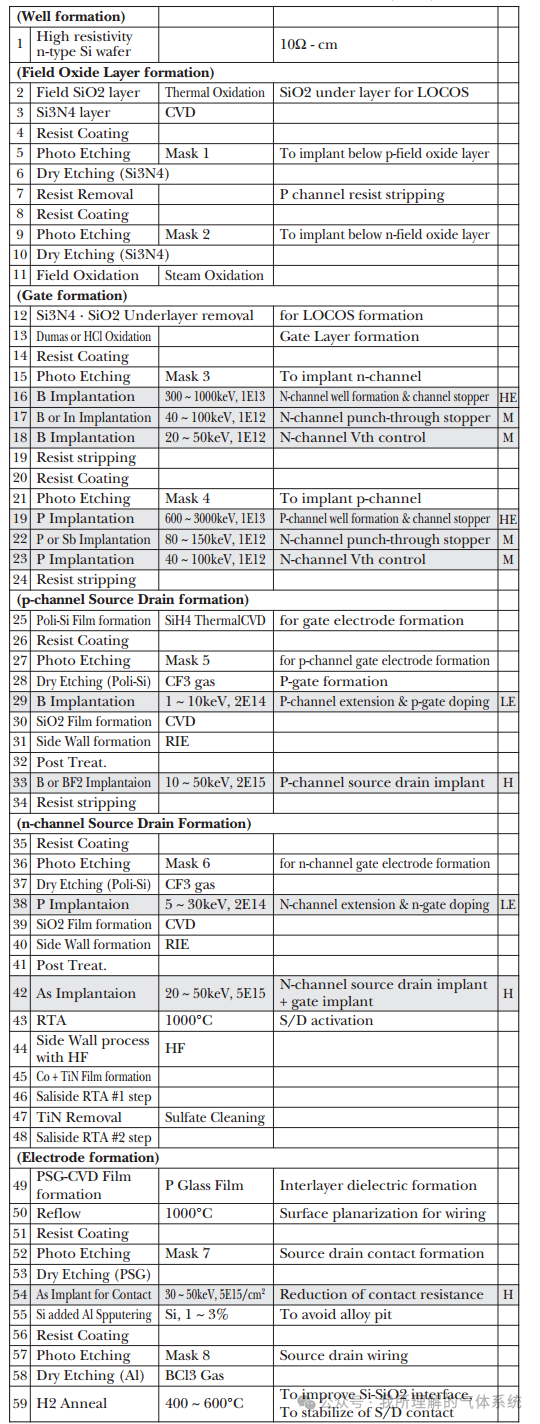

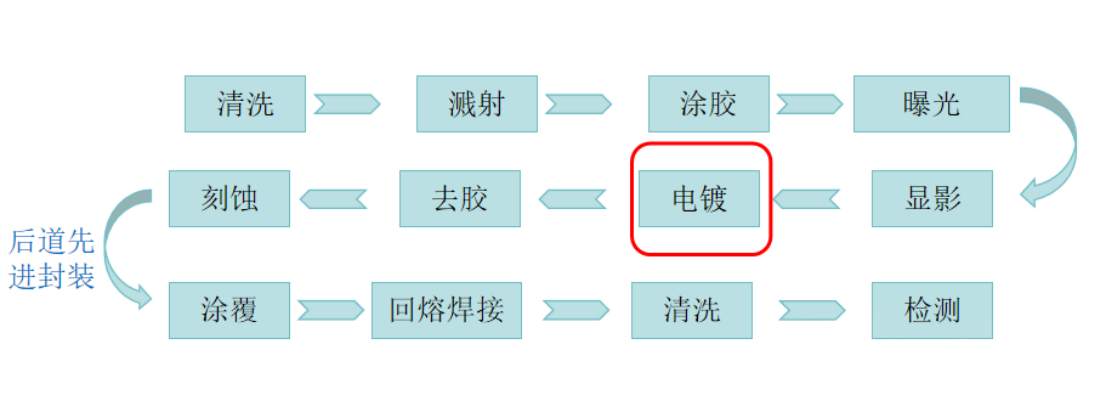

CMOS的基本工藝流程:Wafer將經歷多個步驟的IMP制程

?離子注入的發展歷史

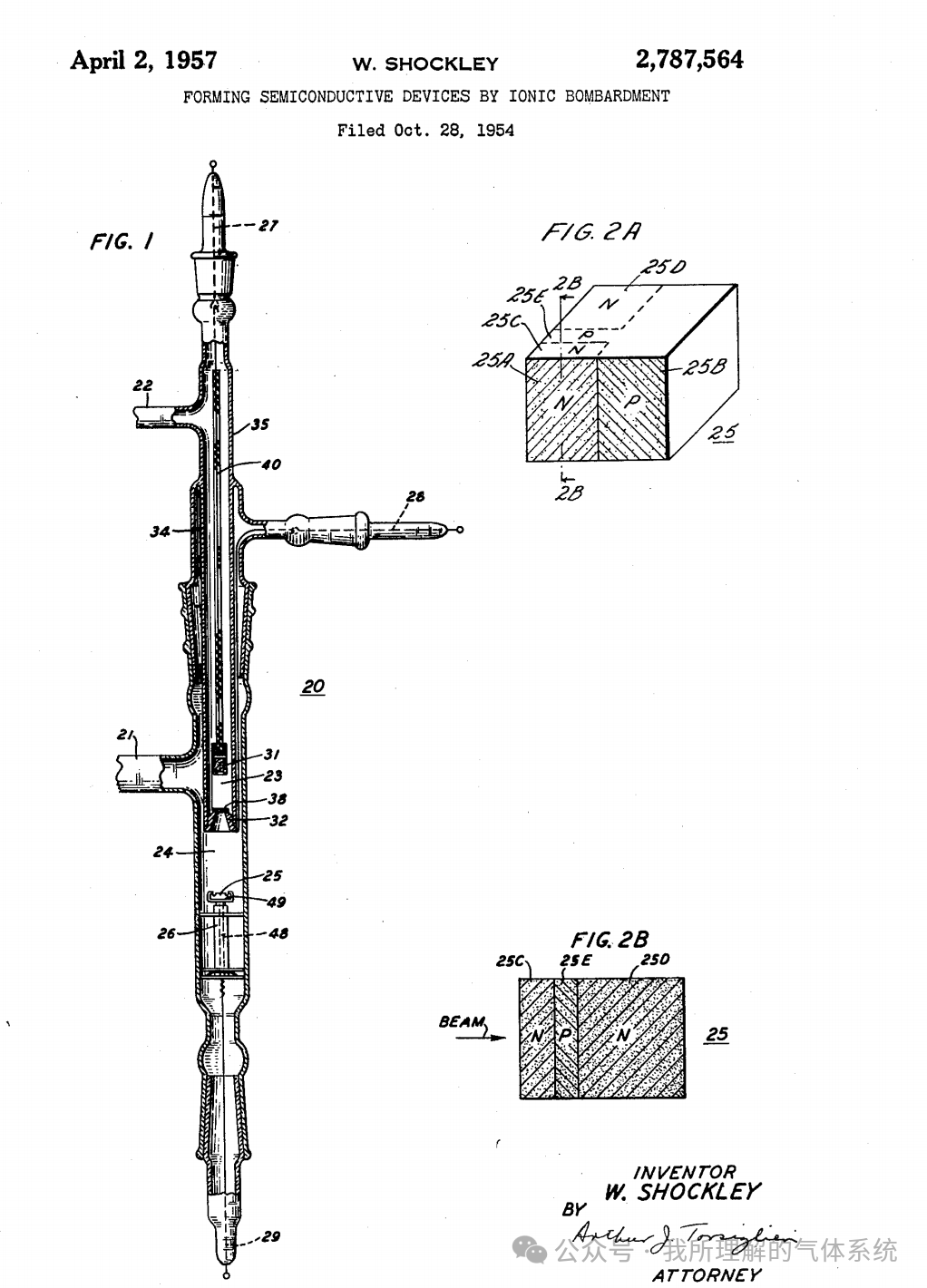

1954年,半導體器件發明人之一的肖克萊提出了離子注入的摻雜技術,并擁有離子注入的專利(US Patent:2787564)

1955年,英國Cussins發現硼離子轟擊鍺晶體,在n型材料上制成了P型層

1960年代,Lindhard/Scharff/Schiott發表射程概念與重離子射程,

理論分析了在非晶體中的離子注入射程分布理論(LSS原理)

1963年,Macaldin在Wafer上注入高濃度的銫離子,形成了P-N結

1970年代,摻雜主要通過高溫爐的擴散過程完成,由于擴散方法對于節深和濃度無法精確控制,并且擴散過程是各個方向上,很難定向控制

雖然高溫爐現在基本用于氧化和退火工藝,很少用于擴散摻雜,

但是高溫爐區域還是沿用了擴散區這個名稱即DIFF(Diffusion)區

1970年代之前由于高能離子束與同位素分離技術的發展,在1970年代中后期,

離子注入技術得到廣泛的應用

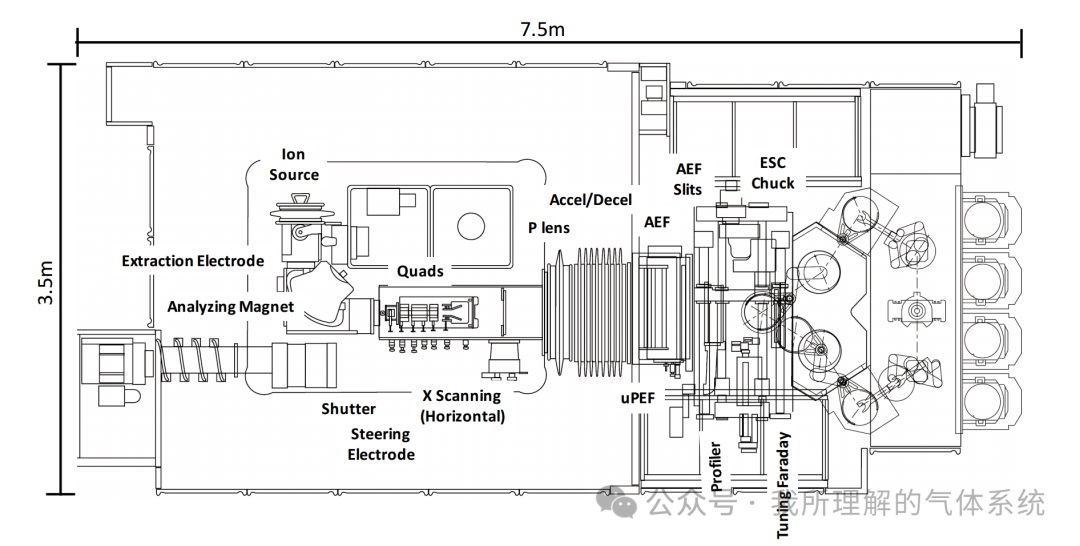

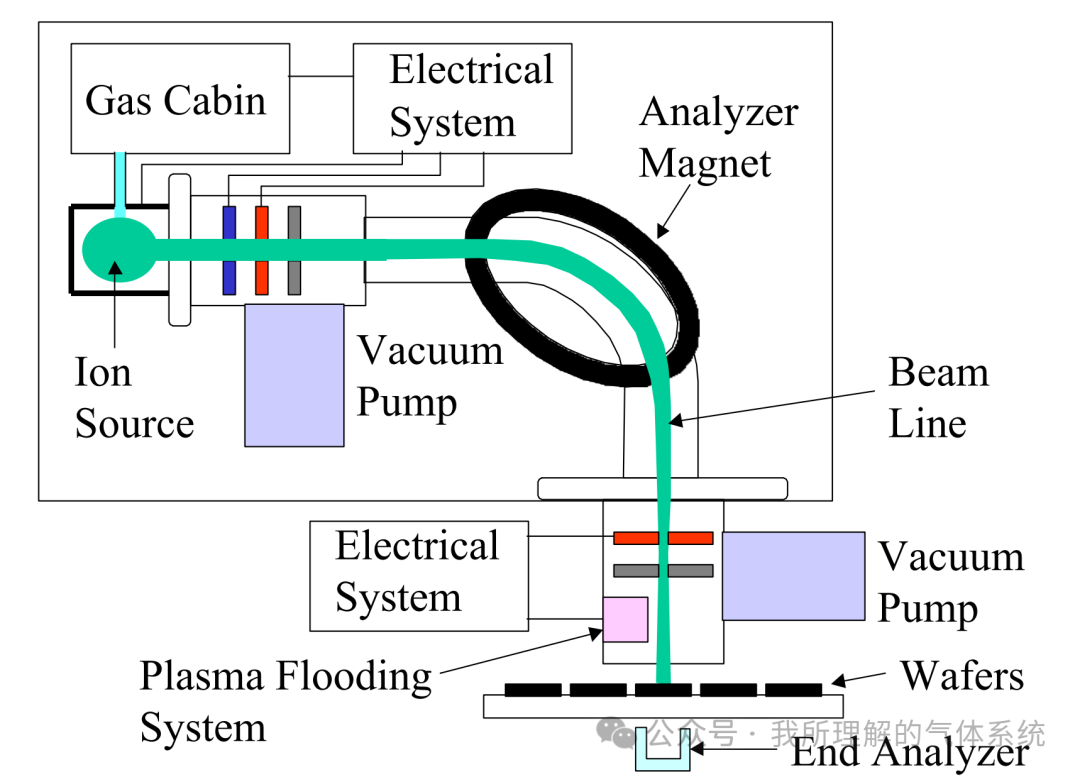

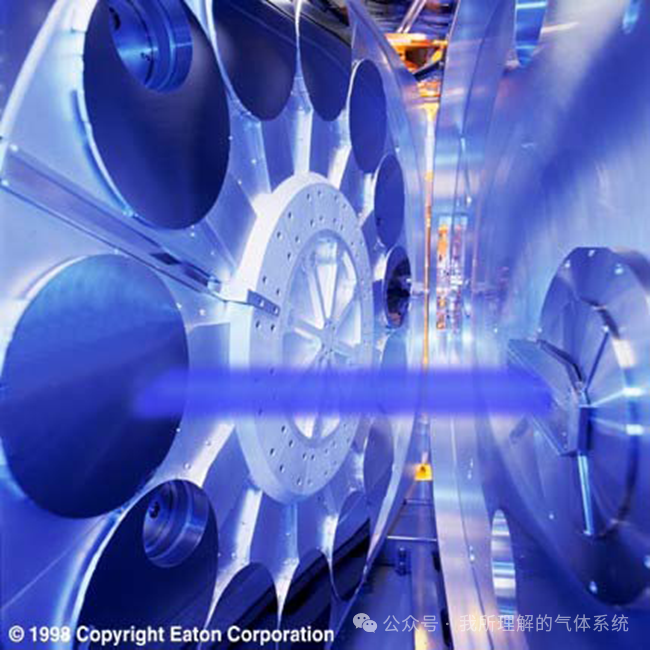

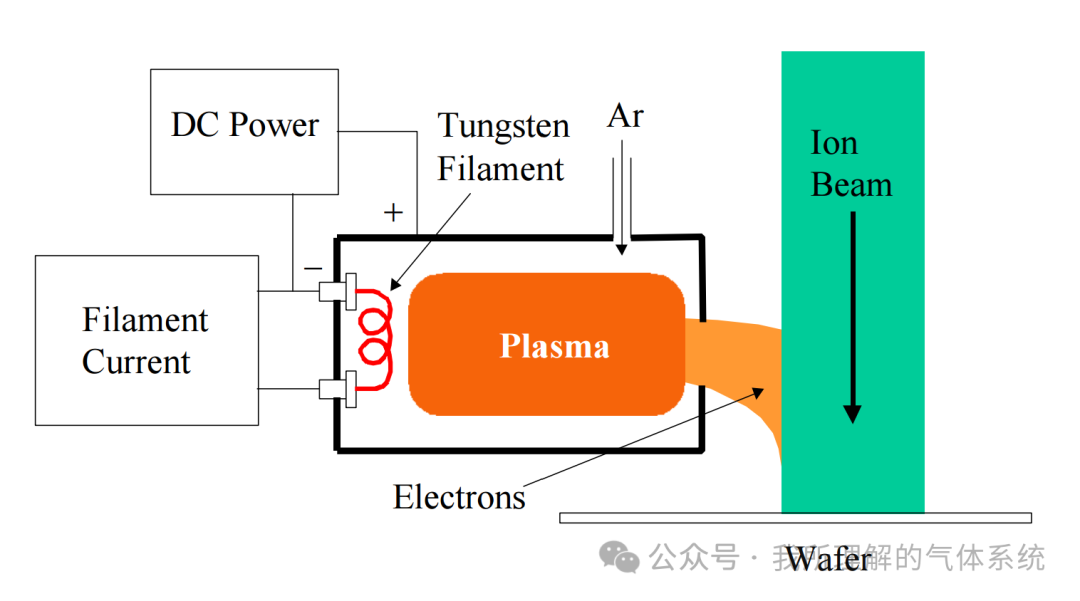

?離子注入機的基本運行原理 離子注入機是非常龐大的設備

總結起來: 氣體電離,電場加速,磁場篩選 基本結構:

氣體系統:BF3/PH3/AsH3/B2H6等常用特種氣體

離子化系統:使氣體電離

真空系統:高真空狀態(10^-6 Torr以上)

質譜篩選:選擇正確的離子進行轟擊

電荷中性化系統:避免電荷在基底累積

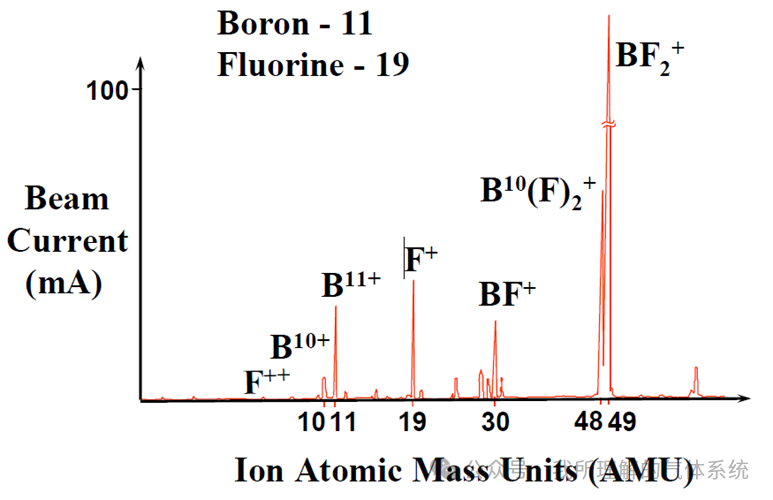

注意:說的簡單,實際上,每個系統都具有非常多考量的設計細節 我們簡單了解一下質譜篩選系統,如何選到我們期望的轟擊離子: 以BF3氣體為例:BF3電離后的離子種類:

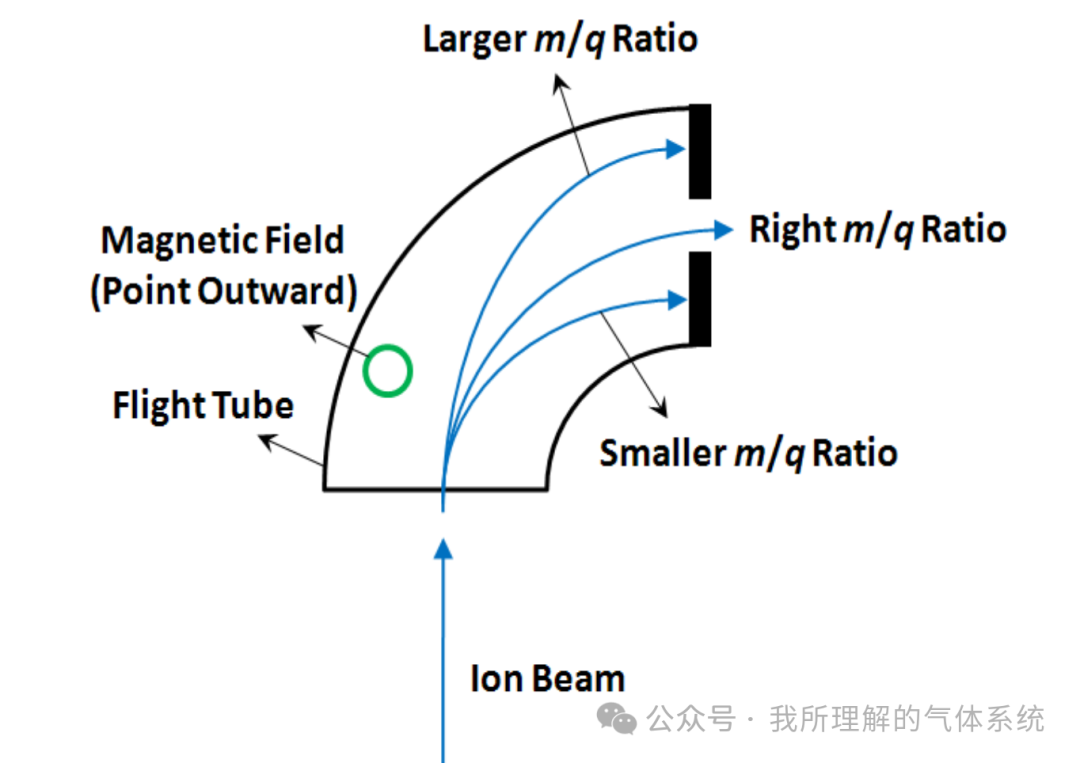

質譜篩選的基本原理是:質荷比不同在磁場中的彎曲半徑不同

帶電離子以一定速度進入磁場,受到洛倫茲力進行偏轉

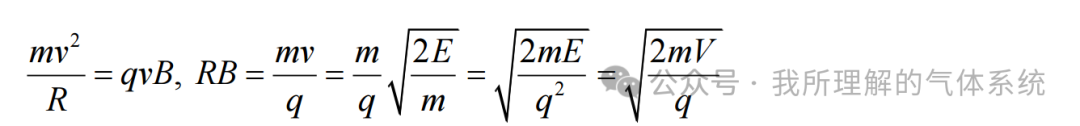

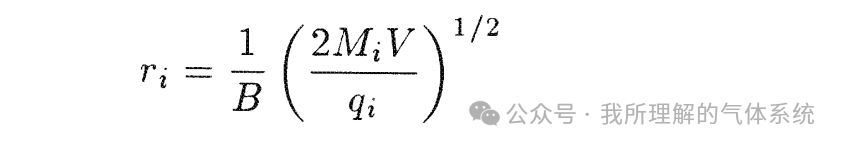

根據:洛倫茲力等于向心力(圓周運動)

可以得到:

控制磁場強度B與加速電極的電壓V不變,

對于不同的質荷比(M/q)的離子具有不同的偏轉半徑

從而篩選出期望的離子

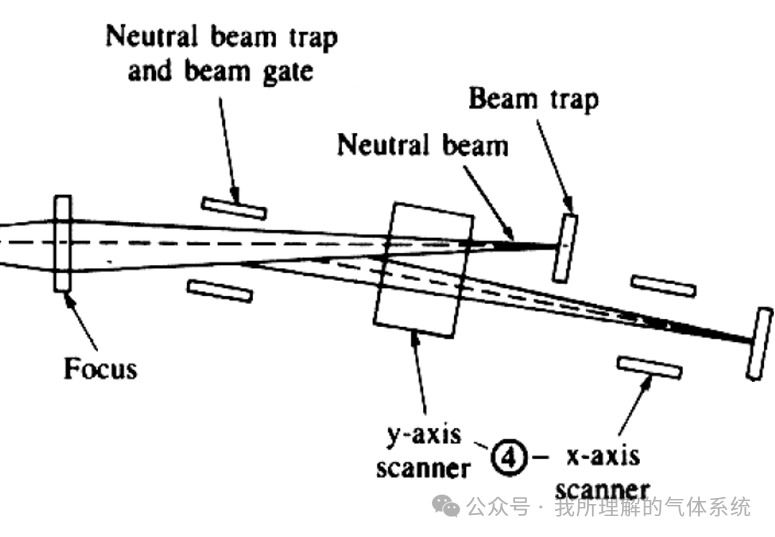

篩選后的離子在加速或者向前運動的過程中,相互碰撞,可能會產生電荷交換導致產生中性的物質,這不是期望的結果。 采用分離裝置,使帶電離子進行偏轉,而中性物質不偏轉進行分離并捕捉有時為了更加高效,可以采用多個分離裝置,使Beam離子束成S形狀

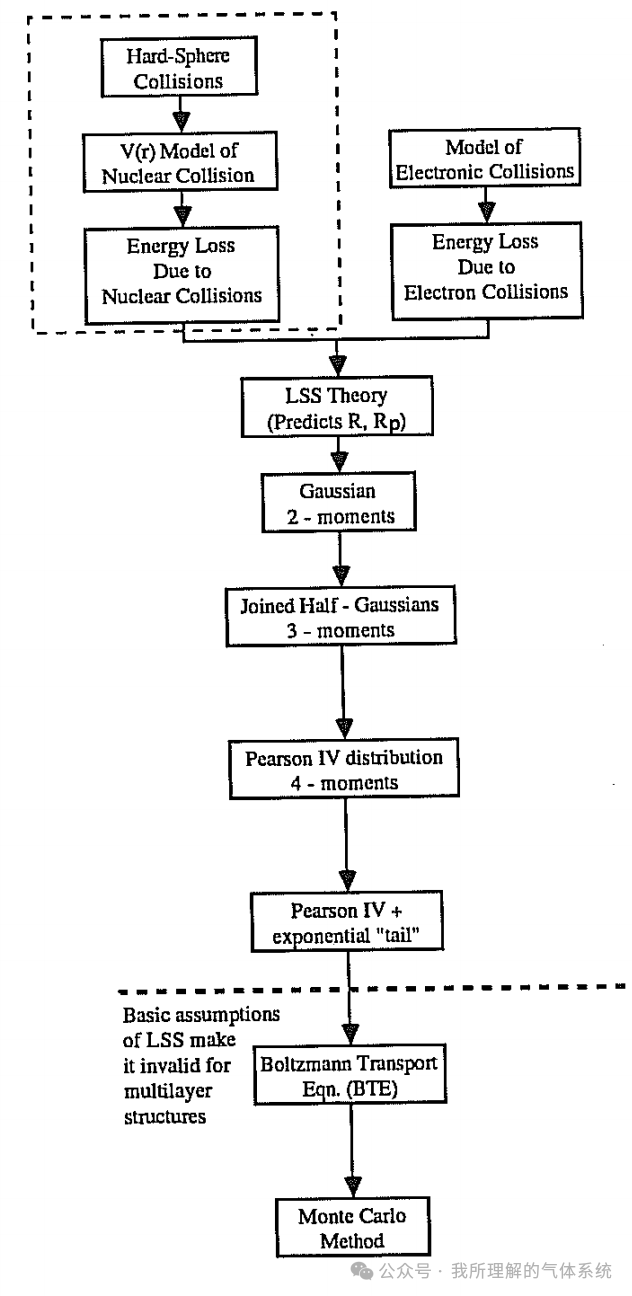

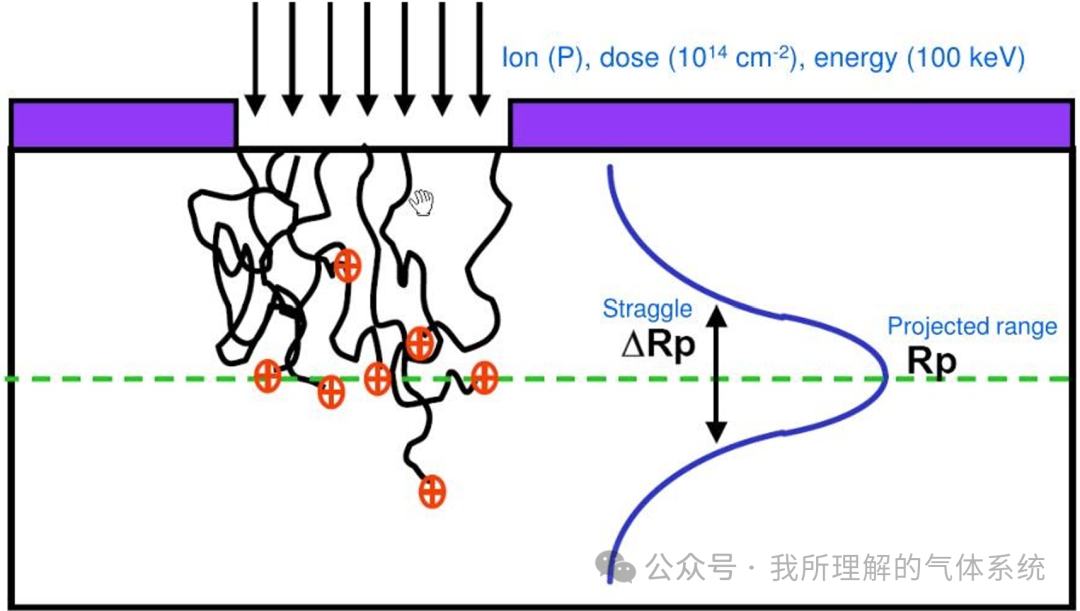

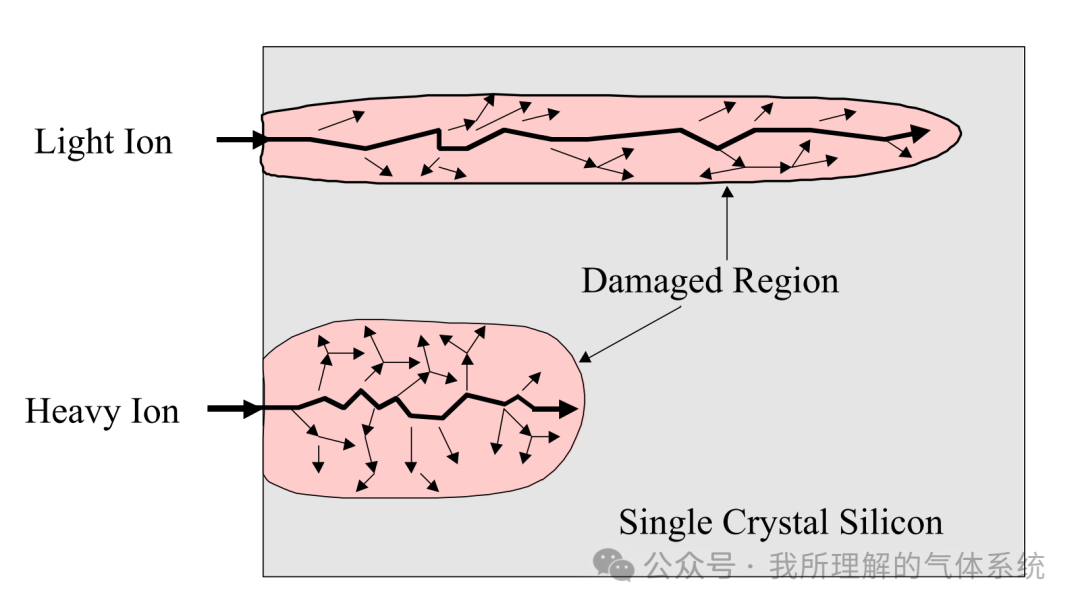

?離子注入方式:摻雜物種類/注入濃度/節深 我們對離子注入進行基本的建模: 1. 大數量的統計模型,很多都符合正態分布(高斯分布),比如天梯積分的分布 2.當離子注入到靶材,最終將會停止在某一位置(Stopping),原因: 1.靶材原子核的碰撞(Energy Loss:Nuclear Collisions) 2.靶材原子的電子碰撞(Energy Loss:Electron Collisions)

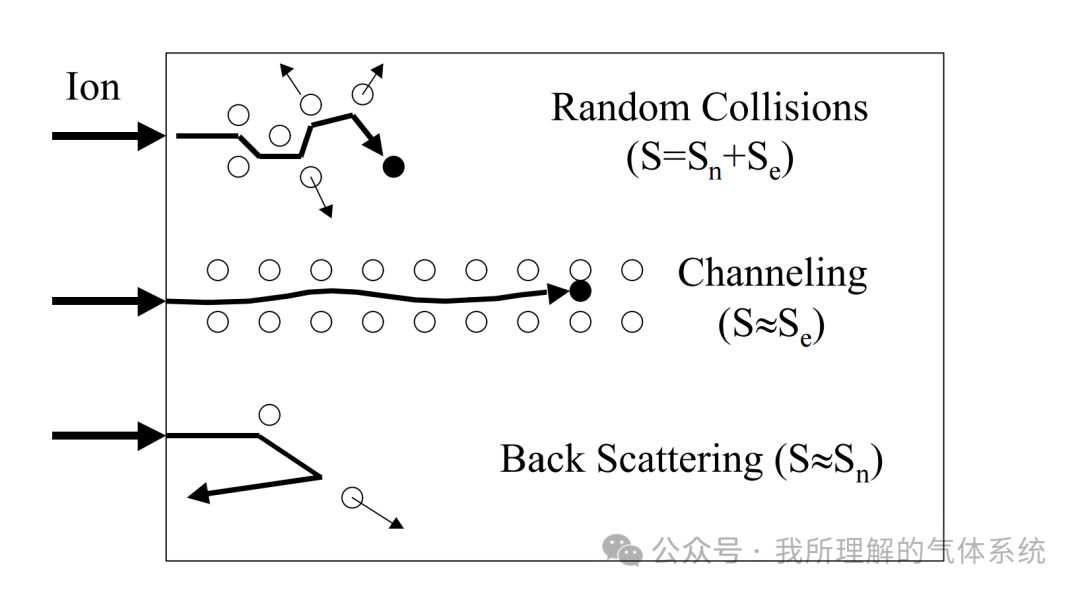

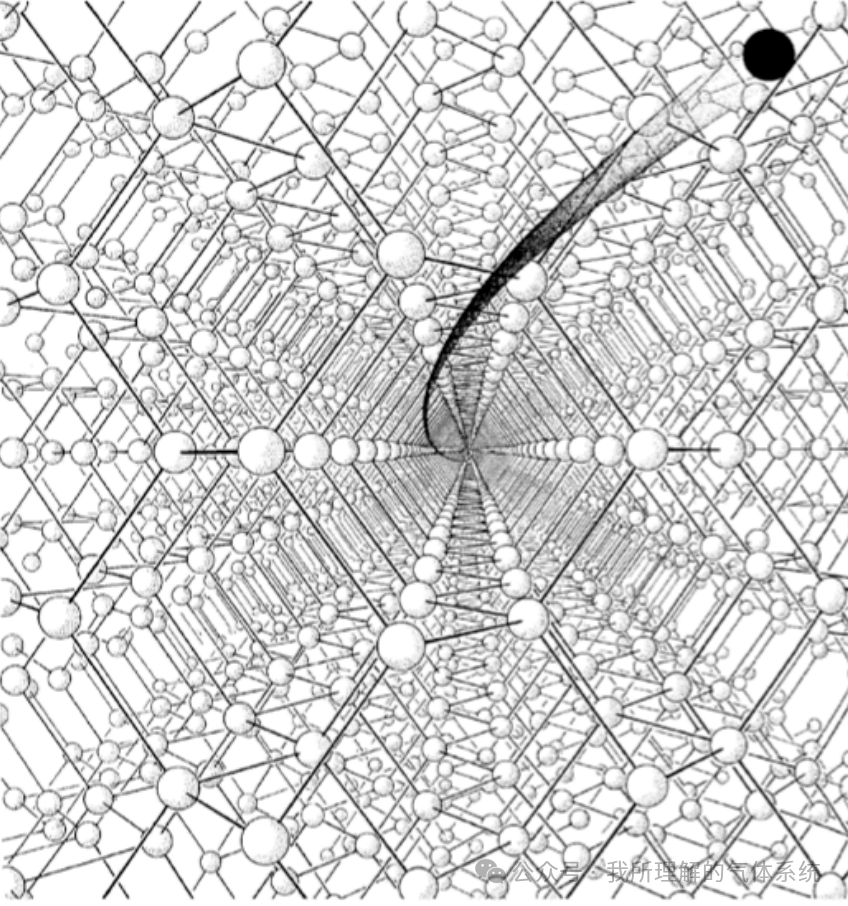

在Channeling情況下,以電子阻擋為主 通過對這2種方式的獨立近似,發展出整個離子注入的分布理論 其中,離子注入(能量/劑量/分布)到非晶靶材(混亂而均勻)的LSS理論是理解的基石。

3.離子注入的基本概念:

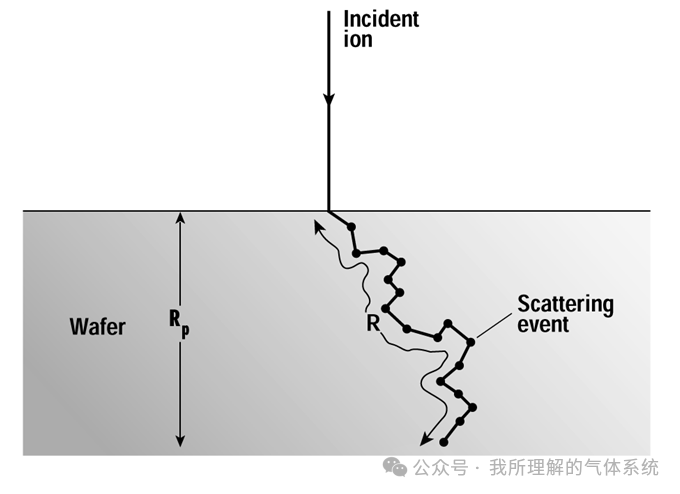

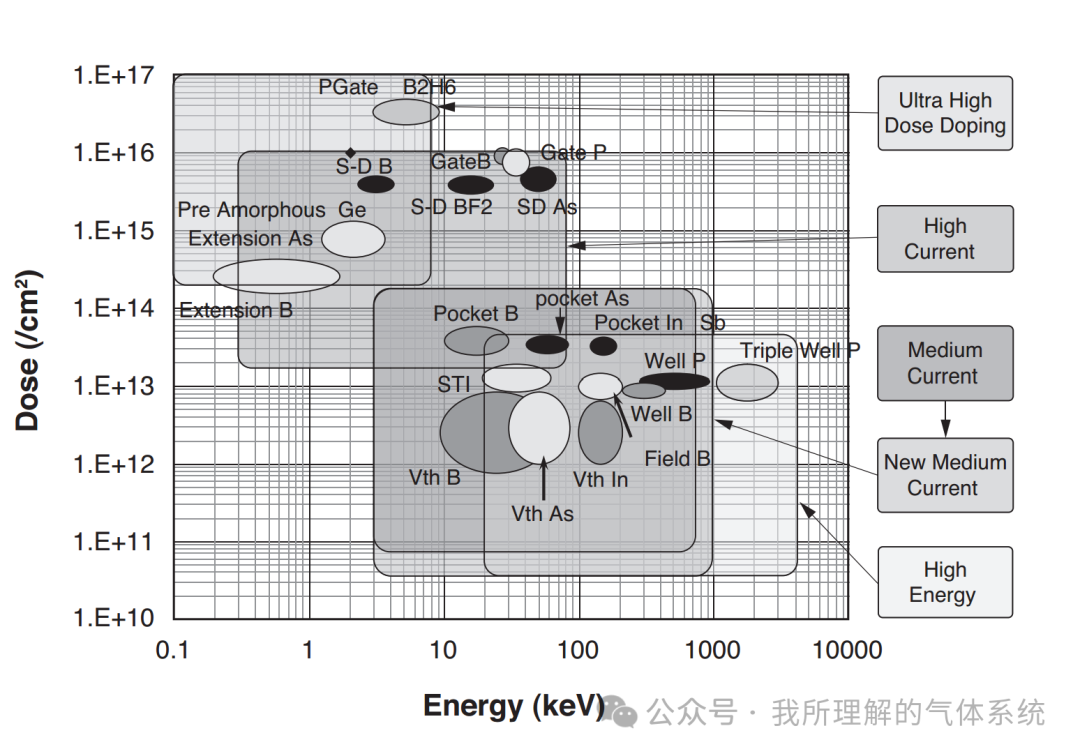

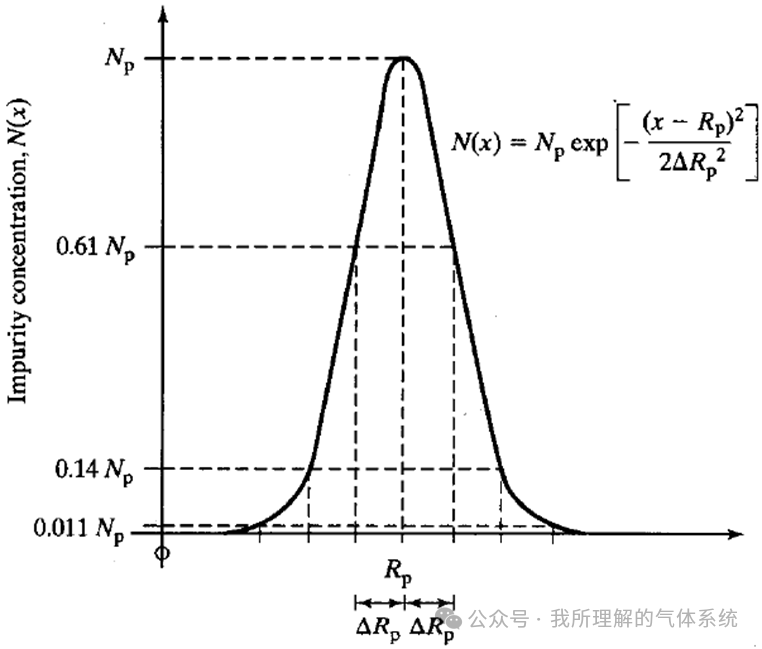

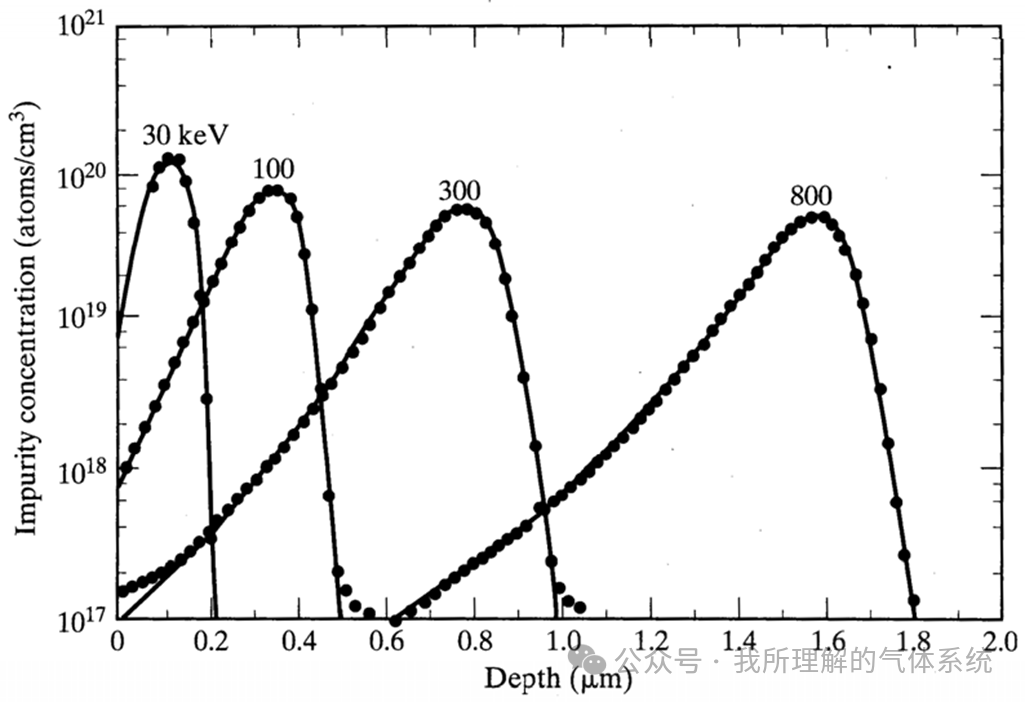

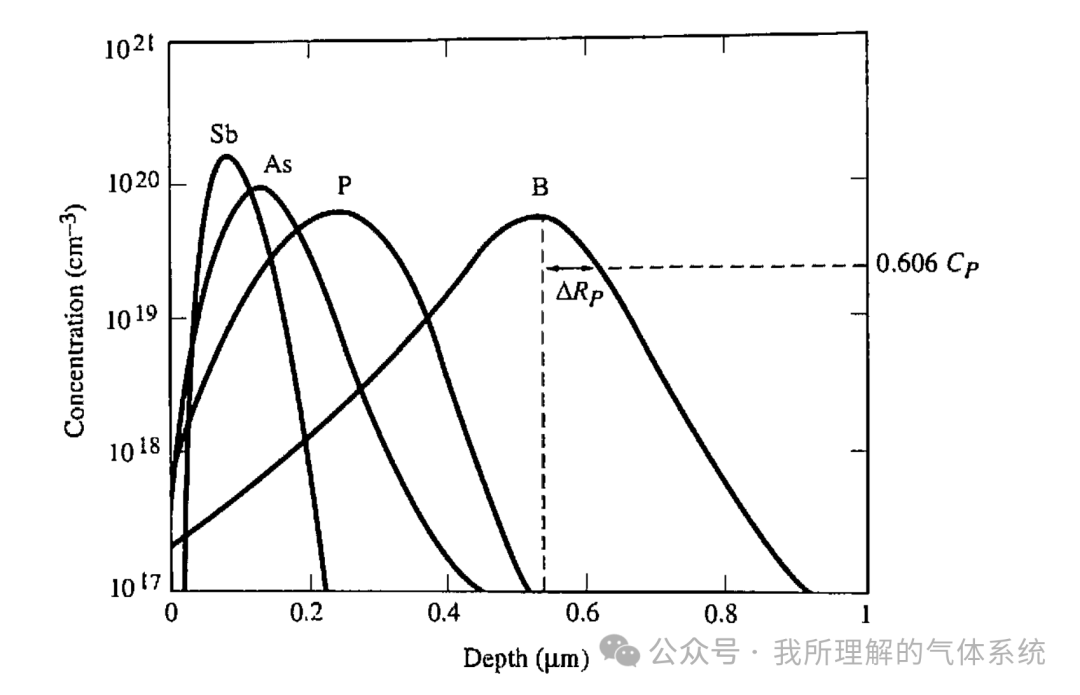

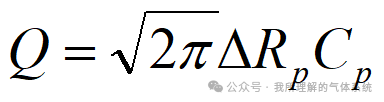

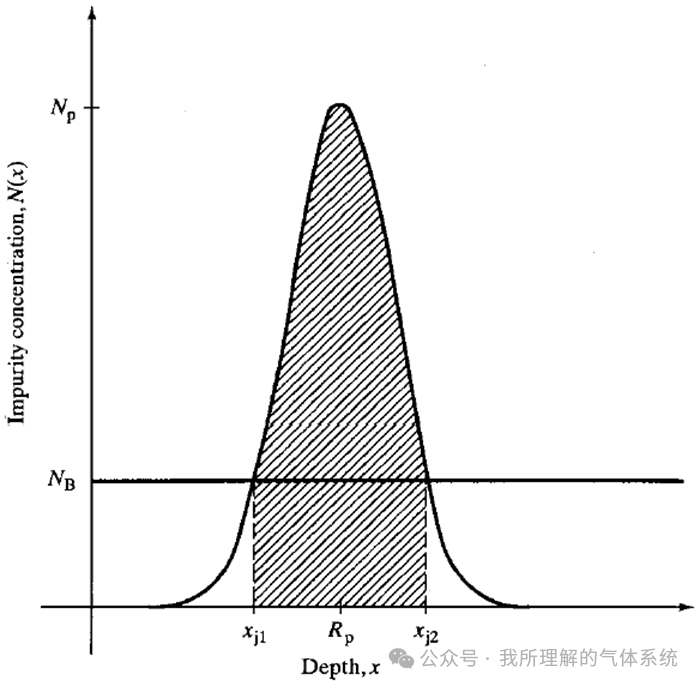

1. 注入能量:keV,離子具有的初始能量,千電子伏特 控制加速電極電壓控制注入能量 2. 注入濃度:Dose, atoms/cm2,單位面積上注入的摻雜原子數量,10^11 - 10^18次方的數量級。這個量可以測量離子束的電流,根據電流的定義計算得到: Dose = I*t/q/A, 電流與時間相乘為電荷量,除以每個離子的電荷量即為離子總數,除以面積得到Dose. 控制電流與注入時間,控制注入量 3. 注入深度:Rp, P為Projected.Rp可理解為平均深度,Rp是投影距離 大量相同的離子,相同的能量注入,由于碰撞后不同的方向,受力的不同,在靶材內的深度與濃度的關系是符合高斯分布(理想情況)

不同的計量與能量在不同情況下的應用,按電流和能量分為不同的情況。 注意:以下都是非晶Si的情況,不是單晶Si的情況:當離子不在通道效應的情況下轟擊,可以近似認為離子轟擊非晶體 單晶Si的情況更加復雜 離子注入是大量的離子數量,所以符合統計規律,很多的平均量的表述。

理想情況下高斯分布,實際情況下,采用Pearson IV分布的預測與實測值吻合非常好。

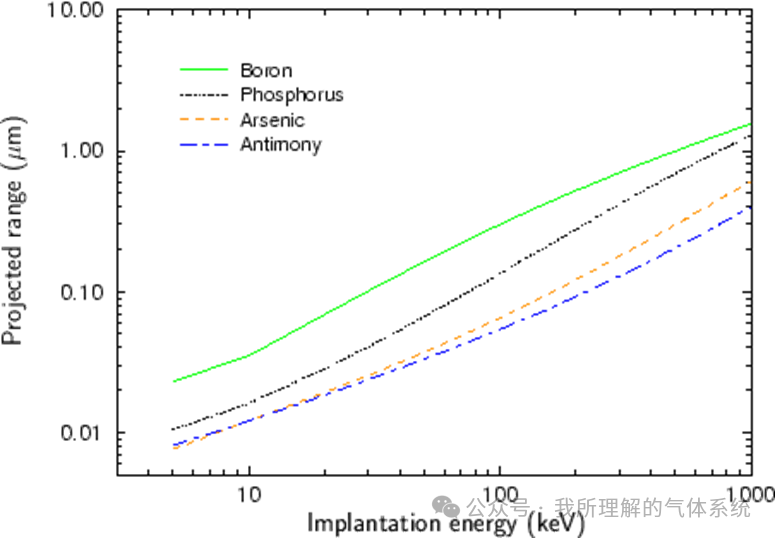

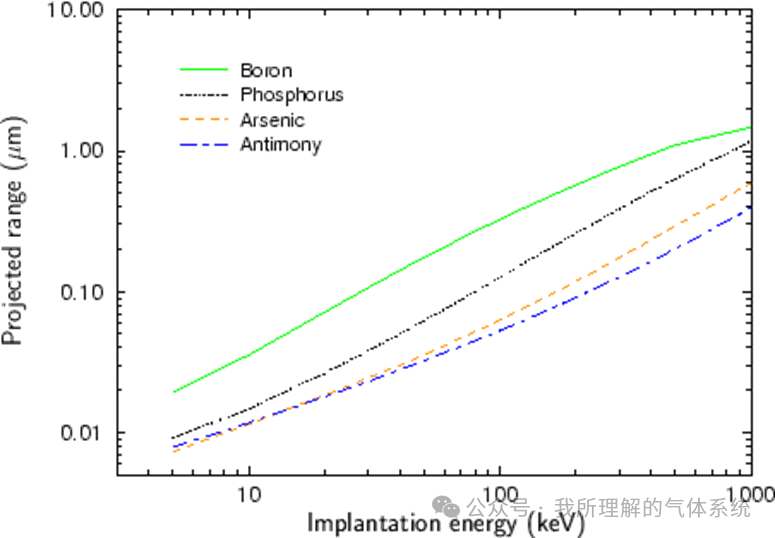

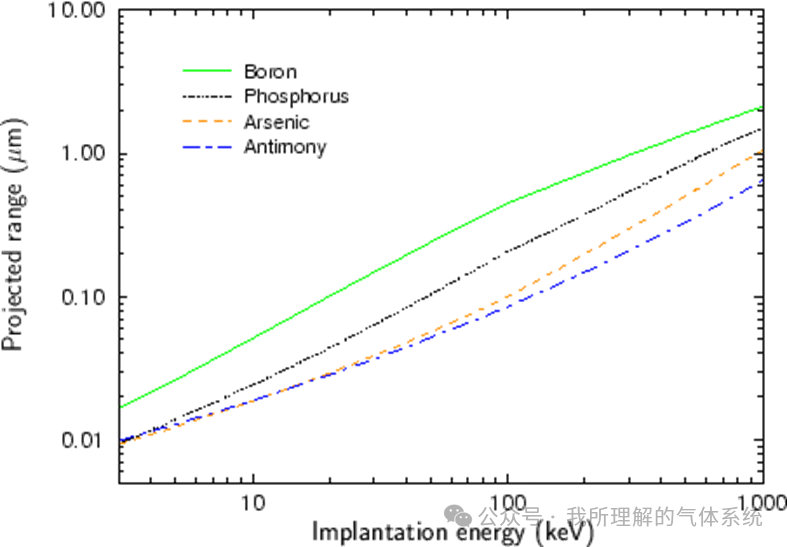

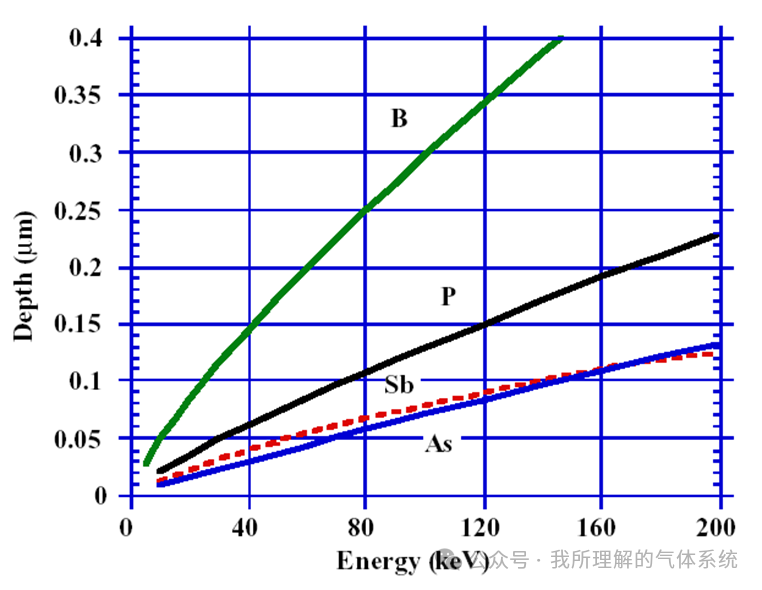

有了一些基本定義的概念,我們可以得到一些結論: 相同注入能量下,輕離子的注入深度更深,很好理解: 200keV的條件下,不同原子的深度:硼是11,最輕,Rp最大,深度最遠

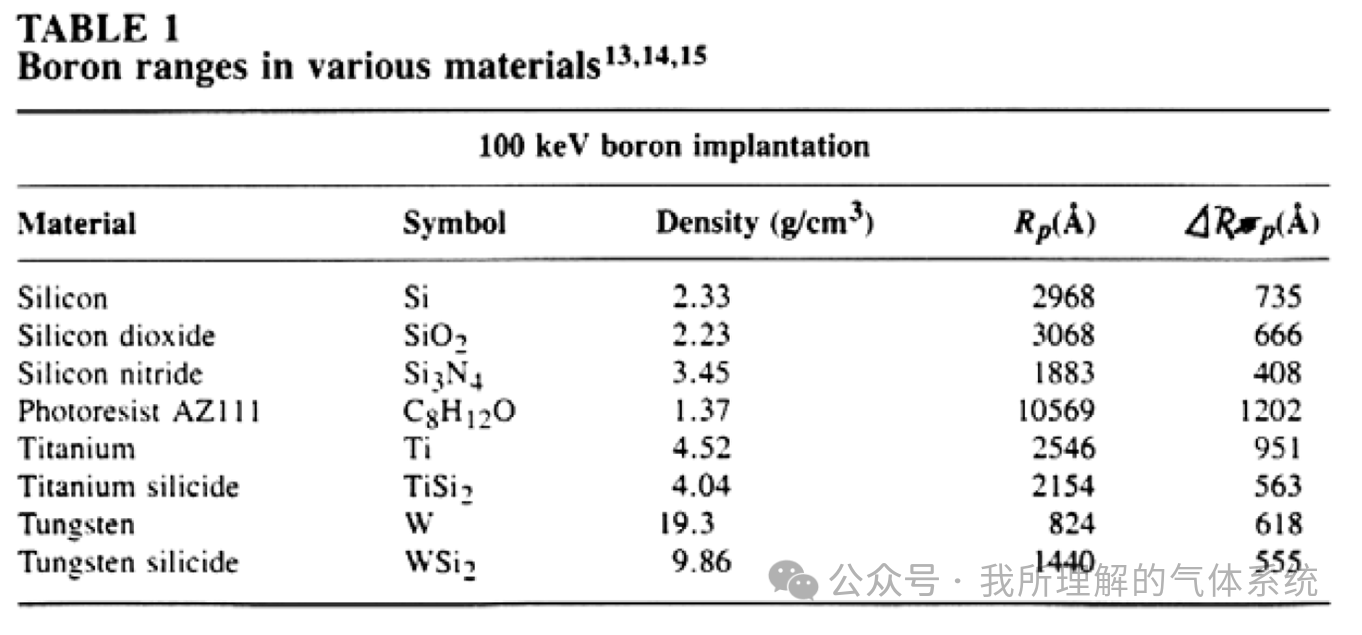

相同的能量,相同的離子,在不同的靶材上的Rp不同。

對于Si為靶材來說:不同能量下的Rp深度如下:

對于SiO2為靶材來說(可能會當作植入掩蔽層):

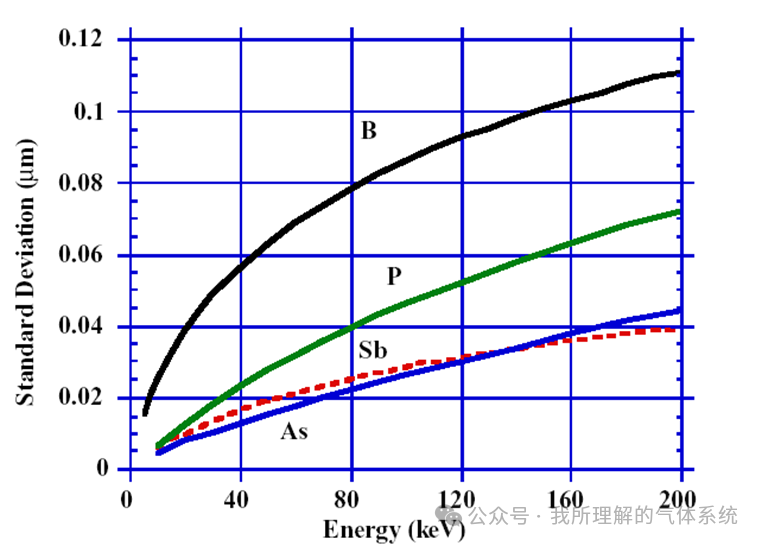

Si/SiO2圖形非常相似,這兩個是絕配,這也是Si可以成為主流的關鍵。 淺結界的一個方法,可以先生長一層SiO2氧化膜,由于Si/SiO2之間的匹配性,再植入離子,這層氧化膜充當了Si的角色,相同離子能量下,在實際的下層硅片中只植入了部分,再清洗掉SiO2,完成淺結界。 想用SiO2做阻擋層,下層Wafer不要被植入,這層SiO2厚度可以為:相同條件下,Rp+6ΔRp即可,ΔRp為標準差 當然光刻膠也可以做阻擋層,不用再單獨生長SiO2。但是光刻膠的厚度需要根據光刻膠的物質進行核算。

AZ-7500 resist的植入深度

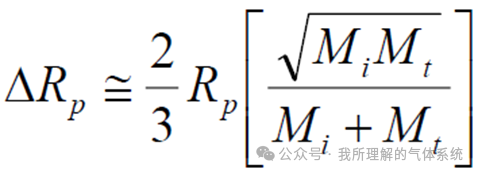

在計算過程中,Rp與ΔRp是重要的數值,當然也是有圖表可以查的數值, 這兩個數值是同時存在的。

一些基本的關系如下:

我們可以做一個簡單的估算問題: P,100ekV,注入非晶區域Si,Rp處的濃度需求10^17 atoms/cm3 查表:100keV,Rp=0.12um,ΔRp=0.045um Q=1.13*10^12 atoms/cm2 離子注入可以有非常多的理論預測計算,這就不再計算了。 對于在Si中的PN結的結深,相當于在P型區域注入N型原子:預測也是相當復雜

總之,離子的結深/濃度的分布是需要精確預測的,而通過控制離子的能量與注入量可以得到期望的分布 當原子有序排列時,單晶類型,一些額外的情況會發生: Si原子的晶格立體結構,在某些方向上會產生通道(Channeling)

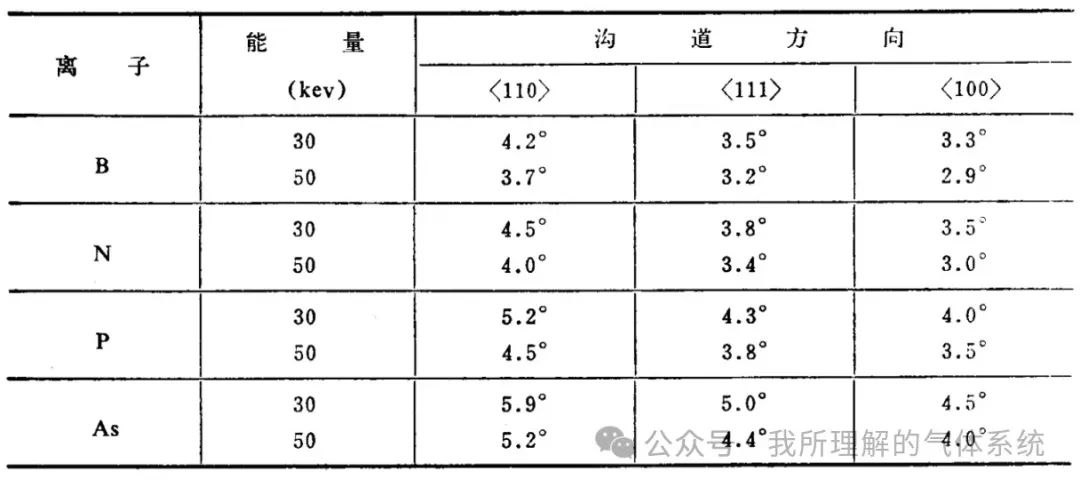

可以想象,植入原子進入該通道會跑的特別遠,大部分情況下,并不是期望的結果。臨界角度的計算也是非常復雜 不同離子以及能量下的臨界角,超過這個角度,可以有效減緩通道效應

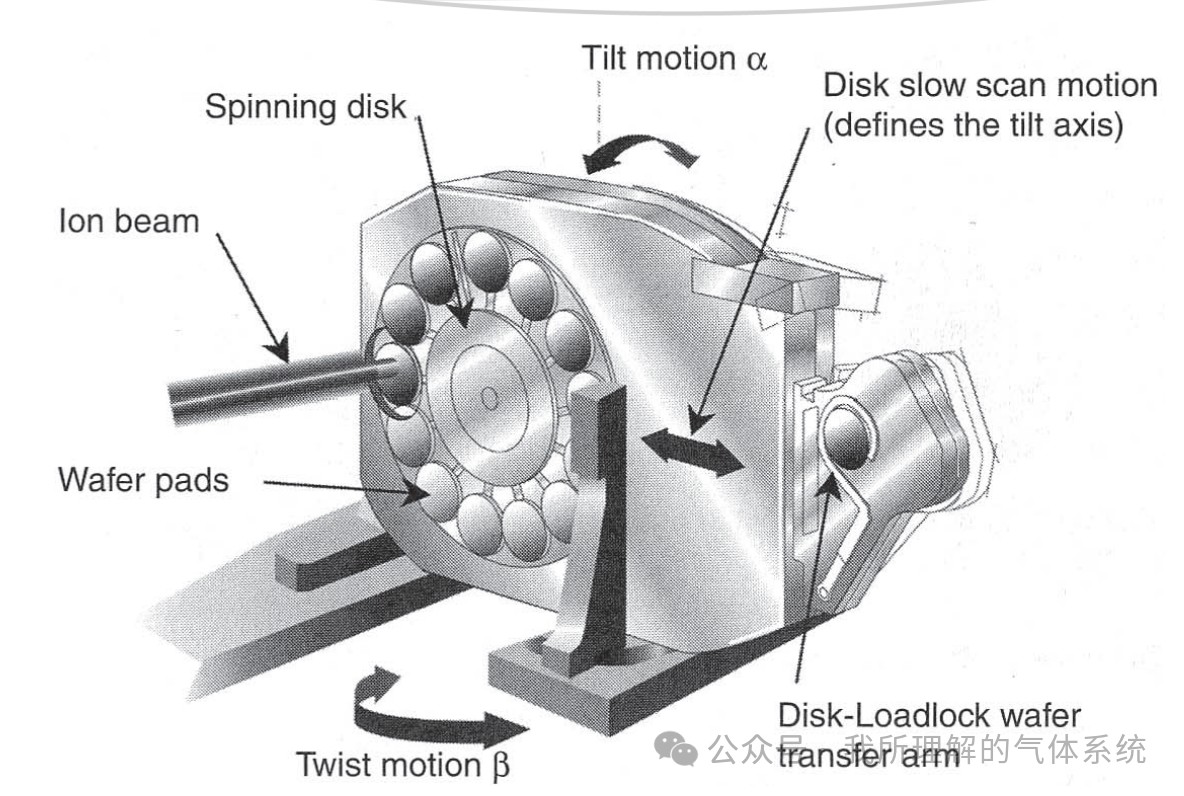

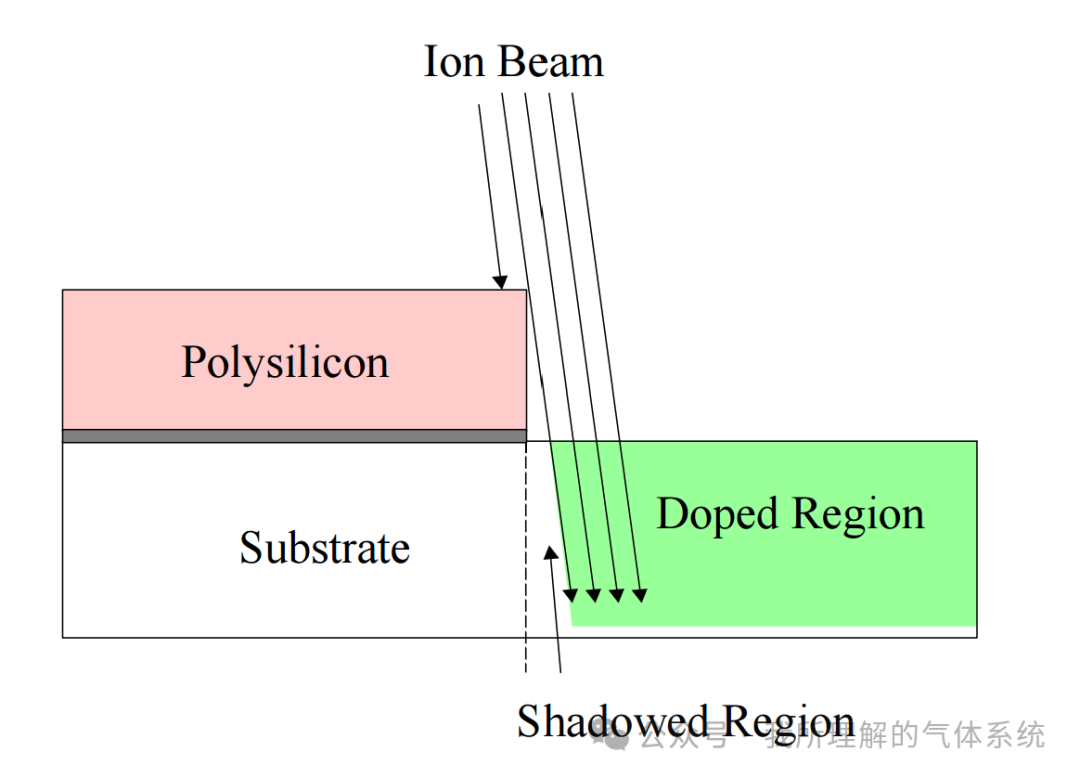

在腔室的設計中,采用旋轉的方式同時可以調整角度(Si wafer tilt 7°) 旋轉以及Wafer傾斜可以減少 通道效應與 Shadowing Effect

離子注入額外的問題:電荷中和/退火 RTA 電荷中和: 當帶電離子不斷的植入Wafer或者顯示行業的基板BP,正電荷會在表明積累,當到達一定電壓,會排斥離子同時也會損傷Wafer上的器件, 所以需要中和掉植入的電荷:有很多種方式:

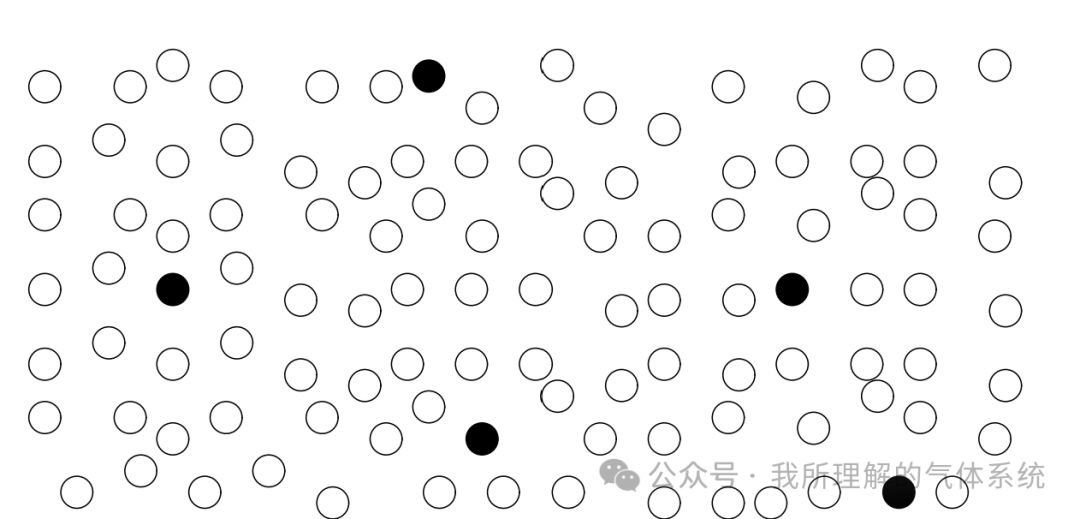

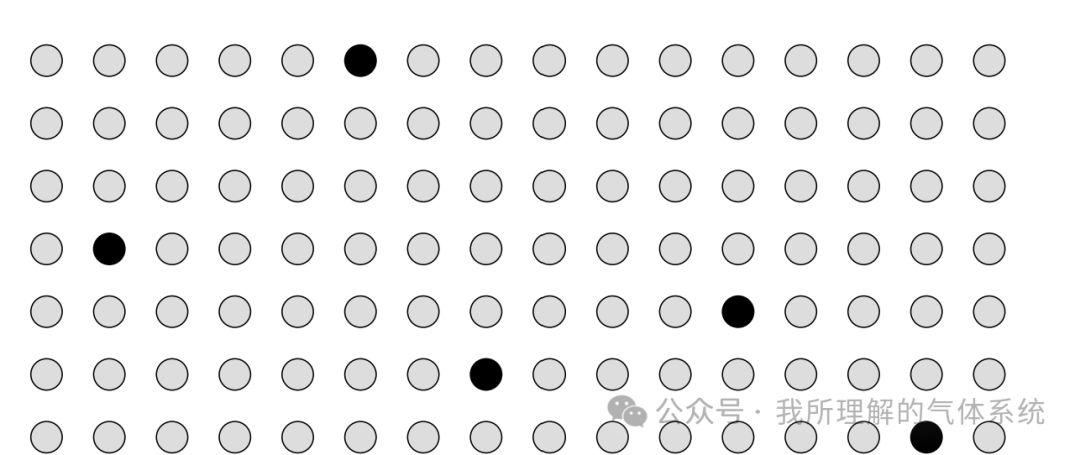

在AMOLED制程中,機臺會采用Xe這種氣體作為電子來源,中和離子注入的電荷。一般離子注入機臺:BF3/PH3/Xe是標配 現在需要說明非常重要的一個問題: 離子注入后的退火工藝 退火表面意思看起來像降溫,實則完全相反,通過加熱溫度使得原子獲得能量自發的到晶格上去的方法。 因為原子都在晶格上可以理解為整個系統處于最低能量狀態,原子吸收能量后,總是傾向于跑到晶格位置。 容易想象的是,當大量的離子轟擊靶材時,靶材上原有晶格上的原子可能會被轟擊的亂七八糟,不進行退火工藝,則這樣的缺陷是無法做到要求的導電能力。 晶格損傷有多種類型,至少有5-6種。

在高溫爐內進行退火工藝,可以分批操作,但是時間長,對于先進制程可能對已經做好的部分造成損傷,于是RTA技術應運而生 當然激光退火技術也得到了很多的應用,比如ELA(Exclaimer Laser Annealing,采用308nm XeCl準分子激光進行退火,使非晶Si變成Poly-Si,在LTPS的TFT生產中應用廣泛) RTA:Rapid Thermal Annealing : 快速退火技術

RTA屬于RTP(Rapid Thermal Processing)中的一種,這是另外一個專題的內容了,將會繼續更新RTP的內容。 RTA可以在半分鐘內完成500 - 1000℃的溫度上升,使得退火過程進行非常快,也可以一定程度上抑制 由于退火導致的摻雜原子的擴散,當然也可以很快速的冷卻。 主要目的是:恢復破壞的晶格并激活摻雜離子 退火前:

退火后:

對于從事IMP制程的人員,建議特別的了解一下LSS理論以及后續的一些發展 離子注入如同子彈打入一個有規律的晶體結構中,這個結構中有晶格上的原子進行反彈,同時也有無形的無數電子形成的勢場拖拽子彈,導致子彈最終停下。 總的來說,這是一個物理過程,經過合理的簡化與近似,可以比較準確的預測重要的物理量,射程/分布/濃度 感謝閱讀,歡迎轉載和分享!

-

工藝

+關注

關注

4文章

669瀏覽量

29248 -

IMP

+關注

關注

0文章

12瀏覽量

8565 -

半導體制造

+關注

關注

8文章

441瀏覽量

24559

原文標題:半導體制程—離子植入-IMP

文章出處:【微信號:芯長征科技,微信公眾號:芯長征科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

半導體制冷機chiller在半導體工藝制程中的高精度溫控應用解析

揭秘半導體電鍍工藝

最全最詳盡的半導體制造技術資料,涵蓋晶圓工藝到后端封測

靜電卡盤:半導體制造中的隱形冠軍

半導體制造里的ALD工藝:比“精”更“精”!

鎵在半導體制造中的作用

【「大話芯片制造」閱讀體驗】+ 半導體工廠建設要求

ESD靜電對半導體制造的影響

半導體制造設備對機床的苛刻要求與未來展望

半導體制造工藝中的離子植入技術(IMP)

半導體制造工藝中的離子植入技術(IMP)

評論