開放數(shù)據(jù)中心委員會ODCC冬季全員會議于12月4日-6日在春暖花開的昆明舉行。奇異摩爾首席系統(tǒng)架構師朱琛作為網(wǎng)絡工作組ETH-X超節(jié)點項目的核心成員分享了AI Networking Scale Up卡間互聯(lián)的新路徑解決方案并展開了相關應用分析。

隨著人工智能大模型訓推的需求日益增長,更大的模型并行規(guī)模,模型并行中Tensor并行或MOE類型的Expert并行都會在GPU之間產(chǎn)生大量的通信。這對于AI網(wǎng)絡Scale Up加速卡通訊提出了更高的顯存容量及帶寬、更低的延遲需求。

通常來說,Scale Up相對于Scale Out和業(yè)務網(wǎng)絡需要更高一個數(shù)量級(10倍以上)的帶寬,同時由于對于延遲的需求,要求GPU Direct直出互聯(lián)的設計,并節(jié)省更多的面積給芯片的計算核心、更高的IO集成能力。

傳統(tǒng)的做法是GPU SoC內(nèi)部集成不同的IO IP通過片上網(wǎng)絡進行通信互聯(lián)。然而,Scale Up網(wǎng)絡還在不斷的演進當中,行業(yè)目前在標準制定與生態(tài)上還缺乏完備的解決方案。隨著相關技術的革新與演進,對GPU的未來設計及其相關性能提出更復雜的需求與挑戰(zhàn)。

傳統(tǒng)基于GPU SoC IO IP的方案在先進工藝的成本與靈活性方面缺乏優(yōu)勢,計算芯片需要和IP使用統(tǒng)一一致的工藝節(jié)點;另一方面,如果對于互聯(lián)的設計產(chǎn)生較大的改變,將花費更多的時間與精力重新設計整體芯片方案。

(傳統(tǒng)直接集成IO IP的計算芯片)

奇異摩爾作為ETH-X超節(jié)點項目的成員提出了一種新的GPU片間互聯(lián)路徑。一種GPU內(nèi)集成IO Die (邊緣IO Chiplet)的創(chuàng)新方案在未來Scale Up互聯(lián)的場景下能夠靈活應用并達到更可靠的GPU互聯(lián)通信效率。

(基于IO Die的計算芯片,計算芯粒和IO芯粒解耦,通過UCIe互聯(lián))

GPU計算芯粒與IO 芯粒解耦,更靈活的技術演進和創(chuàng)新

IO Die 讓GPU芯粒和IO芯粒解耦并通過UCIe D2D互聯(lián),這種方式讓GPU芯粒和IO Die能夠分開進行設計,并使用不同的先進工藝節(jié)點。當前Scale up的技術正處于不斷演進的過程中,基于IO Die的方案相比SoC可以提供更快的技術迭代。

復用IO Die,降低成本

采用獨立的IO Die使在新的設計中復用已有的IOD成為可能,比如Central IOD AMD EPYC Turin繼續(xù)復用上一代6nm制程的IOD 繼續(xù)實現(xiàn)制程/芯粒解耦,減少工藝成本。Intel的至強6使用了邊緣IOD的方式同樣實現(xiàn)了計算芯粒和IOD的解耦。

(圖:AMD 使用Central IOD實現(xiàn)內(nèi)核工藝節(jié)點與IO分開 ,并復用IOD來降低成本)

靈活性及擴展性

基于Chiplet 的靈活性,用戶根據(jù)各自的帶寬需求自主選擇IO Die的數(shù)量和類型,在Scale Up的場景下來實現(xiàn)互聯(lián)帶寬的靈活配置。

奇異摩爾的Kiwi NDSA-G2G就是上述這種GPGPU集成IO Die芯粒的新路徑解決方案,不僅具備上述所列優(yōu)勢,并內(nèi)建Scale Up所需要的網(wǎng)絡加速控制引擎。客戶只需自研計算芯粒,免去自研互聯(lián)芯粒的成本,基于統(tǒng)一的互聯(lián)協(xié)議和接口采用Kiwi NDSA-G2G芯粒來實現(xiàn)片間TB級的互聯(lián)。

使用UCIe建立GPU芯粒與IO Die間互聯(lián)

奇異摩爾的GPU Link NDSA G2G (IO Chiplet) 通過基于UCIe的D2D IP與計算芯粒互聯(lián)。UCIe是主流的D2D國際互聯(lián)標準,目前已經(jīng)受到了廣泛芯粒上下游的認可。UCIe 1.1v 本身支持主流Streaming等協(xié)議,并通過FLIT的按需交織實現(xiàn)多協(xié)議的復用。基于UCIe的D2D互聯(lián)無論從芯片面積占用、延遲(ns)、以及功耗的增加都在一個極低的可控制范圍。

關于GPU芯粒和IO Die的通信

如果GPU芯粒和IO Die在協(xié)議層使用同種協(xié)議,互通可以無縫實現(xiàn),無需進行額外的協(xié)議轉換。如果GPU芯粒和IO Die在協(xié)議層采用不同的協(xié)議時,協(xié)議適配與轉換可以根據(jù)客戶的芯粒設計所處階段來適配協(xié)議在哪一側進行轉換。

隨著國內(nèi)芯粒生態(tài)以及Scale Up網(wǎng)絡相關技術標準的日益完善,奇異摩爾展望從片間協(xié)議再到片內(nèi)協(xié)議,推動行業(yè)建立統(tǒng)一互聯(lián)標準,從而攜手產(chǎn)業(yè)鏈共同實現(xiàn)超過十萬張加速卡的高效互聯(lián)。AI網(wǎng)絡的春天即將到來,希望的曙光在不久的將來將照拂行業(yè)的每一位前行者。

關于我們

AI網(wǎng)絡全棧式互聯(lián)架構產(chǎn)品及解決方案提供商

奇異摩爾,成立于2021年初,是一家行業(yè)領先的AI網(wǎng)絡全棧式互聯(lián)產(chǎn)品及解決方案提供商。公司依托于先進的高性能RDMA 和Chiplet技術,創(chuàng)新性地構建了統(tǒng)一互聯(lián)架構——Kiwi Fabric,專為超大規(guī)模AI計算平臺量身打造,以滿足其對高性能互聯(lián)的嚴苛需求。我們的產(chǎn)品線豐富而全面,涵蓋了面向不同層次互聯(lián)需求的關鍵產(chǎn)品,如面向北向Scale out網(wǎng)絡的AI原生智能網(wǎng)卡、面向南向Scale up網(wǎng)絡的GPU片間互聯(lián)芯粒、以及面向芯片內(nèi)算力擴展的2.5D/3D IO Die和UCIe Die2Die IP等。這些產(chǎn)品共同構成了全鏈路互聯(lián)解決方案,為AI計算提供了堅實的支撐。

奇異摩爾的核心團隊匯聚了來自全球半導體行業(yè)巨頭如NXP、Intel、Broadcom等公司的精英,他們憑借豐富的AI互聯(lián)產(chǎn)品研發(fā)和管理經(jīng)驗,致力于推動技術創(chuàng)新和業(yè)務發(fā)展。團隊擁有超過50個高性能網(wǎng)絡及Chiplet量產(chǎn)項目的經(jīng)驗,為公司的產(chǎn)品和服務提供了強有力的技術保障。我們的使命是支持一個更具創(chuàng)造力的芯世界,愿景是讓計算變得簡單。奇異摩爾以創(chuàng)新為驅(qū)動力,技術探索新場景,生態(tài)構建新的半導體格局,為高性能AI計算奠定穩(wěn)固的基石。

-

gpu

+關注

關注

28文章

4912瀏覽量

130673 -

數(shù)據(jù)中心

+關注

關注

16文章

5145瀏覽量

73215 -

奇異摩爾

+關注

關注

0文章

54瀏覽量

3665

原文標題:聚焦昆明ODCC 冬季全員會議,奇異摩爾分享計算芯片Scale Up 片間互聯(lián)新途徑

文章出處:【微信號:奇異摩爾,微信公眾號:奇異摩爾】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

奇異摩爾攜手UALink聯(lián)盟助力AI網(wǎng)絡繁榮發(fā)展

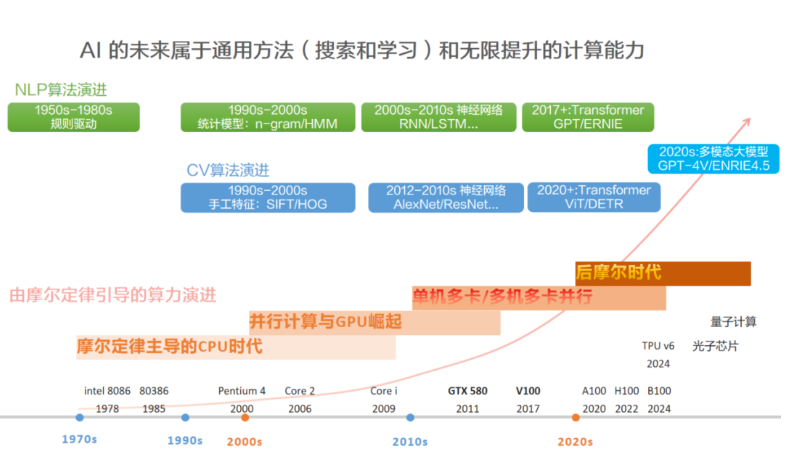

AI演進的核心哲學:使用通用方法,然后Scale Up!

奇異摩爾以互聯(lián)之長推進OISA GPU卡間互聯(lián)生態(tài)適配

奇異摩爾受邀出席第三屆HiPi Chiplet論壇

衢州市領導蒞臨奇異摩爾考察調(diào)研

奇異摩爾加入UALink加速器間互聯(lián)協(xié)議聯(lián)盟

回顧:奇異摩爾@ ISCAS 2024 :聚焦互聯(lián)技術與創(chuàng)新實踐

潤欣科技與奇異摩爾簽署CoWoS-S封裝服務協(xié)議

智原科技與奇異摩爾2.5D封裝平臺量產(chǎn)

境外SOCKS5代理:安全高效的網(wǎng)絡訪問新途徑

境外SOCKS5代理:解鎖全球網(wǎng)絡資源的新途徑

奇異摩爾專用DSA加速解決方案重塑人工智能與高性能計算

異構計算:解鎖算力潛能的新途徑

奇異摩爾分享計算芯片Scale Up片間互聯(lián)新途徑

奇異摩爾分享計算芯片Scale Up片間互聯(lián)新途徑

評論