1. RFSoC

Xilinx最新一代UltraScale+ FPGA ^[1]^ 將RF AD/DA、SerDes等系統(tǒng)完美集成在一顆芯片打造出了一個(gè)全方位的通信鏈,其中RFSoC可以支持5G無(wú)線網(wǎng)絡(luò),電纜訪問(wèn)遠(yuǎn)程物理節(jié)點(diǎn)和電子戰(zhàn)/雷達(dá)系統(tǒng),還可以應(yīng)用于測(cè)試和測(cè)量,衛(wèi)星通信,軍用無(wú)線通等。

該RFSoC具有如下特性:

8個(gè)4GSPS 或16個(gè)2GSPS 12位ADC;

8-16個(gè)6.4GSPS 14位DAC。

RFSoC輸入頻率達(dá)到GHz且位數(shù)大于12位,架構(gòu)上采時(shí)鐘直接采樣的方式,采樣后的數(shù)據(jù)送到數(shù)字進(jìn)行處理,這對(duì)采樣時(shí)鐘噪聲性能提出了非常高的要求。2018年Xilinx發(fā)表在ISSCC會(huì)議上的關(guān)于PLL的paper ^[2]^ 正是應(yīng)用于該RFSoC。

該P(yáng)LL在6.25GHz頻率下的RMS Jitter為54fs @ 10k~10MHz積分區(qū)間。論文核心內(nèi)容僅有不到一面A4紙,每句話都值得我們細(xì)細(xì)品味。下面章節(jié)將結(jié)合該論文逐一展開(kāi)PLL的噪聲優(yōu)化技術(shù)。

2. Xilinx****噪聲優(yōu)化技術(shù)

**2.1 PLL **參數(shù)

參考頻率:500MHz;輸出頻率:7.414GHz;6.25GHz RMS Jitter:54fs @ 10kHz10MHz積分區(qū)間;工藝:16nm FinFET;功耗:45mW @ 12.5GHz;面積:0.35 mm^2^。

**2.2 **帶內(nèi)噪聲的優(yōu)化

PLL參考頻率為500MHz,帶寬可以做的很高,原則上50MHz以?xún)?nèi)都合理,但帶寬過(guò)高對(duì)帶內(nèi)噪聲是不利的,過(guò)低對(duì)VCO噪聲不利,折中考慮,我個(gè)人猜測(cè)帶寬應(yīng)該在5~10MHz左右。文中也提到高帶寬下要想做低噪聲,帶內(nèi)噪聲(如PFD/CP/FBCLK/REFCLK)必須要很低。

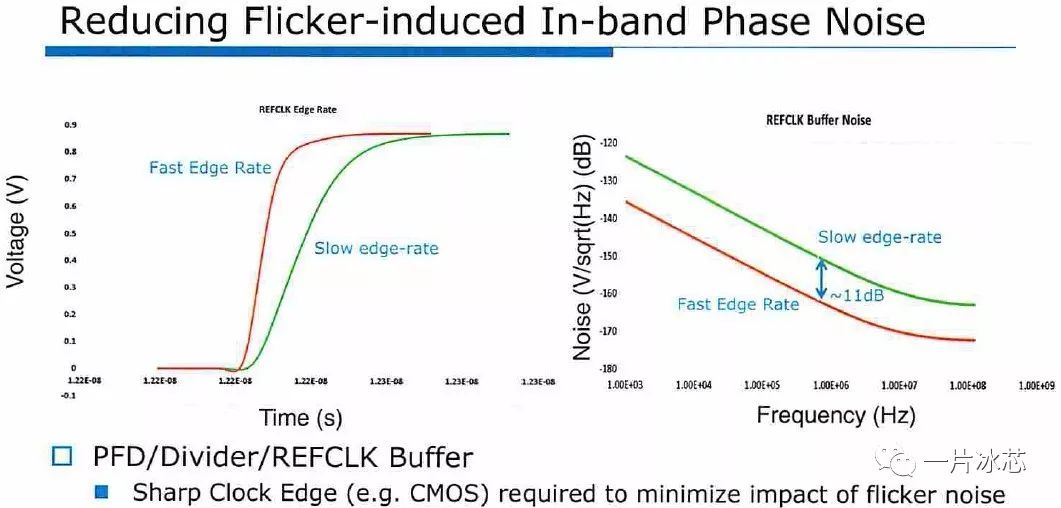

噪聲來(lái)自電平翻轉(zhuǎn)的不確定性,在閾值電壓附近,停留的時(shí)間越短噪聲越小。因此為了降低PFD和DIVIDER等CMOS電路的Jitter,需要盡量把上升/下降沿做shaper,如小于10ps;PFD消死區(qū)時(shí)間小于40ps。

Xilinx在2019年ISSCC上的報(bào)告 ^[3]^ 指出CMOS電路邊沿做Sharp后噪聲優(yōu)化了11dB,如圖1所示。

Fig1. 邊沿sharp后對(duì)帶內(nèi)噪聲的影響

2.3 CP****的噪聲優(yōu)化

CP電路輸出級(jí)采用18個(gè)slices并聯(lián)的方式,實(shí)現(xiàn)了大電流且電流可調(diào),大的動(dòng)態(tài)范圍,降低了噪聲;自偏置電流源使up/dn電流失配小于1%;CP鏡像電流源尺寸為輸出級(jí)slices的4倍,保證了較好的matching和jitter;PMOS電流鏡柵源增加RC濾波,減小了輸出噪聲;輸出級(jí)增加單位增益放大器,減小了動(dòng)態(tài)電流失配;上下電流源采用stack結(jié)構(gòu)提高了輸出阻抗并降低了噪聲。

2.4 LPF****的噪聲優(yōu)化

電阻熱噪聲與阻值成正比,因此在保證環(huán)路穩(wěn)定的前提下濾波電阻應(yīng)盡量小;電容漏電會(huì)引入spur,為減小漏電濾波電容采用MOM電容。

**2.5 **基準(zhǔn)源的優(yōu)化

LDO參考電壓來(lái)自bandgap,為了減小bandgap和LDO本身引入的噪聲,通路上增加了兩個(gè)大的RC濾波,其中LDO功率管柵端濾波電阻(為減小面積該電阻由亞閾值管實(shí)現(xiàn))高達(dá)幾M Ohm,帶寬小于10kHz。

2.6 LCVCO****的優(yōu)化

16nm FinFET工藝中PMOS管的flicker noise遠(yuǎn)大于NMOS,為減小噪聲,LCVCO有源器件采用全NMOS實(shí)現(xiàn),與CP電路類(lèi)似采用了stack結(jié)構(gòu),提高了輸出阻抗,進(jìn)一步減小了噪聲。

電容陣列由MOM電容,一個(gè)NMOS開(kāi)關(guān)(M1),兩個(gè)stack結(jié)構(gòu)的NMOS pull devices和一個(gè)反相器組成,如圖2所示。該結(jié)構(gòu)可保證電容陣列在on狀態(tài)下A,B點(diǎn)拉低,off狀態(tài)下A,B點(diǎn)拉高,提高了on/off狀態(tài)下電容陣列的Q值,優(yōu)化了LCVCO相位噪聲。

溫度補(bǔ)償電壓Vte經(jīng)RC濾波接到varactor電容,減小了噪聲,其中Vte具有正溫度系數(shù),用于補(bǔ)償LCVCO高溫下頻帶的下移。

電感的Q值越大,相位噪聲越好,一般電感的Q值在13左右,這里電感Q 值要求大于17,有可能采用平面螺旋結(jié)構(gòu),因?yàn)槠矫媛菪Y(jié)構(gòu)Q值一般大于堆疊結(jié)構(gòu)。電容陣列的引入,可使得tuningvaractor電容變小,提高了LCVCO的相位噪聲。

Fig2. LCVCO及LDO電路

**2.7 **電源和地的隔離

前面介紹為了提高數(shù)字電路噪聲性能,將數(shù)字邊沿做的更shape,使得模擬電路更易受到干擾,電路設(shè)計(jì)時(shí)CP,LPF,VCO中的NMOS采用deepnwell器件,電源也要與數(shù)字電源分開(kāi),這三個(gè)模塊采用LDO供電,這樣模擬、數(shù)字電源和地完全隔離,減小模擬、數(shù)字電路襯底和電源的相互干擾。

2.8 layout****布局

電容陣列采用圖2所示帶有二進(jìn)制權(quán)重且上下對(duì)稱(chēng)的局部布局方式;電感線圈周邊插入電源到地的decap電容且LCVCO遠(yuǎn)離數(shù)字模塊的整體布局方式。

**3. **其他噪聲優(yōu)化技術(shù)

文獻(xiàn)[4]和[5]分別為Xilinx和Samsung近兩年發(fā)表的paper,文獻(xiàn)[4]給出的Sampling Phase Detector(SPD) PLL結(jié)構(gòu)如圖3所示。引入SPD前后測(cè)試結(jié)果如圖4所示,可見(jiàn)采用SPD技術(shù)PLL在9GHz和18GHz頻點(diǎn)下RMS Jitter分別提高了200fs和230fs @ 1kHz~100MHz積分區(qū)間。

Fig3. SPD PLL結(jié)構(gòu)

Fig4. 引入SPD前后測(cè)試結(jié)果 @ 9GHz, 18GHz

文獻(xiàn)[5]采用Digital-to-Time Convert(DTC)-basedsampling analog pll結(jié)構(gòu),該結(jié)構(gòu)同樣也采用了SPD技術(shù),除此以外Samsung還采用了DTC增益校準(zhǔn),DCC校準(zhǔn),reference clock doubler,LMS算法,Sigma-Delta等技術(shù),在6.33GHz頻率下將 RMS Jitter做到了75fs @ 10kHz~10MHz積分區(qū)間,該P(yáng)LL可用于最新的5G蜂窩移動(dòng)通信。

Fig5. DTC-basedfractional-N pll

-

VCO

+關(guān)注

關(guān)注

13文章

311瀏覽量

70003 -

CMOS電路

+關(guān)注

關(guān)注

0文章

49瀏覽量

11778 -

PLL電路

+關(guān)注

關(guān)注

0文章

92瀏覽量

6717 -

熱噪聲

+關(guān)注

關(guān)注

0文章

47瀏覽量

8325 -

濾波電阻

+關(guān)注

關(guān)注

0文章

4瀏覽量

2377

發(fā)布評(píng)論請(qǐng)先 登錄

具有時(shí)鐘分配的1.4GHz低相位噪聲和低抖動(dòng)PLL的演示板DC1795A

評(píng)估低抖動(dòng)PLL時(shí)鐘發(fā)生器的電源噪聲抑制性能

MAX3625B 抖動(dòng)僅為0.36ps的PLL時(shí)鐘發(fā)生器

模擬PLL,模擬PLL是什么意思

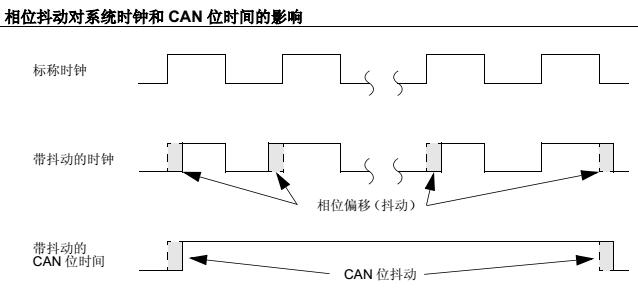

PLL抖動(dòng)及其對(duì)ECAN?技術(shù)通信的影響

評(píng)估低抖動(dòng)PLL時(shí)鐘發(fā)生器的電源噪聲抑制

評(píng)估低抖動(dòng)PLL時(shí)鐘發(fā)生器的電源噪聲抑制

如何建立一個(gè)簡(jiǎn)單的PLL電路

了解鎖相環(huán)(PLL)瞬態(tài)響應(yīng) 如何優(yōu)化鎖相環(huán)(PLL)的瞬態(tài)響應(yīng)?

如何評(píng)估分布式PLL系統(tǒng)的相位噪聲?

LMK04208具有雙環(huán)PLL的低噪聲時(shí)鐘抖動(dòng)消除器數(shù)據(jù)表

PLL抖動(dòng)對(duì)GSPS ADC SNR及性能優(yōu)化的影響

鎖相環(huán)PLL的噪聲分析與優(yōu)化 鎖相環(huán)PLL與相位噪聲的關(guān)系

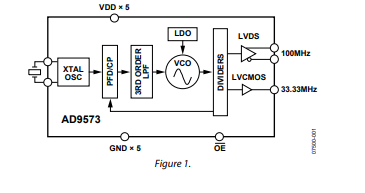

AD9573 PCI-Express時(shí)鐘發(fā)生器IC,PLL內(nèi)核,分頻器,兩路輸出技術(shù)手冊(cè)

如何做一個(gè)低抖動(dòng)的PLL?PLL噪聲優(yōu)化

如何做一個(gè)低抖動(dòng)的PLL?PLL噪聲優(yōu)化

評(píng)論