概述

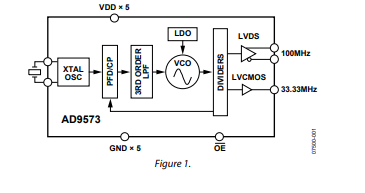

AD9573是一款高度集成的雙路輸出時鐘發生器 , 包括一個針對PCI-e應用而優化的片內PLL內核 。 整數N分頻PLL設計基于ADI公司成熟的高性能、低抖動頻率合成器系列 , 可實現線路卡的較高性能 。 這款器件也適合相位噪聲和抖動要求嚴格的其它應用。

數據表:*附件:AD9573 PCI-Express時鐘發生器IC,PLL內核,分頻器,兩路輸出技術手冊.pdf

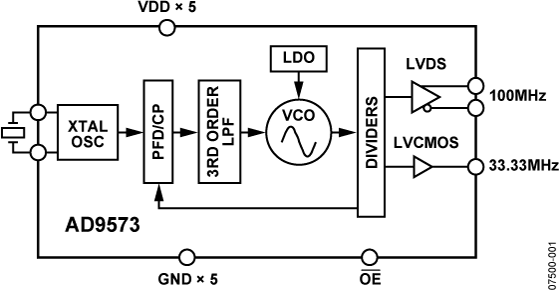

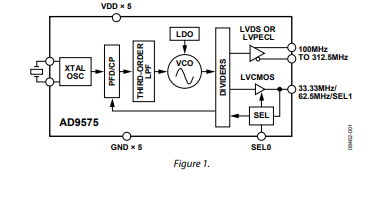

PLL部分由低噪聲鑒頻鑒相器(PFD)、精密電荷泵、低相位噪聲壓控振蕩器(VCO)、預編程的反饋分頻器和輸出分頻器組成。

通過連接一個外部25 MHz晶振,可以將100 MHz和33.33 MHz輸出頻率鎖定至輸入參考。輸出分頻比和反饋分頻比可針對所要求的輸出速率進行預編程。無需外部環路濾波器,從而節省寶貴的設計時間和電路板空間。

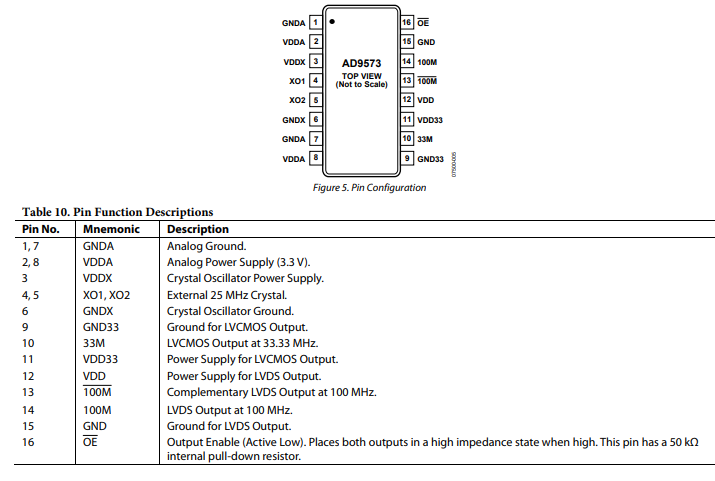

AD9573提供16引腳、4.4 mm × 5.0 mm TSSOP封裝,可以采用3.3 V單電源供電。溫度范圍為?40°C至+85°C。

應用

特性

- 完全集成的VCO/PLL內核

均方根抖動:0.54 ps(12 kHz至20 MHz)

輸入晶振頻率:25 MHz - 針對100 MHz、33.33 MHz提供預設分頻比

- LVDS/LVCMOS 輸出格式

- 集成環路濾波器

- 4.4 mm × 5.0 mm TSSOP封裝,節省空間

- 功耗:0.235 W

- 3.3 V 工作電壓

框圖

引腳配置描述

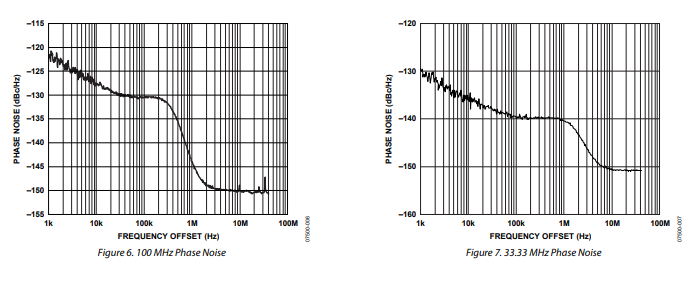

典型性能特征

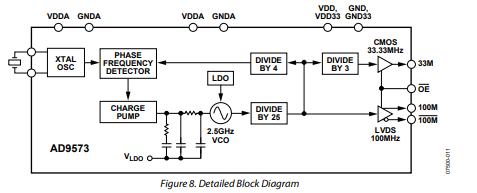

操作理論

圖8展示了AD9573的框圖。該芯片具有一個鎖相環(PLL)內核,經過配置可生成PCI - Express所需的特定時鐘頻率,無需用戶進行任何編程。此PLL基于亞德諾半導體(Analog Devices)成熟的合成器技術,其卓越的相位噪聲性能值得關注。AD9573集成度很高,包含環路濾波器、電源噪聲抗擾度調節器、所有必要的分頻器、輸出緩沖器以及一個晶體振蕩器。用戶只需提供25 MHz的外部晶體,即可實現完整的PCIe時鐘解決方案,無需處理器干預。

輸出

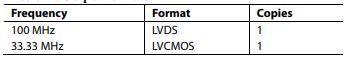

表11總結了可用的輸出。

表11. 輸出格式

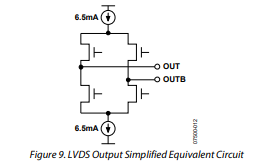

圖9展示了LVDS輸出的簡化等效電路。100 MHz輸出被描述為LVDS,是因為它采用了LVDS驅動器拓撲結構。不過,其電平為HCSL兼容,因此與標準LVDS不同。輸出電流有所增加,以提供比標準LVDS更大的輸出擺幅。

圖9. LVDS輸出簡化等效電路

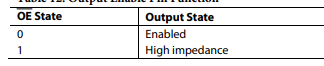

根據表12連接OE引腳,可將兩個輸出都置于高阻抗狀態。該引腳有一個50 kΩ的下拉電阻。

表12. 輸出使能引腳功能

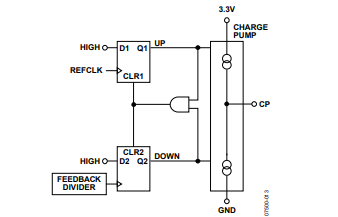

鑒頻鑒相器(PFD)和電荷泵

PFD接收來自參考時鐘和反饋分頻器的輸入,產生一個與兩者之間相位和頻率差成比例的輸出。圖10展示了簡化示意圖。

圖10. PFD簡化示意圖及時序(鎖定狀態)

電源

AD9573的VDD需要3.3 V ± 10%的電源。規格部分的表格給出了AD9573在該電源電壓范圍內的性能預期。相對于地,VDD或VDDA引腳上的絕對最大電壓范圍為(-0.3 V) - (+3.6 V),此范圍絕不能被超出。

在PCB布局中應遵循良好的工程實踐。電源走線和PCB接地層的電源應在PCB上用足夠的電容(>10 μF)旁路。AD9573應使用足夠的電容(0.1 μF)在所有電源引腳處盡可能靠近引腳進行去耦。

-

發生器

+關注

關注

4文章

1399瀏覽量

62513 -

時鐘發生器

+關注

關注

1文章

223瀏覽量

68885 -

ad9573

+關注

關注

0文章

3瀏覽量

4363

發布評論請先 登錄

AD9571ACPZPEC時鐘發生器銷售

AD9520-3BCPZ時鐘發生器

低抖動高精度時鐘發生器MAX3625B相關資料分享

MAX3679A高性能四路輸出時鐘發生器(Maxim)

PCI時鐘發生器IC鎖相環分頻器兩個輸出ad9573數據表

AD9573 PCI-Express時鐘發生器IC,PLL內核,分頻器,兩路輸出

AD9510:1.2 GHz時鐘分配IC,PLL內核,分頻器,延遲調整,8路輸出

時鐘發生器由哪些部分組成?鎖相環pll的特點是什么?

具有兩個獨立PLL、八路輸出、集成EEPROM的LMK03328超低抖動時鐘發生器數據表

CDCM61002兩路輸出、集成VCO、低抖動時鐘發生器數據表

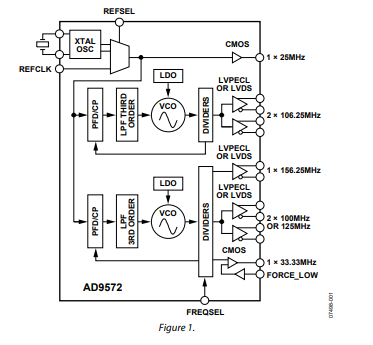

AD9572光纖通道/以太網時鐘發生器IC,PLL內核,分頻器,7路時鐘輸出技術手冊

AD9573 PCI-Express時鐘發生器IC,PLL內核,分頻器,兩路輸出技術手冊

AD9573 PCI-Express時鐘發生器IC,PLL內核,分頻器,兩路輸出技術手冊

評論