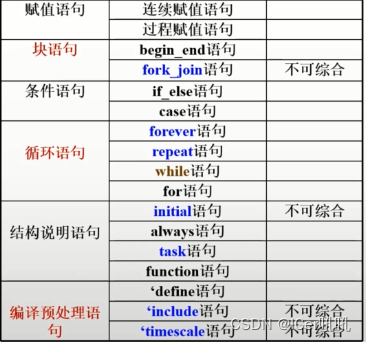

不可綜合語句經(jīng)常用在測試文件中,未注明的語句均是可綜合的

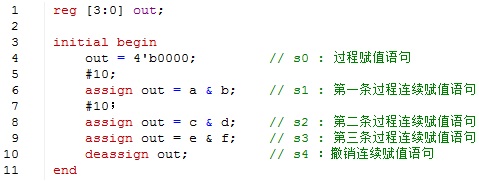

賦值語句

1.連續(xù)賦值語句——assign語句,用于對wire型變量賦值,是描述組合邏輯最常用的方法之一。

例:assign c=a&b; // a,b,c 均為wire型變量

2.過程賦值語句——用于對reg型變量賦值,有兩種方法:

非阻塞賦值方法:符號<=

阻塞賦值方法:符號為=

阻塞與非阻塞賦值的區(qū)別:

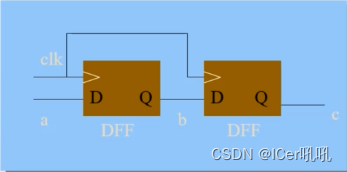

1.非阻塞賦值方式:

always @(posedge clk)

begin

b <= a;

c <= b;

end

非阻塞賦值在塊結(jié)束時才完成賦值操作(c的值比b的值落后一個時鐘周期)

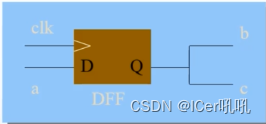

2.阻塞賦值方式

always @(posedge clk)

begin

b = a;

c = b;

end

阻塞賦值語句在該語句結(jié)束時就完成賦值操作(在塊語句中,如果有多條阻塞賦值語句,在前面的賦值語句沒有完成之前,后面的語句就不能被執(zhí)行,就像被阻塞一樣,因此稱為阻塞賦值方式。這里的c和b的值一樣。)

非阻塞賦值于阻塞賦值方式的主要區(qū)別:

非阻塞賦值:b的值被賦成新值a的操作,并不是立刻完成,而是在塊結(jié)束時才完成;

塊內(nèi)的多條語句在塊結(jié)束時同時賦值。

硬件有對應(yīng)電路。

阻塞賦值: b的值立刻被賦成新值a;

完成該賦值語句后才能執(zhí)行下一條語句;

硬件沒有對應(yīng)的電路,因而綜合結(jié)果未知。

塊語句

用來將兩條或多條語句組合在一起,使其在格式上更像一條語句,以增加程序的可讀性

塊語句有兩種:

begin...end語句——標示順序執(zhí)行的語句

fork...join語句——標示并行執(zhí)行的語句(不可綜合)

begin...end:

塊內(nèi)的語句是順序執(zhí)行的

每條語句的延遲時間是相對于前一條語句的仿真時間而言的

直到最后一條語句執(zhí)行完,程序流程控制才能跳出該順序塊

塊內(nèi)語句可以是參數(shù)聲明,reg變量聲明,integer變量聲明,real變量聲明語句

#可以用在語句塊中表示延遲,(在模塊調(diào)用過程中使用#表示參數(shù)的傳遞)

fork...join:

塊內(nèi)的語句是并行執(zhí)行的

每條語句的延遲時間是相對于開始仿真時間而言的

如何跳出該順序塊由(fork...join,fork...join_any,fork...join_none)決定

塊內(nèi)語句可以是參數(shù)聲明,reg變量聲明,integer變量聲明,real變量聲明語句,time變量聲明語句和事件(event)說明語句。

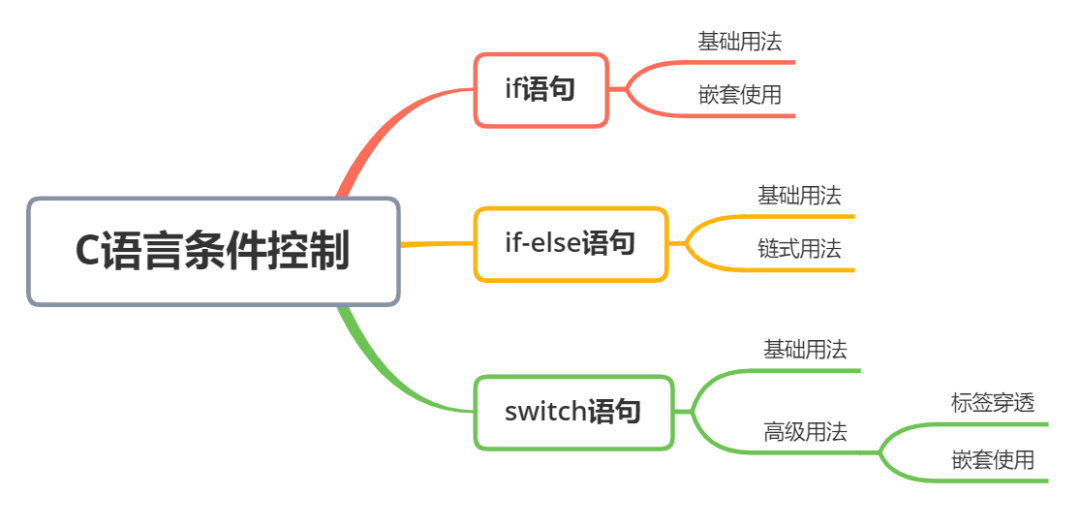

條件語句

條件語句分為兩種:if...else語句和case語句

它們都是順序語句,應(yīng)該放在“always”塊內(nèi);

if...else:

判定給出的條件是否滿足,根據(jù)判定的結(jié)果(真或假)決定執(zhí)行給出的兩種操作之一。

if...else語句有3中形式:

其中,表達式為邏輯表達式或關(guān)系表達式,或一位的變量

若表達的值為0或者z,則判定的結(jié)果為假,若為1,則加過為真

語句分為單句,也可分為多句;多句一定用“begin...end”語句括起來,形成一個符合塊語句

方式1:

if (表達式) 語句1;

方式2:

if(表達式) 語句1;

else 語句2;

方式3:

if(表達式1) 語句1;

else if(表達式2) 語句2;

...

else if(表達式n) 語句n;

允許一定形式的表達式簡寫方式,如:

if(expression) 等同于if(expression ==1)

if(!expression) 等同于if(expression!=1)

if 語句可以嵌套

若if和else的數(shù)目不一樣,要使用“begin..end”語句來確定if于else的配對關(guān)系。

嵌套語句:

if(表達式1)

if(表達式2)語句1;

else 語句2;

else

if(表達式3) 語句3;

else 語句4;

module count60(qout, cout,data,load,cin,reset,clk); output[7:0] qout; output cout; input [7:0] data; input load,cin,reset,clk; reg [7:0] qout; always@(posedge clk) begin if(reset) qout = 0; //同步復(fù)位 else if(load) qout = data; //同步置數(shù) else if (cin) /如果cin為1,執(zhí)行加1計數(shù) begin if (qout[3:0]==9) begin qout[3:0]=0; if (qout[7:4]==5) qout[7:4] = 0; else qout[7:4] =qout[7:4]+1; end else qout[3:0]=qout[3:0]+1; end end assign cout = ((qout ==8'h59)&cin)?1:0; //產(chǎn)生進位輸出 endmodulecase語句

當敏感表達式取不同的值時,執(zhí)行不同的語句;

功能:當某個(控制)信號取不同的值時,給另一個(輸出)信號賦不同的值。常用于多條件譯碼電路(如譯碼器,數(shù)據(jù)選擇器,狀態(tài)機,微處理器)

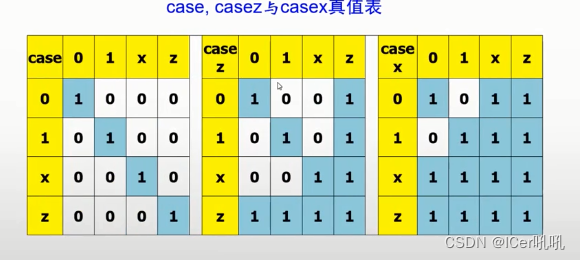

case語句有三種不同形式:case,casez,casex

說明:

其中“敏感表達式”有稱為“控制表達式”,通常表示為控制信號的某些位。

值1—值n稱為分支表達式,用控制信號的具體狀態(tài)值表示,因此有分為常量表達式。

default項可有可無,一個case語句中只有一個default項;

值1—值n必須互不相同,否則矛盾;

值1—值n的位寬必須相等,且與控制表達式的位寬相同。

casez與casex語句:

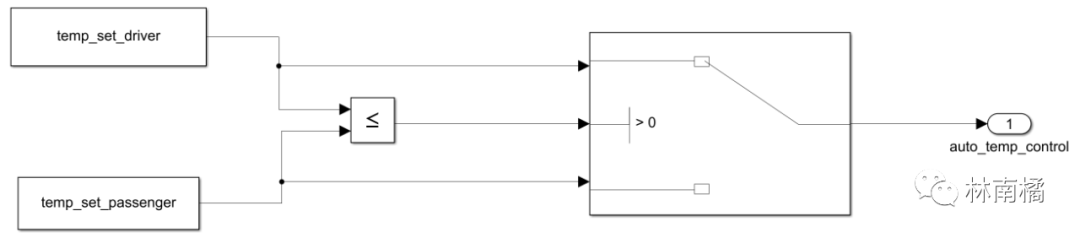

使用條件語句的注意事項:

- 應(yīng)列出所有條件分支,否則當條件不滿足時,編譯器會生成一個鎖存器保持原值;

- 這一點可用于設(shè)計時序電路,如計數(shù)器:條件滿足時加1,否則保持原值不變;

- 在組合電路設(shè)計中,應(yīng)避免生成隱含的鎖存器,有效的方法是在if語句最后寫上else,在case語句最后寫上default項。

審核編輯:湯梓紅

-

IC

+關(guān)注

關(guān)注

36文章

6098瀏覽量

178454 -

電路設(shè)計

+關(guān)注

關(guān)注

6700文章

2524瀏覽量

212055 -

Verilog

+關(guān)注

關(guān)注

29文章

1366瀏覽量

111870 -

變量

+關(guān)注

關(guān)注

0文章

614瀏覽量

28831 -

符號

+關(guān)注

關(guān)注

0文章

55瀏覽量

4537

原文標題:IC學霸筆記 | Verilog賦值語句、塊語句、條件語句

文章出處:【微信號:IC修真院,微信公眾號:IC修真院】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

C語言中if語句、if-else語句和switch語句詳解

Verilog中的賦值語句的區(qū)別

Verilog的兩種塊語句解析

Verilog的塊語句

Verilog的塊語句fork...join 和 begin...end

詳解Python條件語句

Verilog中的If語句和case語句介紹

詳解Verilog賦值語句、塊語句、條件語句

詳解Verilog賦值語句、塊語句、條件語句

評論