1. 連續(xù)賦值語(yǔ)句(Continuous Assignments)

連續(xù)賦值語(yǔ)句是Verilog數(shù)據(jù)流建模的基本語(yǔ)句,用于對(duì)線網(wǎng)進(jìn)行賦值,等價(jià)于門級(jí)描述,是從更高的抽象角度來(lái)對(duì)電路進(jìn)行描述。連續(xù)賦值語(yǔ)句必須以關(guān)鍵詞assign開始。

連續(xù)復(fù)制的主要特點(diǎn)是:

連續(xù)賦值語(yǔ)句的左值可以是一下類型之一:

①標(biāo)量線網(wǎng)

②向量線網(wǎng)

③矩陣中的一個(gè)元素(該矩陣可以是標(biāo)量線網(wǎng)類型的,也可以是向量線網(wǎng)類型的)

④向量線網(wǎng)的某一位

⑤向量線網(wǎng)的部分位

以及上述各種類型的拼接體

但是,不能是向量或向量寄存器。

連續(xù)賦值語(yǔ)句總是處于激活狀態(tài)。只要任意一個(gè)操作數(shù)發(fā)生變化,表達(dá)式就會(huì)被立即重新計(jì)算,并且將結(jié)果賦給等號(hào)左邊的線網(wǎng)。

操作數(shù)可以是標(biāo)量或向量的線網(wǎng)或寄存器,也可以是函數(shù)的調(diào)用。

賦值延遲用于控制對(duì)線網(wǎng)賦予新值的時(shí)間,根據(jù)仿真時(shí)間單位進(jìn)行說(shuō)明。賦值延遲類似于門延遲,對(duì)于描述實(shí)際電路中的時(shí)序是非常重要的。

2. 過程賦值語(yǔ)句(Procedural Assignments)

過程賦值語(yǔ)句的更新對(duì)象是寄存器、整數(shù)、實(shí)數(shù)或時(shí)間變量等。這些類型的變量在被賦值后,其值將保持不變,直到被其他過程賦值語(yǔ)句賦予新值。過程賦值語(yǔ)句只有在執(zhí)行到的時(shí)候才會(huì)起作用。過程賦值語(yǔ)句只能在initial或always語(yǔ)句內(nèi)進(jìn)行賦值,只能對(duì)變量數(shù)據(jù)類型賦值,同時(shí)initial和always中只能使用過程賦值語(yǔ)句。

過程賦值語(yǔ)句的左值可以是以下類型之一:

①reg、整形數(shù)、實(shí)型數(shù)、時(shí)間寄存器變量或存儲(chǔ)器單元

②上述各種類型的位選(例如:addr[3])

③上述各種類型的域選(例如:addr[31:16])

④上面三種類型的拼接

過程性賦值語(yǔ)句包括兩種類型的賦值語(yǔ)句:阻塞賦值(=)和非阻塞賦值(<=)(其主要區(qū)別詳見各類Verilog參考書,這里不再詳述)。

3. 過程連續(xù)賦值語(yǔ)句(Procedural Continuous Assignments)

過程連續(xù)賦值是在過程塊內(nèi)對(duì)變量或線網(wǎng)型數(shù)據(jù)進(jìn)行連續(xù)賦值,是一種過程性賦值,換言之,過程性連續(xù)賦值語(yǔ)句是一種能夠在always或initial語(yǔ)句塊中出現(xiàn)的語(yǔ)句。這種賦值可以改寫(Override)所有其他語(yǔ)句對(duì)線網(wǎng)或者變量的賦值。這種賦值允許賦值表達(dá)式被連續(xù)的驅(qū)動(dòng)進(jìn)入到變量或線網(wǎng)中去。

過程連續(xù)賦值語(yǔ)句有兩種類型:

①assign和deassign過程性語(yǔ)句:對(duì)變量進(jìn)行賦值。

②force和release過程性語(yǔ)句:主要用于對(duì)線網(wǎng)賦值,也可以用于對(duì)變量賦值。

3.1 assign和deassign語(yǔ)句

assign和deassign語(yǔ)句構(gòu)成了一類過程性連續(xù)賦值語(yǔ)句,只能用于對(duì)寄存器類型變量的連續(xù)賦值操作,不能用來(lái)對(duì)線網(wǎng)類型數(shù)據(jù)進(jìn)行連續(xù)賦值操作。

①assign語(yǔ)句

語(yǔ)法:assign <寄存器類型變量> =<賦值表達(dá)式>;

assign在執(zhí)行時(shí),寄存器類型變量將由賦值表達(dá)式進(jìn)行連續(xù)驅(qū)動(dòng),即進(jìn)入連續(xù)賦值狀態(tài)。如果此時(shí)有普通的過程賦值語(yǔ)句對(duì)該寄存器變量進(jìn)行過程賦值操作,由于過程連續(xù)賦值語(yǔ)句assign的優(yōu)先級(jí)高于普通過程賦值語(yǔ)句,所以出于連續(xù)賦值狀態(tài)的寄存器變量將忽略普通過程賦值語(yǔ)句對(duì)它的過程賦值操作,其邏輯狀態(tài)仍然由過程連續(xù)賦值語(yǔ)句內(nèi)的賦值表達(dá)式所決定。

如果先后有兩條assign語(yǔ)句對(duì)同一寄存器變量進(jìn)行了過程連續(xù)賦值操作,那么第二條assign的執(zhí)行將覆蓋第一條assign的執(zhí)行效果。

②deassign語(yǔ)句

語(yǔ)法:deassign <寄存器類型變量>;

deassign語(yǔ)句是一條撤銷連續(xù)賦值語(yǔ)句,用來(lái)結(jié)束對(duì)變量的連續(xù)賦值操作。當(dāng)deassign語(yǔ)句執(zhí)行后,原來(lái)由assign語(yǔ)句對(duì)該變量進(jìn)行的連續(xù)賦值操作將失效,寄存器變量被連續(xù)賦值的狀態(tài)將得到解除,該變量又可以由普通過程賦值語(yǔ)句進(jìn)行賦值操作了。這里需要注意一點(diǎn),當(dāng)執(zhí)行該語(yǔ)句撤銷對(duì)某寄存器變量的連續(xù)賦值后,該寄存器變量仍將保持使用該語(yǔ)句之前的原有值。

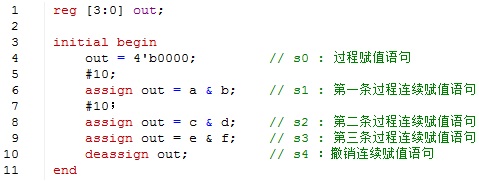

③示例:

上述語(yǔ)句執(zhí)行過程如下:

s0:在0時(shí)刻,out被賦值為0,并且保持這個(gè)取值;

s1:在10時(shí)刻,s1開始執(zhí)行,實(shí)現(xiàn)了對(duì)變量out的連續(xù)賦值操作,因此從10時(shí)刻開始,out將處于連續(xù)賦值狀態(tài);

s2:在20時(shí)刻,s2開始執(zhí)行,將覆蓋s1產(chǎn)生的作用,所以從20時(shí)刻開始,out將由c & d連續(xù)驅(qū)動(dòng);

s3:s3操作覆蓋掉s2操作;

s4:當(dāng)deassign語(yǔ)句得到執(zhí)行,變量out連續(xù)賦值狀態(tài)被解除,其取值將保持最后一次assign語(yǔ)句賦予的值,即“e & f”;

3.2 force和release語(yǔ)句

force和release語(yǔ)句與assign和deassign語(yǔ)句類似,也是一種過程連續(xù)賦值語(yǔ)句。這組賦值語(yǔ)句不僅能對(duì)寄存器類型變量產(chǎn)生作用,還能對(duì)線網(wǎng)類型數(shù)據(jù)進(jìn)行連續(xù)賦值操作。

①force語(yǔ)句

語(yǔ)法:force <寄存器變量或者線網(wǎng)數(shù)據(jù)> = <賦值表達(dá)式>>;

force語(yǔ)句應(yīng)用于寄存器類型變量時(shí),則在force語(yǔ)句執(zhí)行后,該寄存器變量將強(qiáng)制由進(jìn)行連續(xù)驅(qū)動(dòng),進(jìn)入被連續(xù)賦值的狀態(tài),此時(shí)將忽略其他較低優(yōu)先級(jí)的賦值語(yǔ)句對(duì)該寄存器變量的賦值操作,直到執(zhí)行一條release語(yǔ)句來(lái)釋放對(duì)該寄存器變量的連續(xù)賦值為止。

force語(yǔ)句應(yīng)用于線網(wǎng)數(shù)據(jù)時(shí),則force語(yǔ)句執(zhí)行后,對(duì)應(yīng)的線網(wǎng)數(shù)據(jù)將得到的連續(xù)驅(qū)動(dòng),此時(shí)將忽略該線網(wǎng)數(shù)據(jù)上較低優(yōu)先級(jí)的驅(qū)動(dòng),直到有一條release語(yǔ)句執(zhí)行為止。

②release語(yǔ)句

語(yǔ)法:release <寄存器變量或者線網(wǎng)數(shù)據(jù)>;

release語(yǔ)句執(zhí)行后,原先由force語(yǔ)句對(duì)變量或者線網(wǎng)施加的過程連續(xù)賦值將失效,變量將解除被被連續(xù)賦值的狀態(tài),較低優(yōu)先級(jí)的賦值語(yǔ)句的賦值操作將有效。

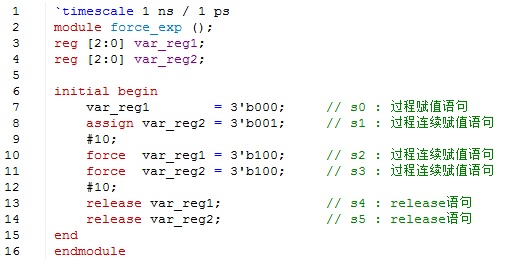

③示例:

s0:實(shí)現(xiàn)對(duì)變量var_reg1的過程賦值操作,即var_reg1被賦值為3'b000;

s1:執(zhí)行assign過程連續(xù)賦值語(yǔ)句,用來(lái)實(shí)現(xiàn)對(duì)變量var_reg2的連續(xù)賦值,從而var_reg2將被連續(xù)賦值為3'b001;

s2:在執(zhí)行本條語(yǔ)句時(shí),var_reg1未被assign語(yǔ)句進(jìn)行過連續(xù)賦值操作,因此var_reg1被force連續(xù)賦值為3'b100;

s3:執(zhí)行本條語(yǔ)句后,var_reg2被force連續(xù)賦值為3'b100;

s4:執(zhí)行本條語(yǔ)句時(shí),因?yàn)樽兞縱ar_reg1將退出連續(xù)賦值的狀態(tài),因?yàn)関ar_reg1未曾被assign語(yǔ)句進(jìn)行過連續(xù)賦值操作,故var_reg1取值保持不變,即保持force狀態(tài)時(shí)的值3'b100;

s5:執(zhí)行本語(yǔ)句時(shí),因?yàn)関ar_reg2在執(zhí)行s3之前已經(jīng)由s1實(shí)現(xiàn)了連續(xù)賦值,所以在本條語(yǔ)句s5執(zhí)行后,變量var_reg2將恢復(fù)到由assign語(yǔ)句s1確定的連續(xù)賦值狀態(tài),即3'b001;

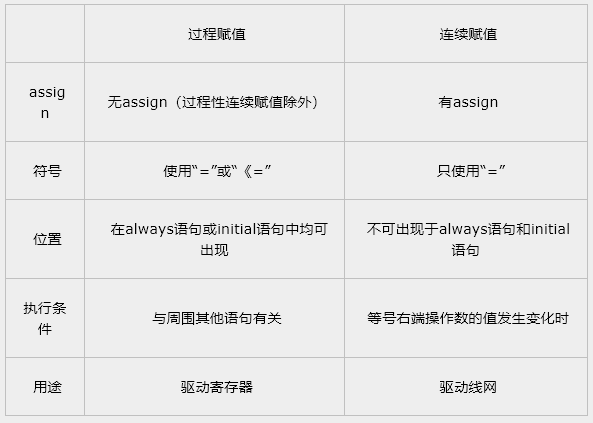

4. 賦值語(yǔ)句的區(qū)別

4.1 連續(xù)賦值語(yǔ)句和過程賦值語(yǔ)句之間的區(qū)別

? 連續(xù)賦值語(yǔ)句由assign來(lái)標(biāo)示,而過程賦值語(yǔ)句不能包含這個(gè)關(guān)鍵詞;

? 連續(xù)賦值語(yǔ)句中左側(cè)的數(shù)據(jù)類型必須是線網(wǎng)數(shù)據(jù)類型,而過程賦值語(yǔ)句中的被賦值數(shù)據(jù)類型則必須是寄存器類型的變量;

? 連續(xù)賦值語(yǔ)句不能出現(xiàn)在過程塊(initial或always)中,而過程賦值語(yǔ)句可以;

? 連續(xù)賦值語(yǔ)句主要用來(lái)對(duì)組合邏輯電路進(jìn)行建模以及對(duì)線網(wǎng)數(shù)據(jù)間的連接進(jìn)行描述,而過程賦值語(yǔ)句主要用來(lái)對(duì)時(shí)序邏輯電路進(jìn)行行為描述;

? 連續(xù)賦值語(yǔ)句對(duì)被賦值線網(wǎng)型數(shù)據(jù)的賦值是“連續(xù)”的(即賦值表達(dá)式的任何變化都會(huì)在立刻反應(yīng)在線網(wǎng)數(shù)據(jù)的取值上),而過程性賦值語(yǔ)句,只有在過程賦值語(yǔ)句被執(zhí)行時(shí)才執(zhí)行賦值操作,語(yǔ)句執(zhí)行完后被賦值變量的取值不再受到賦值表達(dá)式的影響(注意這里的一次是指:在initial塊中,過程性賦值只順序執(zhí)行一次,而在always塊中,每一次滿足always的條件時(shí),都要順序執(zhí)行一次該always塊中的語(yǔ)句。)。

? 連續(xù)賦值與過程賦值的區(qū)別:

4.2 過程連續(xù)賦值語(yǔ)句和連續(xù)賦值語(yǔ)句之間的區(qū)別

? 過程連續(xù)賦值語(yǔ)句只能用在過程塊(initial過程快或always過程塊)內(nèi),而連續(xù)賦值語(yǔ)句不能出現(xiàn)在過程塊中。

? 過程連續(xù)賦值語(yǔ)句可以對(duì)寄存器類型變量進(jìn)行連續(xù)賦值(其中force-release語(yǔ)句還可以對(duì)線網(wǎng)進(jìn)行連續(xù)賦值),但是其賦值目標(biāo)不能是變量或線網(wǎng)的某一位或某幾位,而連續(xù)賦值語(yǔ)句只能對(duì)線網(wǎng)數(shù)據(jù)進(jìn)行賦值,賦值目標(biāo)可以是線網(wǎng)型數(shù)據(jù)的某一位或某幾位。

-

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7636瀏覽量

166414 -

Verilog

+關(guān)注

關(guān)注

28文章

1366瀏覽量

111821

發(fā)布評(píng)論請(qǐng)先 登錄

詳解TIA Portal SCL編程語(yǔ)言中的IF語(yǔ)句

在testbench中如何使用阻塞賦值和非阻塞賦值

FPGA Verilog HDL語(yǔ)法之編譯預(yù)處理

Verilog中signed和$signed()的用法

淺談Verilog和VHDL的區(qū)別

Verilog 電路仿真常見問題 Verilog 在芯片設(shè)計(jì)中的應(yīng)用

Verilog 與 ASIC 設(shè)計(jì)的關(guān)系 Verilog 代碼優(yōu)化技巧

Verilog 測(cè)試平臺(tái)設(shè)計(jì)方法 Verilog FPGA開發(fā)指南

Verilog與VHDL的比較 Verilog HDL編程技巧

Verilog HDL的基礎(chǔ)知識(shí)

Verilog中的賦值語(yǔ)句的區(qū)別

Verilog中的賦值語(yǔ)句的區(qū)別

評(píng)論