1. 塊語句有兩種,一種是 begin-end 語句, 通常用來標(biāo)志()執(zhí)行的語句;一種是 fork-join 語句,通常用來標(biāo)志()執(zhí)行的語句。

答案:順序,并行

解析:

(1)begin_end順序塊,用于將多條語句組成順序塊,語句按順序一條一條執(zhí)行(除了帶有內(nèi)嵌延遲控制的非阻塞賦值語句),每條語句的延遲時間是相對于由上一條語句的仿真時間而言;

(2)fork-join并行塊,塊內(nèi)語句同時執(zhí)行。

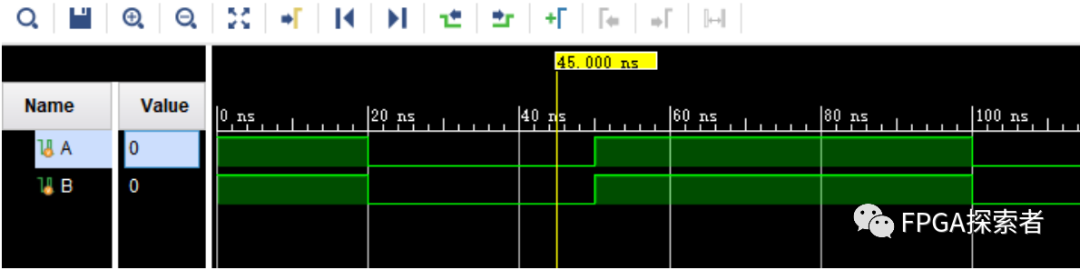

2. 塊語句,下面這段語句中,第 40 時刻上,A、B 的值各是多少?

reg A;reg B;initial beginforkbeginA = 1;#20 A = 0;#30A=1;#50 A = 0;endbeginB = 1;#20 B = 0;#30 B = 1;#50 B = 0;endjoinend

答案:A = 0,B = 0

解析:

塊語句有兩種,begin...end 和 fork...join,其中 fork...join 是并行塊,begin...end 是順序執(zhí)行塊,可以相互嵌套。

上面,兩個 begin...end 之間是并行的,而各自 begin...end 內(nèi)部是順序執(zhí)行,A 和 B 的賦值邏輯是一樣的,所以要么都是 1,要么都是 0。

按照順序執(zhí)行,A 前 20 個時間單位是 1,然后持續(xù) 30 個時間單位的 0,所以 40 時刻是 0,同理 B 也是 0。

審核編輯 :李倩

-

Verilog

+關(guān)注

關(guān)注

28文章

1365瀏覽量

111749

原文標(biāo)題:Verilog 的塊語句 fork...join 和 begin...end

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

詳解TIA Portal SCL編程語言中的IF語句

FPGA Verilog HDL語法之編譯預(yù)處理

尋找verilog高手,有報酬

Verilog 與 ASIC 設(shè)計的關(guān)系 Verilog 代碼優(yōu)化技巧

Verilog 測試平臺設(shè)計方法 Verilog FPGA開發(fā)指南

Verilog與VHDL的比較 Verilog HDL編程技巧

Verilog硬件描述語言參考手冊

Verilog HDL的基礎(chǔ)知識

如何利用Verilog-A開發(fā)器件模型

Verilog的塊語句

Verilog的塊語句

評論