本文主要介紹verilog常用的循環語句,循環語句的用途,主要是可以多次執行相同的代碼或邏輯。

verilog的循環語句主要有:for循環、while循環、foever循環和repeat循環。

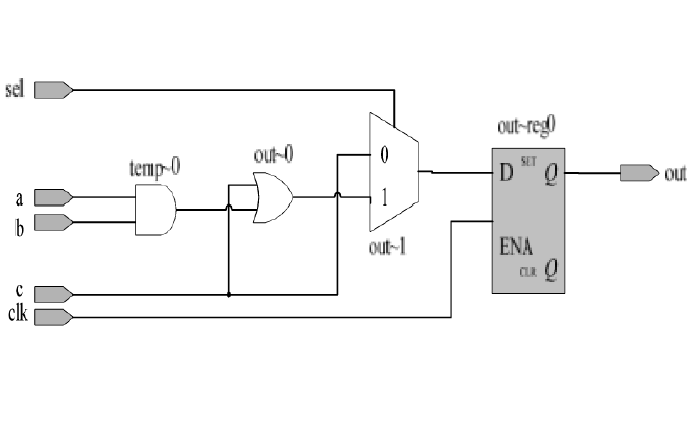

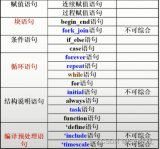

注意注意,for循環在正式FPGA設計中部分情況下可綜合,其余幾個循環語句均不可綜合,主要用于testbench。

一、For循環

for 循環會將一段代碼執行固定次數。

雖然它通常用于testbench,但也可以在可綜合的 verilog 代碼中使用,比如 for 循環處理verilog數組。

1、語法

for (

說明:

更新循環變量,注意只能用類似i=i+1或i=i-1。

2、代碼示例

for 循環實現移位寄存器

reg [5:0] shift [0:3];

wire [5:0] init_data = 'd10;

wire [6*4-1] shift_com_w;

//將輸入賦值給數組的第一個數

shift[0] <= init_data;

//使用for循環語句來將數組整體向左移動

for (i = 1; i < 4; i = i + 1) begin

shift[i] <= shift[i-1];

end

//合并數組,易于輸出模塊

for (i = 0; i < 4; i = i + 1) begin

assign shift_com_w[i*6+:6] = shift[i];

end

二、Forever循環

verilog 中的forever循環會創建一個連續執行的代碼塊,并無限循環。

forever循環只能在testbench中使用,常用于生成激勵時鐘信號。 注意forever循環無法被綜合。

1、語法

forever begin

// 循環執行的語句

end

3、代碼示例

創建一個10Mhz的時鐘

initial begin

clk = 1'b0;

forever begin

#5 clk = ~clk;

end

end

三、Repeat循環

repeat循環執行指定次數的循環代碼塊。 注意該語句不可綜合。

1、語法

repeat (

說明: 用來確定重復循環的次數

2、代碼示例

檢測到上升沿,信號翻轉一次。

repeat (6) begin //重復6次

@(posedge sig_a) //上升沿

sig_b = ~sig_b; //翻轉

end

四、While 循環

while循環的每次迭代之前都會判斷指定條件是否滿足,如果為真,就執行條件內的循環代碼塊; 否則,就不會執行。 注意該語句不可綜合。

1、語法

while

說明: 循環執行條件。

2、代碼示例

創建一個從 0 到 3 的integer型變量,然后在循環的每次迭代中打印這個變量的值。

integer i;

while (i < 4) begin

$display("i = %0d", i);

i = i + 1;

end

-

FPGA

+關注

關注

1645文章

22040瀏覽量

618202 -

FPGA設計

+關注

關注

9文章

428瀏覽量

27340 -

Verilog

+關注

關注

29文章

1367瀏覽量

112251 -

代碼

+關注

關注

30文章

4900瀏覽量

70690 -

變量

+關注

關注

0文章

614瀏覽量

28944

發布評論請先 登錄

verilog中generate語句的用法分享

verilog是什么_verilog的用途和特征是什么

Verilog可綜合的循環語句

Verilog教程之Verilog HDL程序設計語句和描述方式

Verilog邏輯設計中的循環語句和運算符

Verilog中循環語句簡介

Verilog中的If語句和case語句介紹

Verilog常用的循環語句及用途

Verilog常用的循環語句及用途

評論