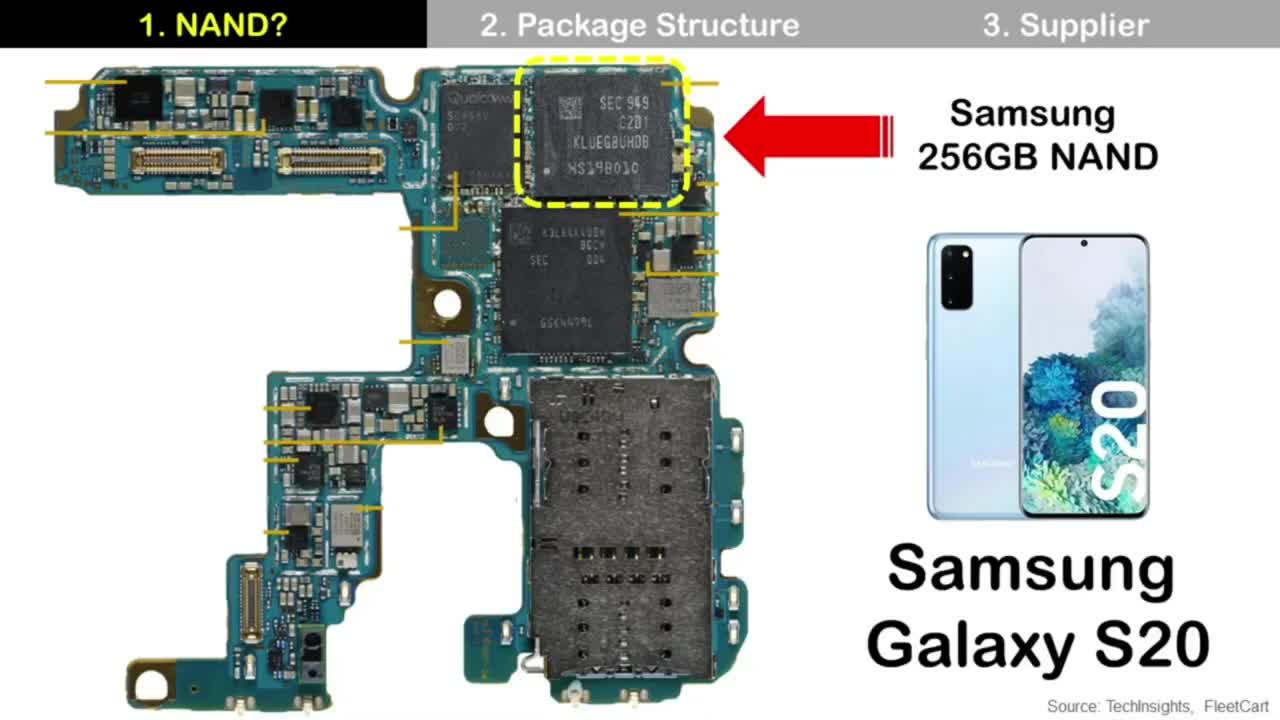

芯片與封裝之間,封裝內(nèi)各芯片之間,以區(qū)封裝與印制電路板(PCB)之間存在交互作用,采用芯片-封裝-PCB 協(xié)同設(shè)計(jì)可以優(yōu)化芯片、封裝乃至整個(gè)系統(tǒng)的性能,減少設(shè)計(jì)迭代,縮短設(shè)計(jì)周期,降低設(shè)計(jì)成本。

芯片-封裝-PCB 電氣協(xié)同設(shè)計(jì)

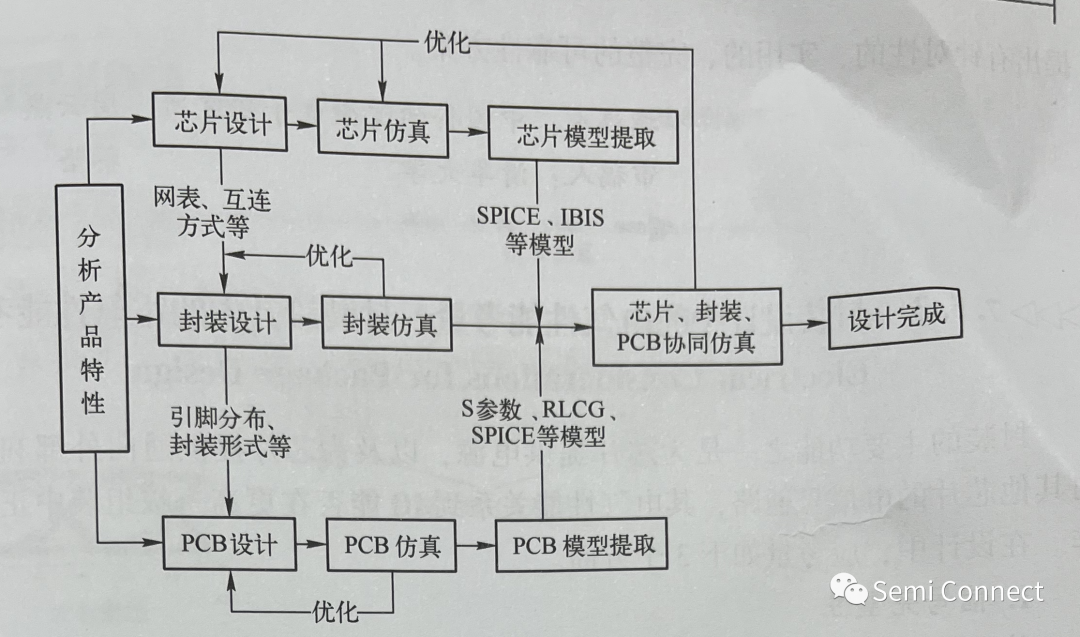

首先分析產(chǎn)品特性 (如產(chǎn)品功能、使用環(huán)境、技術(shù)指標(biāo)等),據(jù)此進(jìn)行芯片設(shè)計(jì),對(duì)其I/O引腳排布進(jìn)行優(yōu)化,結(jié)合芯片的功能、性能和成本,選用合適的互連方式(如引1線鍵合、倒裝芯片等),降低基板布線復(fù)雜度,提高傳輸特性;利用芯片的網(wǎng)表、引腳引出方式等信息進(jìn)行封裝設(shè)計(jì),結(jié)合芯片和產(chǎn)品特性,選用相應(yīng)的封裝形式(如 BGA、LCA、QFN 等),保障將芯片的信息信號(hào)和功率合理地輸人與輸出,實(shí)現(xiàn)芯片之間的互連;對(duì)芯片實(shí)現(xiàn)良好的物理保護(hù)綜合考慮 PCB 的布線難度和功能,實(shí)現(xiàn)整個(gè)系統(tǒng)的設(shè)計(jì)。然后分別進(jìn)行芯片、封裝和 PCB 的仿真,提取芯片模型和 PCB 模型,并將其導(dǎo)人到封裝的仿真模型中,進(jìn)行信號(hào)完整傳輸路徑的仿真,建立系統(tǒng)級(jí)仿真鏈路,實(shí)現(xiàn)芯片一封裝PCB 的協(xié)同設(shè)計(jì)和仿真,然后基于仿真結(jié)果,分析芯片、封裝和 PCB 的設(shè)計(jì)對(duì)整個(gè)系統(tǒng)的影響,并對(duì)其進(jìn)行優(yōu)化,最終完成設(shè)計(jì)。芯片-封裝-PCB 的電學(xué)協(xié)同設(shè)計(jì)流程如圖所示。在協(xié)同設(shè)計(jì)仿真過程中,應(yīng)結(jié)合芯片、封裝和PCB 各自的特點(diǎn),進(jìn)行電源完整性設(shè)計(jì),為芯片提供干凈、穩(wěn)定的電源,為信號(hào)提供低阻抗、低噪聲的參考回路,并抑制電磁干擾。基于芯片的 SPICE(Simulation Program with Integrated Circuit Emphasis) 或 IBIS (Input/ Output BufferIntormation Specification) 等模型、封裝的參數(shù)模型(如 RLCG、S 參數(shù)或 SPICE模型等),以及PCB 的 RLCG 或S參數(shù)等模型,進(jìn)行整個(gè)系統(tǒng)的電性能設(shè)計(jì)與仿真。通過軟件建模工具 與硬件測(cè)試儀器,結(jié)合高速接口電路的電氣特性,完成芯片與封裝軟硬件協(xié)同建模 與參數(shù)提取,依據(jù)仿真得到的滿足系統(tǒng)指標(biāo)的設(shè)計(jì)參數(shù)和文件,得到安全、優(yōu)化的完整設(shè)計(jì)方案。

2.芯片-封裝-PCB 散熱協(xié)同設(shè)計(jì)

芯片熱功耗的大小對(duì)封裝結(jié)構(gòu)、材料選取、散熱設(shè)計(jì) 等提出了不同的需求,應(yīng)根據(jù)不同的產(chǎn)品特性選取合適的散熱方式(如風(fēng)冷、水冷和自然對(duì)流)、封裝結(jié)構(gòu)(如內(nèi)部熱沉、加散熱過孔、基板結(jié)構(gòu)等)和封裝材料(如貼片膠、塑封料和基板材料等),將芯片產(chǎn)生的熱量有效地傳導(dǎo)給PCB 或散熱器。散熱協(xié)同設(shè)計(jì)的主要目的是,針對(duì)產(chǎn)品性能及可靠性需求,實(shí)現(xiàn)芯片、封裝和 PCB 的合理布局,控制局部熱點(diǎn),提高整體散熱性能。將模擬仿真結(jié)果與可測(cè)性實(shí)驗(yàn)相結(jié)合,對(duì)單個(gè)芯片或多芯片集成的封裝體逐級(jí)開展溫度分布分析,研究芯片、熱界面材料與整個(gè)散熱結(jié)構(gòu)之間的關(guān)系,并對(duì)設(shè)計(jì)方案進(jìn)行調(diào)整和優(yōu)化,提高系統(tǒng)的整體散熱性能。協(xié)同設(shè)計(jì)通過采用不同的材料、結(jié)構(gòu)和散熱方式,優(yōu)化系統(tǒng)的散熱方案和連接機(jī)制,如利用銅基及散熱通孔、新型熱界面材料、輔助散熱裝置等技術(shù)來提高系統(tǒng)的散熱性。

3.芯片-封裝-PCB 熱機(jī)械可靠性協(xié)同設(shè)計(jì)

芯片-封裝-PCB 的熱機(jī)械可靠性協(xié)同設(shè)計(jì)主要對(duì)芯片、封裝及系統(tǒng)之間的力學(xué)相互作用進(jìn)行分析,并對(duì)芯片、封裝及PCB 的結(jié)構(gòu)設(shè)計(jì)和材料選取進(jìn)行設(shè)計(jì)和優(yōu)化。熱機(jī)械可靠性分析通過仿真不同封裝結(jié)構(gòu)和材料的應(yīng)力梯度分布得到合適的結(jié)構(gòu)和材料,使其滿足芯片的參數(shù)性能,將應(yīng)力分布控制在芯片的線性、增益、電壓偏移及其他特性隨應(yīng) 力變化的范圍內(nèi);也可分析芯片、封裝和 PCB 間因材料的不同導(dǎo)致的 CTE 不匹配,以及工藝過程累計(jì)的殘余應(yīng)力隨溫度變化引起的熱應(yīng)力應(yīng)變和翹曲問題,通過采用熱機(jī)械模擬方法逐層進(jìn)行分析,提出有針對(duì)性的、實(shí)用的、完整的可靠性方案。

審核編輯:湯梓紅

-

芯片

+關(guān)注

關(guān)注

459文章

52174瀏覽量

436134 -

pcb

+關(guān)注

關(guān)注

4352文章

23417瀏覽量

406737 -

印制電路板

+關(guān)注

關(guān)注

14文章

963瀏覽量

41529 -

封裝

+關(guān)注

關(guān)注

128文章

8497瀏覽量

144784 -

BGA

+關(guān)注

關(guān)注

5文章

565瀏覽量

48139

原文標(biāo)題:芯片-封裝-PCB 協(xié)同設(shè)計(jì),晶片-封裝-PCB 協(xié)同設(shè)計(jì)

文章出處:【微信號(hào):Semi Connect,微信公眾號(hào):Semi Connect】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

芯片-封裝協(xié)同設(shè)計(jì)方法優(yōu)化SoC設(shè)計(jì)

RedEDA V2.0為弘快科技商業(yè)化的第二個(gè)大版本,原理圖-PCB-芯片封裝全流程設(shè)計(jì)#芯片 #pcb

芯片封裝引腳名稱自適應(yīng)顯示#芯片封裝#EDA #電子#電子工程師 #先進(jìn)封裝 #pcb設(shè)計(jì)

芯片、封裝和PCB協(xié)同設(shè)計(jì)方法

芯片、封裝和PCB協(xié)同設(shè)計(jì)方法

評(píng)論