Q1

請教一下各位大俠,一般芯片增加CP測試之后,可靠性需要重新評估么?評估哪些內容?

一般是這樣子,大公司CP都要評估的,如果是新process,那CP部門要做DOE,防止die crack等,但是如果是已經released的,連DOE也不用做。可靠性就更不必談了,除非是發生了問題,并且確認是CP引起的,可能需要討論做一些可靠性與FA。

Q2

誰有jesd22-a104e這個版本的標準,可以分享下嗎?

Q3

有人知道IMC層怎么觀察嗎?行業內有規范嗎?季豐對IMC有沒有相關的DPA標準?

WB站會用顯微鏡和軟件染色來看面積,可靠性后我們會做下Cross-section看IMC生長

Q4

各位大佬,有沒有掃分層的SAT資料分享一下呀?

超聲波掃描顯微鏡Sonoscan D9650,

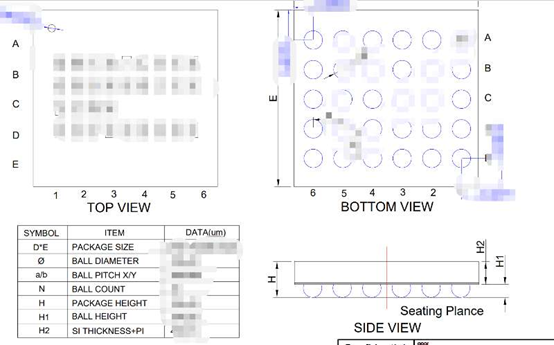

老煉前后的對比照片,老煉后焊球的壓痕還算正常嗎?

如果目的是篩選的就會出貨一般都是100%,目的是壽命的不出貨一般是samples。

Q6

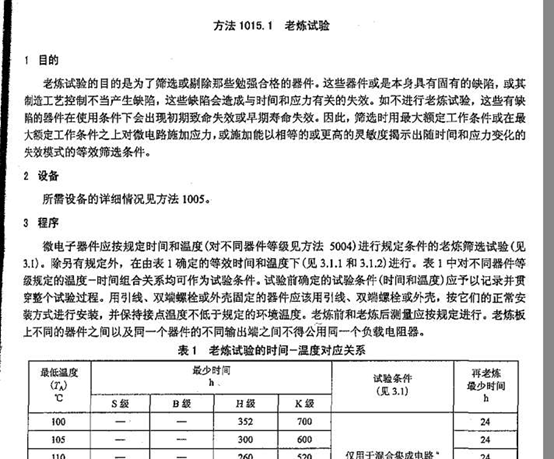

什么是老煉?

國軍標叫老煉,就是壽命實驗的意思,就是加應力加速失效的過程。比如THB,ELFR,HTSL,TC,HTOL,……

Q7

請問大家,WLCSP的 solder ball 下有passivation crack的問題,調整什么參數會有明顯改善,例如可以通過更高次數的TC, solder ball 本身沒有問題,這個是WLCSP封裝,有RDL的。

加underfill一般會有幫助,但也不是所以情況都可以加。UF分CUF和MUF,CUF在很多位置沒有solder ball的情況下,即有大面積空位的情況下UF材料毛細效應弱,流不過去,會有空洞,這樣加UF適得其反;MUF要看這顆IC周圍是不是適合做molding,周圍的器件要不要一起mold起來,有些時候限制太多MUF就不可能了,即使可以做MUF,你也要開模具,增加一道工序,甚至要做熱仿真。passivation crack 的話最好有crack位置的照片和量測數據,還有repassivation的材料和厚度,它下面RDL trace處的臺階高度,RDL trace寬度和間距等,這些信息可以幫助判斷原因和提改進方法。其實這些都有design rule,逐一排查一下吧

Q8

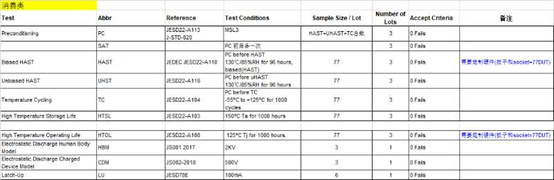

咨詢一下,對于消費類電子,一般會做哪些可靠性項目?

IC類:

pkg-qual:precon, HTSL, TC, uHAST, bHAST,

product-qual:ESD(IBM.CDM), LU, HTOL

可以多做,不少做

Q9

pkg qual與product qual的區別是?

Pkg qual是面向封裝,Product Qual是面向產品(芯片本身的設計和工藝)

Q10

那product qual就不需要做precon, HTSL, TC, uHAST, bHAST實驗了么?

如果只改了芯片設計,別的都沒動,可以不做。

Q11

再咨詢一下,這些rule適用于所有消費類IC產品嘛?比如IC+MOS,這樣的ACDC產品,是否也適用于該可靠性rule?

一般性適用,實際分具體情況。比如,如果是NVM往往要看data retention之類。

Q12

1000hrs,1000cycles,這些時間或者周期可以縮短嘛?

可以啊,等效時間不同。大致意思是,可靠性實驗是以加壓的方式模擬自然(典型)時間條件,加速時間和典型時間會有個換算關系,比如你看到的1000hrs等效為10年,而你的產品不必保那么久,自然可以少做點。

Q13

各位大神,請教下,中測trim過的,到成品測試恢復到熔絲前了,這一般有哪些情況?trim過有燒斷痕跡的,開蓋后探針測試沒有阻值,沒有熔斷。

建議先看看成品熔絲恢復的情況再做推斷,通常現象是成品熔絲有細微裂縫,但是連通電路,這就可能是wt熔斷的冗余度不夠,在封裝時受到擠壓連上了,再去看wafer的熔斷情況,僅供參考。

Q14

請教諸位個問題啊,汽車電子AECQ100中的常溫、高溫、低溫FT測試,業界一般都怎么做呀?如果用熱流罩的話,測試效率太低了,有沒有啥別的好的辦法呢?

三溫handler,可以編程設計。

Q15

請教各位大佬, 固態硬盤BGA顆粒和PCB焊接有很多氣泡,影響和主要改善方向有哪些?(懷疑是baseline問題)

我們出現過類似的問題,問題原因是:Flux沒按固定存放。

Q16

咨詢一個問題,工業上的IC,一般MSL是要求幾的?

伺服驅動器上用的IC是MSL2或MSL1,分立器件用的都是MSL1。

Q17

請問一下,在做HBM時,芯片的測試條件是所有管腳都需要上1.1倍的設計工作電壓呢,還是按照設計時使用的ESD管子的最大電壓來做?

HBM芯片不用上電的,latch up電源管腳才說上電的,IO管腳是電流。

原文標題:季豐電子IC運營工程技術知乎 – 21W50

文章出處:【微信公眾號:上海季豐電子】歡迎添加關注!文章轉載請注明出處。

-

芯片

+關注

關注

459文章

52174瀏覽量

436134 -

軟件

+關注

關注

69文章

5119瀏覽量

88936 -

顯微鏡

+關注

關注

0文章

612瀏覽量

24008

原文標題:季豐電子IC運營工程技術知乎 – 21W50

文章出處:【微信號:zzz9970814,微信公眾號:上海季豐電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

芯片封裝需要進行哪些仿真?

芯片增加CP測試之后需要重新評估么

芯片增加CP測試之后需要重新評估么

評論