引 子

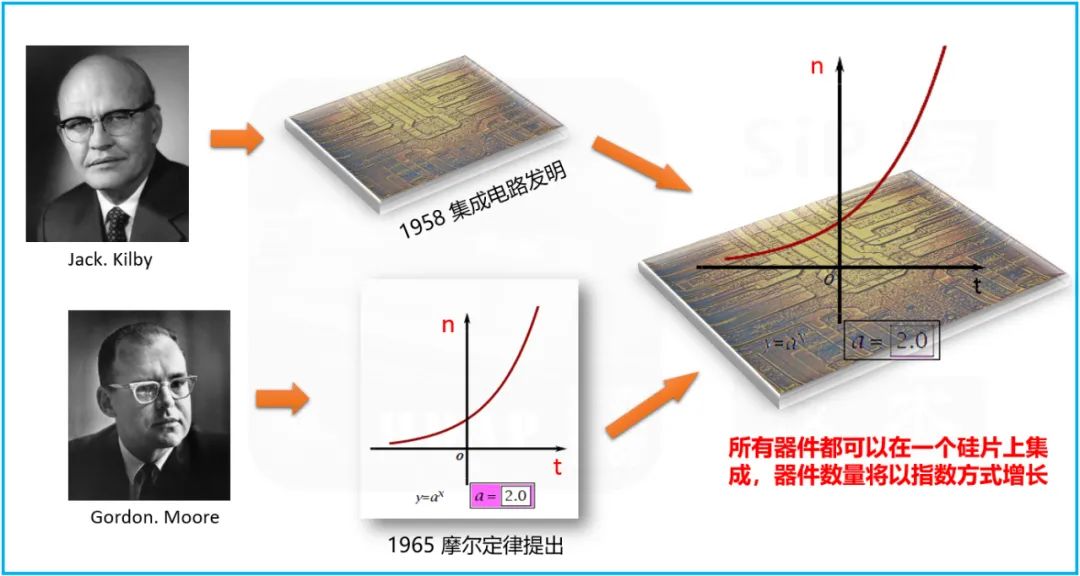

1958年9月12日,溫和的巨人杰克?基爾比(Jack Kilby)發(fā)明了集成電路,當(dāng)時(shí)沒有人知道,這項(xiàng)發(fā)明會(huì)給人類世界帶來如此大的改變。

42年后,基爾比因?yàn)榘l(fā)明集成電路獲得了2000年諾貝爾物理學(xué)獎(jiǎng),“為現(xiàn)代信息技術(shù)奠定了基礎(chǔ)”是諾獎(jiǎng)給予基爾比的中肯評(píng)價(jià)。

科學(xué)技術(shù)的進(jìn)步往往是由一連串夢想而推動(dòng)的,集成電路自然也不例外。

基爾比這位身高兩米,性格溫和穩(wěn)重的TI工程師的夢想就是:“用硅一種材料來制作電路所需的所有器件”。

集成電路發(fā)明7年后,Intel創(chuàng)始人戈登?摩爾提出了他的預(yù)言式夢想:“集成電路上的器件數(shù)量每隔十八個(gè)月將翻一番”,這就是我們今天所熟知的摩爾定律。

最終,他們都實(shí)現(xiàn)了自己的夢想,推動(dòng)了科技的巨大進(jìn)步。兩個(gè)偉大的夢想疊加在一起,也造就了今天的半導(dǎo)體產(chǎn)業(yè)。

“所有的器件都可以在一個(gè)硅片上集成,器件數(shù)量將以指數(shù)方式增長”,這就是我們對(duì)兩個(gè)偉大的夢想的總結(jié)。六十多年后的今天,整個(gè)集成電路產(chǎn)業(yè)的發(fā)展依然以它們?yōu)榛?/p>

從同構(gòu)到異構(gòu)

事物的發(fā)展有其出現(xiàn)、發(fā)展、成熟、終結(jié)的過程,技術(shù)的發(fā)展也是如此。

基爾比曾經(jīng)認(rèn)為,在一種材料上做出所有電路需要的器件才是電路微型化的出路,只需要一種半導(dǎo)體材料就能將所有電子器件集成起來,今天,我們稱之為同構(gòu)集成 Homogeneous integration。在這篇文章里,我們重點(diǎn)討論的則是另一個(gè)技術(shù):異構(gòu)集成 Heterogeneous integration。

首先,我們了解一下從同構(gòu)到異構(gòu)的發(fā)展過程。

從基爾比開始,人類就致力于在硅片上制作出電路所需要的所有器件,在摩爾定律的推動(dòng)下,硅片上的器件數(shù)量以指數(shù)方式增長。今天,在一平方毫米的硅片上可集成的器件數(shù)量輕松超過一億只,主流芯片都集成了百億量級(jí)的晶體管。

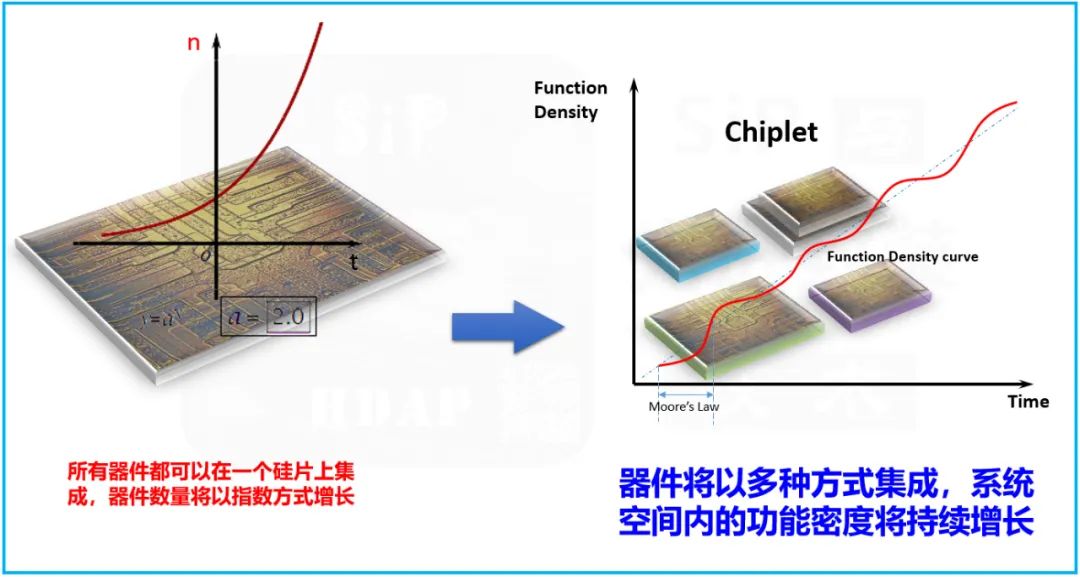

同構(gòu)集成技術(shù)的發(fā)展已經(jīng)如此成熟,同樣不可避免地會(huì)經(jīng)歷走向終結(jié)的過程,在同構(gòu)集成逐漸成熟并難以再持續(xù)發(fā)展的過程中,人類必須尋找一種新的集成方式來延續(xù),這就是異構(gòu)集成。

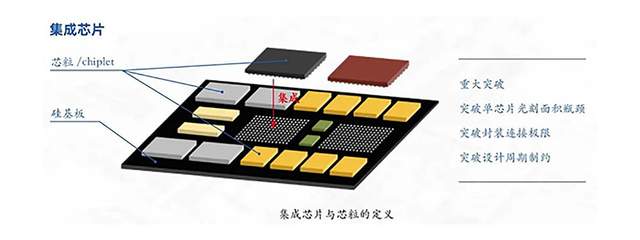

異構(gòu)集成中有一個(gè)重點(diǎn)概念我們需要理解,這就是Chiplet,Chiplet意為小芯片,就是將現(xiàn)有的大芯片切割成小芯片,然后再進(jìn)行集成。為什么要將大芯片切割成Chiplet,這就是我們下面要講述的Chiplet技術(shù)帶來的新“四化”。

除了大芯片切割為Chiplet,芯片上的器件數(shù)量也不再以指數(shù)方式增長,也就是摩爾定律終將走向終結(jié)。筆者認(rèn)為:“器件將以多種方式集成,系統(tǒng)空間內(nèi)的功能密度將持續(xù)增長”。關(guān)于摩爾定律的終結(jié)、系統(tǒng)空間、功能密度等詳細(xì)內(nèi)容請(qǐng)參看即將出版的新書《基于SiP技術(shù)的微系統(tǒng)》。

Chiplet技術(shù)的出現(xiàn)帶來了芯片設(shè)計(jì)的新變化,我們簡單描述為:IP芯片化、集成異構(gòu)化、集成異質(zhì)化、IO增量化,簡稱為新“四化”。

Chiplet技術(shù)

Chiplet顧名思義就是小芯片,我們可以把它想象成樂高積木的高科技版本。首先將復(fù)雜功能進(jìn)行分解,然后開發(fā)出多種具有單一特定功能,可進(jìn)行模塊化組裝的“小芯片”(Chiplet),如實(shí)現(xiàn)數(shù)據(jù)存儲(chǔ)、計(jì)算、信號(hào)處理、數(shù)據(jù)流管理等功能,并以此為基礎(chǔ),建立一個(gè)“小芯片”的集成系統(tǒng)。

簡單來說,Chiplet技術(shù)就是像搭積木一樣,把一些預(yù)先生產(chǎn)好的實(shí)現(xiàn)特定功能的芯片裸片(die)通過先進(jìn)的集成技術(shù)封裝在一起形成一個(gè)系統(tǒng)級(jí)芯片,而這些基本的裸片就是Chiplet。

Chiplet芯片可以使用更可靠和更便宜的技術(shù)制造。較小的硅片本身也不太容易產(chǎn)生制造缺陷。此外,Chiplet芯片也不需要采用同樣的工藝,不同工藝生產(chǎn)制造的Chiplet可以通過SiP技術(shù)有機(jī)地結(jié)合在一起。

1. IP芯片化

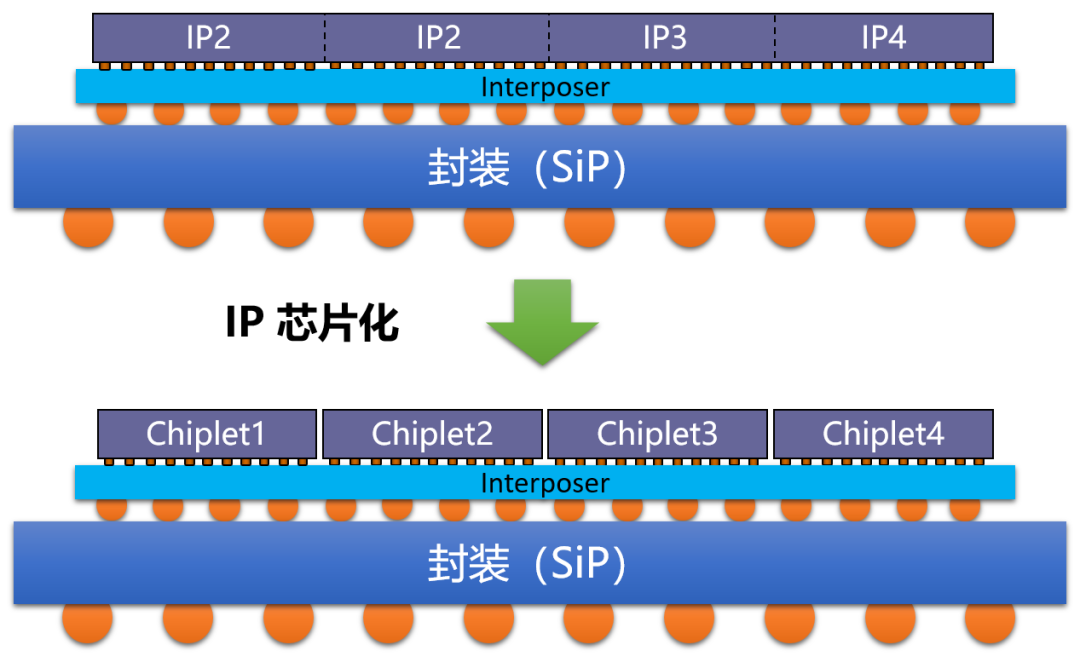

IP(Intelligent Property)是具有知識(shí)產(chǎn)權(quán)核的集成電路的總稱,是經(jīng)過反復(fù)驗(yàn)證過的、具有特定功能的宏模塊,可以移植到不同的半導(dǎo)體工藝中。到了SoC階段,IP核設(shè)計(jì)已成為ASIC電路設(shè)計(jì)公司和FPGA提供商的重要任務(wù),也是其實(shí)力的體現(xiàn)。對(duì)于芯片開發(fā)軟件,其提供的IP核越豐富,用戶的設(shè)計(jì)就越方便,其市場占用率就越高。目前,IP核已經(jīng)變成SoC系統(tǒng)設(shè)計(jì)的基本單元,并作為獨(dú)立設(shè)計(jì)成果被交換、轉(zhuǎn)讓和銷售。

IP核對(duì)應(yīng)描述功能行為的不同分為三類,即軟核(Soft IP Core)、固核(Firm IP Core)和硬核(Hard IP Core)。

當(dāng)IP硬核是以硅片的形式提供時(shí),就變成了Chiplet。

我們可以這么理解:SiP中的Chiplet就對(duì)應(yīng)于SoC中的IP硬核。Chiplet 就是一個(gè)新的 IP 重用模式,就是硅片級(jí)別的IP重用。

設(shè)計(jì)一個(gè)SoC系統(tǒng)級(jí)芯片,以前的方法是從不同的 IP 供應(yīng)商購買一些 IP,軟核、固核或硬核,結(jié)合自研的模塊,集成為一個(gè) SoC,然后在某個(gè)芯片工藝節(jié)點(diǎn)上完成芯片設(shè)計(jì)和生產(chǎn)的完整流程。

有了Chiplet以后,對(duì)于某些 IP,就不需要自己做設(shè)計(jì)和生產(chǎn)了,而只需要買別人實(shí)現(xiàn)好的硅片,然后在一個(gè)封裝里集成起來,形成一個(gè) SiP。所以 Chiplet 可以看成是一種硬核形式的 IP,但它是以芯片的形式提供的。因此,我們稱之為IP芯片化。

2. 集成異構(gòu)化

HeteroStructure Integration

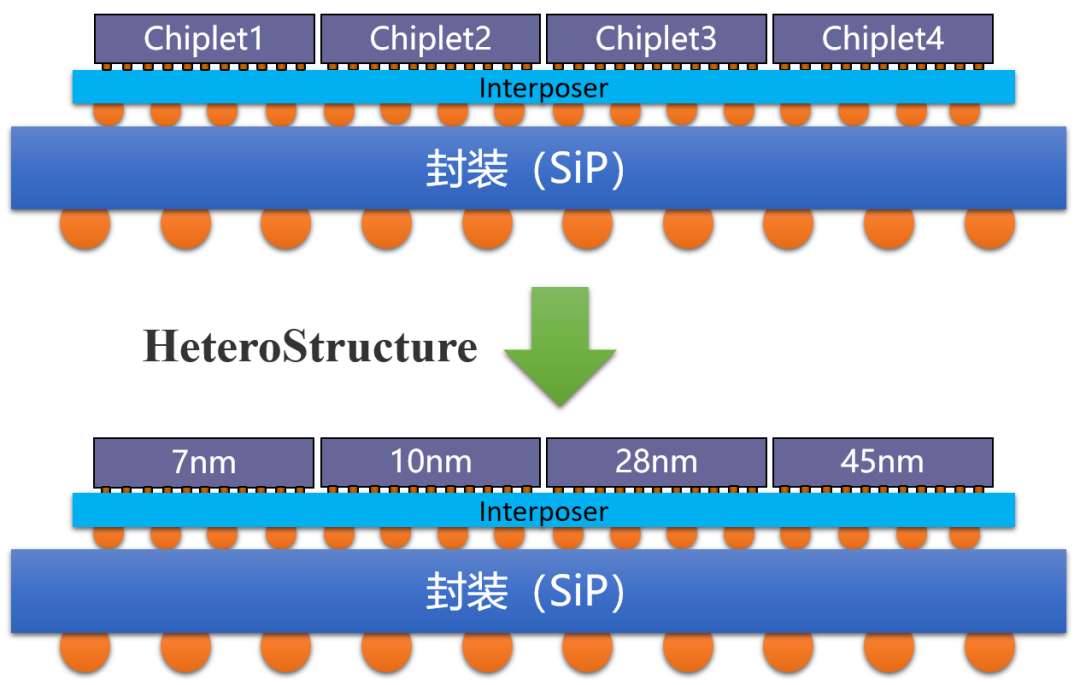

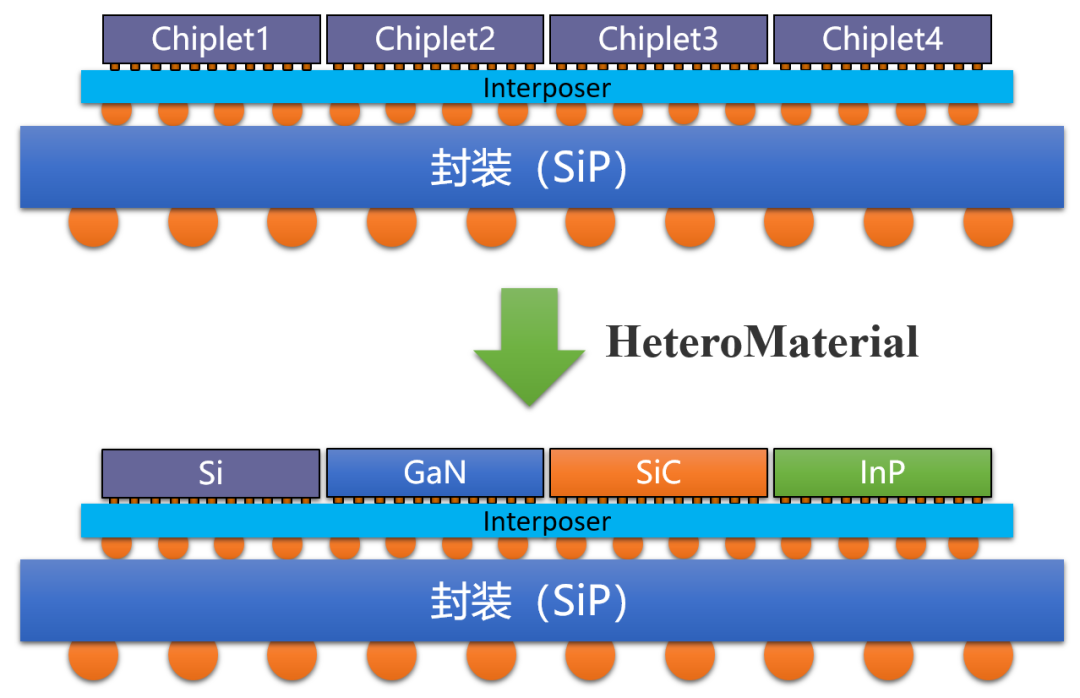

在半導(dǎo)體集成中,Heterogeneous 是異構(gòu)異質(zhì)的含義,在這里我們將其分為異構(gòu)HeteroStructure和異質(zhì)HeteroMaterial兩個(gè)層次的含義。

在這篇文章中,異構(gòu)集成HeteroStructure Integration主要指將多個(gè)不同工藝單獨(dú)制造的芯片封裝到一個(gè)封裝內(nèi)部,以增強(qiáng)功能性和提高工作性能,可以對(duì)采用不同工藝、不同功能、不同制造商制造的組件進(jìn)行封裝。

例如上圖所示:將7nm、10nm、28nm、45nm的Chiplet通過異構(gòu)集成技術(shù)封裝在一起。

通過異構(gòu)集成技術(shù),工程師可以像搭積木一樣,在芯片庫里將不同工藝的Chiplet小芯片組裝在一起。

3. 集成異質(zhì)化

HeteroMaterial Integration

近年來集成硅(CMOS和BiCMOS)射頻技術(shù)已經(jīng)在功率上取得巨大的進(jìn)步,同時(shí)也將頻率擴(kuò)展到了100GHz左右。然而還有眾多應(yīng)用只能使用像磷化銦(InP)和氮化鎵(GaN)這樣的化合物半導(dǎo)體技術(shù)才能實(shí)現(xiàn)。磷化銦能提供最大頻率為1太赫茲的晶體管,具備高增益和高功率,以及超高速混合信號(hào)電路。而氮化鎵能使器件具備大帶寬、高擊穿電壓、以及高達(dá)100GHZ的輸出功率。

因此將不同材料的半導(dǎo)體集成為一體——即異質(zhì)集成HeteroMaterial Integration,可產(chǎn)生尺寸小、經(jīng)濟(jì)性好、設(shè)計(jì)靈活性高、系統(tǒng)性能更佳的產(chǎn)品。

如下圖所示,將Si、GaN、SiC、InP生產(chǎn)加工的Chiplet通過異質(zhì)集成技術(shù)封裝到一起,形成不同材料的半導(dǎo)體在同一款封裝內(nèi)協(xié)同工作的場景。

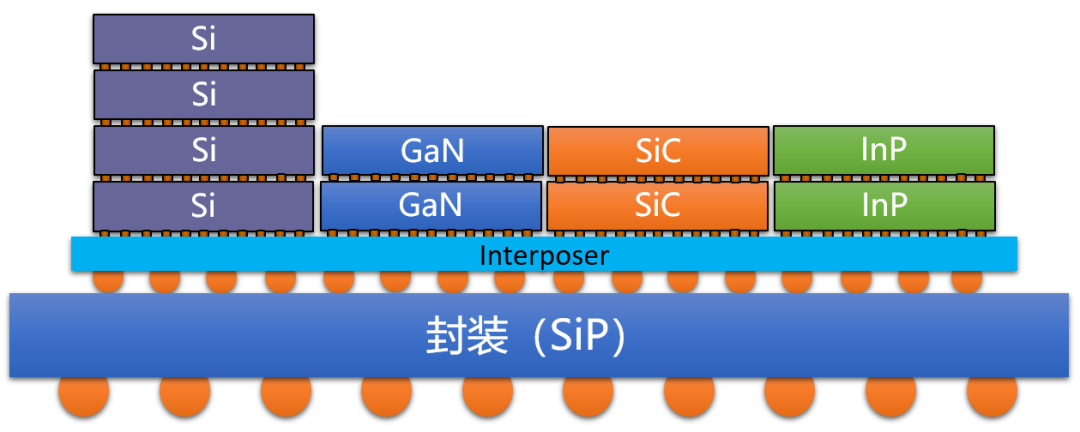

在單個(gè)襯底上橫向集成不同材料的半導(dǎo)體器件(硅和化合物半導(dǎo)體)以及無源元件(包括濾波器和天線)等是Chiplet應(yīng)用中比較常見的集成方式。

需要讀者注意的是,目前不同材料的多芯片集成主要采用橫向平鋪的方式在基板上集成,對(duì)于縱向堆疊集成,則傾向于堆疊中的芯片采用同種材質(zhì),從而避免了由于熱膨脹系統(tǒng)等參數(shù)的不一致而導(dǎo)致的產(chǎn)品可靠性降低,如下圖所示。

4. IO增量化

如果說前面的“三化”是Chiplet技術(shù)的優(yōu)勢,那么,IO增量化則給Chiplet帶來了挑戰(zhàn)。IO增量化體現(xiàn)在水平互聯(lián)(RDL)的的增量化,同時(shí)也體現(xiàn)在垂直互聯(lián)(TSV)的增量化。

在傳統(tǒng)的封裝設(shè)計(jì)中,IO數(shù)量一般控制在幾百或者數(shù)千個(gè),Bondwire工藝一般支持的IO數(shù)量最多數(shù)百個(gè),當(dāng)IO數(shù)量超過一千個(gè)時(shí),多采用FlipChip工藝。在Chiplet設(shè)計(jì)中,IO數(shù)量有可能多達(dá)幾十萬個(gè),為什么會(huì)有這么大的IO增量呢?

我們知道,一塊PCB的對(duì)外接口通常不超過幾十個(gè),一款封裝對(duì)外的接口為幾百個(gè)到數(shù)千個(gè),而在芯片內(nèi)部,晶體管之間的互聯(lián)數(shù)量則可能多達(dá)數(shù)十億到數(shù)百億個(gè)。越往芯片內(nèi)層深入,其互聯(lián)的數(shù)量會(huì)急劇增大。Chiplet是大芯片被切割成的小芯片,其間的互聯(lián)自然不會(huì)少,經(jīng)常一款Chiplet封裝的硅轉(zhuǎn)接板超過100K+的TSV,250K+的互聯(lián),這在傳統(tǒng)封裝設(shè)計(jì)中是難以想象的。

由于IO的增量化,Chiplet的設(shè)計(jì)也對(duì)EDA軟件提出了新的挑戰(zhàn),Chiplet技術(shù)需要EDA工具從架構(gòu)探索、芯片設(shè)計(jì)、物理及封裝實(shí)現(xiàn)等提供全面支持,以在各個(gè)流程提供智能、優(yōu)化的輔助,避免人為引入問題和錯(cuò)誤。

Cadence、Synopsys、Siemens EDA(Mentor)等傳統(tǒng)的集成電路EDA公司都相繼推出支撐Chiplet集成的設(shè)計(jì)仿真驗(yàn)證工具。

總 結(jié)

從基爾比開始,同構(gòu)集成技術(shù)經(jīng)過六十多年的發(fā)展,已經(jīng)相當(dāng)成熟,并逐漸走向極致,同時(shí),摩爾定律以指數(shù)增長的趨勢也難以為繼,人類必須尋找一種新的集成方式來進(jìn)行延續(xù),這就是異構(gòu)集成。

異構(gòu)集成以更靈活的方式讓功能單位在系統(tǒng)空間進(jìn)行集成,并讓系統(tǒng)空間的功能密度持續(xù)增長,只是這種增長不再以指數(shù)方式增長。

異構(gòu)集成的單元可稱之為Chiplet,Chiplet技術(shù)給集成電路產(chǎn)業(yè)帶來了新的變化,該技術(shù)既有新的優(yōu)勢也帶來了新的挑戰(zhàn)。

總結(jié)一下,Chiplet帶給集成技術(shù)的新變化就是:IP芯片化、集成異構(gòu)化、集成異質(zhì)化、IO增量化,我們稱之為Chiplet技術(shù)帶來的新“四化”。

編輯:jq

-

芯片

+關(guān)注

關(guān)注

459文章

52160瀏覽量

436070 -

集成電路

+關(guān)注

關(guān)注

5419文章

11945瀏覽量

367099 -

芯片設(shè)計(jì)

+關(guān)注

關(guān)注

15文章

1064瀏覽量

55461 -

IP

+關(guān)注

關(guān)注

5文章

1783瀏覽量

151291 -

EDA技術(shù)

+關(guān)注

關(guān)注

12文章

173瀏覽量

37390

原文標(biāo)題:干貨 | Chiplet帶來的新變化

文章出處:【微信號(hào):wc_ysj,微信公眾號(hào):旺材芯片】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

Chiplet與先進(jìn)封裝設(shè)計(jì)中EDA工具面臨的挑戰(zhàn)

淺談Chiplet與先進(jìn)封裝

Chiplet技術(shù)在消費(fèi)電子領(lǐng)域的應(yīng)用前景

奇異摩爾受邀出席第三屆HiPi Chiplet論壇

LibreELEC 12.0.2 為樹莓派用戶帶來重大變化!

Chiplet:芯片良率與可靠性的新保障!

2.5D集成電路的Chiplet布局設(shè)計(jì)

樹形喇叭狀異形創(chuàng)意LED顯示屏為商業(yè)顯示、展覽展示、文旅旅游等行業(yè)帶來了全新的變化

解鎖Chiplet潛力:封裝技術(shù)是關(guān)鍵

GPT誕生兩周年,AIPC為連接器帶來什么新變化?

Chiplet技術(shù)有哪些優(yōu)勢

IMEC組建汽車Chiplet聯(lián)盟

淺談Chiplet帶來了哪些新的變化

淺談Chiplet帶來了哪些新的變化

評(píng)論