Chiplet與先進封裝的結合

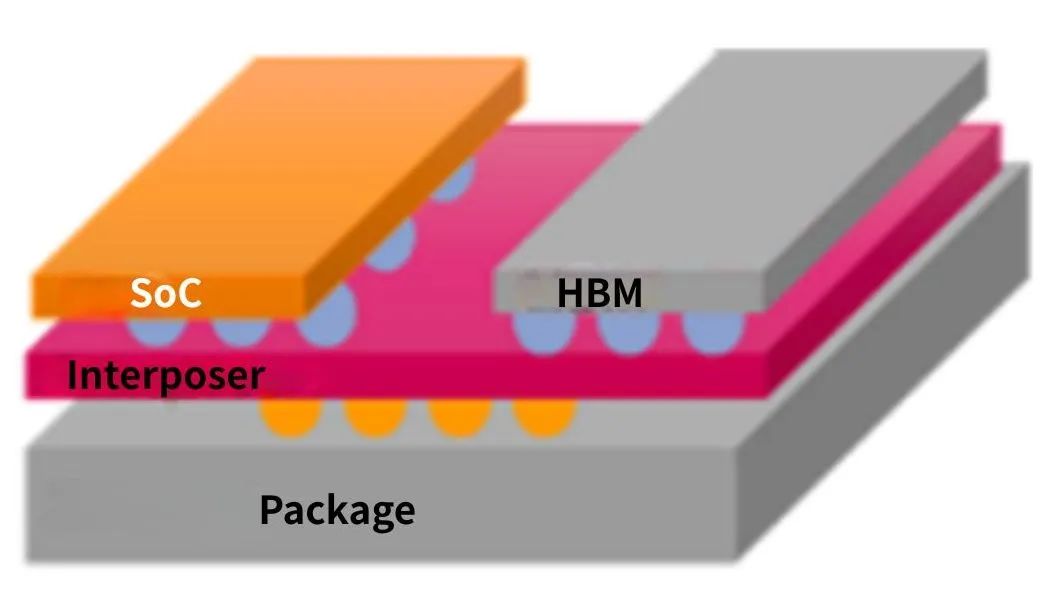

Chiplet和先進封裝通常是互為補充的。Chiplet技術使得復雜芯片可以通過多個相對較小的模塊來實現,而先進封裝則提供了一種高效的方式來將這些模塊集成到一個封裝中。通過這種組合,設計師可以在不需要完全重新設計每個組件的情況下,輕松地實現芯片的定制化、升級以及性能優化。例如,某些應用可能需要特定的高帶寬內存(HBM)或專用加速器(如AI加速器),這些可以作為獨立的Chiplet與主處理器Chiplet共同組成系統。在封裝級別,設計者使用先進封裝技術,將這些Chiplet通過高密度互聯(如微凸點、硅通孔、封裝內光互聯等)連接起來,從而優化整體性能、帶寬和功耗。

EDA工具面臨的挑戰

隨著Chiplet和先進封裝技術的廣泛應用,EDA工具在設計、驗證、優化這些新型結構時面臨著一系列挑戰。

設計復雜性增加

Chiplet和先進封裝設計的一個顯著特點是其設計復雜性的大幅提升。每個Chiplet內部都有獨立的電路設計和功能,設計者需要考慮如何將這些獨立的模塊組合起來,以實現最佳的性能和功耗。與此同時,封裝層面的設計(包括互連、散熱、信號完整性等)也增加了額外的挑戰。EDA工具需要支持這種多層次的、跨模塊的設計過程,而不僅僅是單一的芯片設計。這就需要EDA工具支持多物理場協同仿真,需同時分析電、熱、力(應力)耦合效應。

互聯和帶寬的優化

Chiplet之間的互連是其設計中至關重要的一環。不同的Chiplet需要高效、低延遲的互聯,以保證整體系統的性能。傳統的EDA工具通常集中在單一芯片內部的布線和互連上,但在Chiplet架構中,EDA工具不僅需要考慮單一芯片的信號完整性,還需要處理模塊之間的互聯設計、帶寬規劃以及信號傳輸的時序問題。為了支持這種需求,EDA工具需要具備跨模塊的信號仿真和帶寬分析能力。從納米級晶體管到厘米級封裝的全鏈路仿真,要求EDA工具支持電磁場求解器與電路仿真的聯合優化。

封裝層級設計與優化

傳統EDA工具通常僅關注芯片級設計,而在Chiplet與先進封裝架構下,設計和優化的范圍擴展到了封裝層級。封裝不僅需要支持Chiplet間的電氣連接,還要考慮到散熱、機械結構、功耗、尺寸限制等多方面的因素。這要求EDA工具在設計初期就能進行封裝級的電氣、熱、機械等多物理場仿真,并提供針對性的優化方案。同時由于當前UCIe(通用Chiplet互連標準)尚未完全普及,EDA工具需支持自定義互連協議驗證。

多種制造工藝和異構集成

在Chiplet設計中,每個模塊可能使用不同的制造工藝(例如,處理器模塊使用先進的FinFET工藝,而存儲模塊可能使用不同的工藝),并且不同的模塊需要通過異構集成來連接。不同工藝節點的Chiplet需統一DRC,EDA工具需要支持這種工藝多樣性,并能夠在不同工藝之間進行有效的互操作性分析和優化。此外,異構集成還要求EDA工具能夠處理不同模塊之間的電氣、熱管理和機械對接問題。

驗證與測試的挑戰

Chiplet架構的引入使得驗證工作變得更加復雜。傳統的SoC設計驗證方法可能不適用于Chiplet系統,因為驗證過程需要涉及到不同模塊之間的交互,以及跨模塊的接口驗證。此外,由于多個廠商可能提供不同的Chiplet,確保這些模塊之間的兼容性和協同工作變得更加困難。EDA工具需要支持跨廠商、多模塊的驗證,并能夠處理復雜的接口標準和協議。

功耗和散熱的管理

在Chiplet和先進封裝的設計中,功耗管理和散熱設計是至關重要的。Chiplet間互連功耗可能占系統總功耗15%以上,需動態電壓頻率調整算法支持,并且每個Chiplet可能具有不同的功耗特性,而它們在集成到封裝中的時候,散熱成為一個不容忽視的問題。EDA工具需要提供有效的功耗估算和熱分析工具,以幫助設計者優化整體系統的能效和熱管理,避免出現過熱導致的性能下降或失效。

總結

Chiplet與先進封裝的結合正重塑半導體產業模式,而EDA工具需突破傳統邊界,向多物理場、高自動化、全鏈路協同的方向演進。為了應對這些挑戰,EDA工具必須不斷進化,提供更強的跨模塊設計、優化、驗證以及仿真能力,同時支持異構集成和多廠商協作。巨霖科技將圍繞Chiplet產業,就先進封裝(2.5D,3D)技術提供一個覆蓋全流程的EDA仿真平臺,該平臺提供完整的包括3DIC設計、SI/PI/多物理場分析的解決方案。

-

處理器

+關注

關注

68文章

19799瀏覽量

233496 -

eda

+關注

關注

71文章

2881瀏覽量

176429 -

chiplet

+關注

關注

6文章

452瀏覽量

12860 -

先進封裝

+關注

關注

2文章

460瀏覽量

501

原文標題:Chiplet與先進封裝的技術協同及EDA仿真工具面臨的挑戰 (二)

文章出處:【微信號:巨霖,微信公眾號:巨霖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

半導體芯片先進封裝——CHIPLET

IC設計中Accellera先進庫格式語言與EDA工具的結合

淺析先進封裝設計面臨的四大挑戰

光芯片走向Chiplet,顛覆先進封裝

Chipletz采用芯和半導體Metis工具設計智能基板產品 解決Chiplet先進封裝設計中的信號和電源完整性分析挑戰

3D IC先進封裝的發展趨勢和對EDA的挑戰

何謂先進封裝/Chiplet?先進封裝/Chiplet的意義

Chiplet技術給EDA帶來了哪些挑戰?

先進封裝Chiplet的優缺點與應用場景

探討Chiplet封裝的優勢和挑戰

先進封裝 Chiplet 技術與 AI 芯片發展

Chiplet在先進封裝中的重要性

Chiplet與先進封裝設計中EDA工具面臨的挑戰

Chiplet與先進封裝設計中EDA工具面臨的挑戰

評論