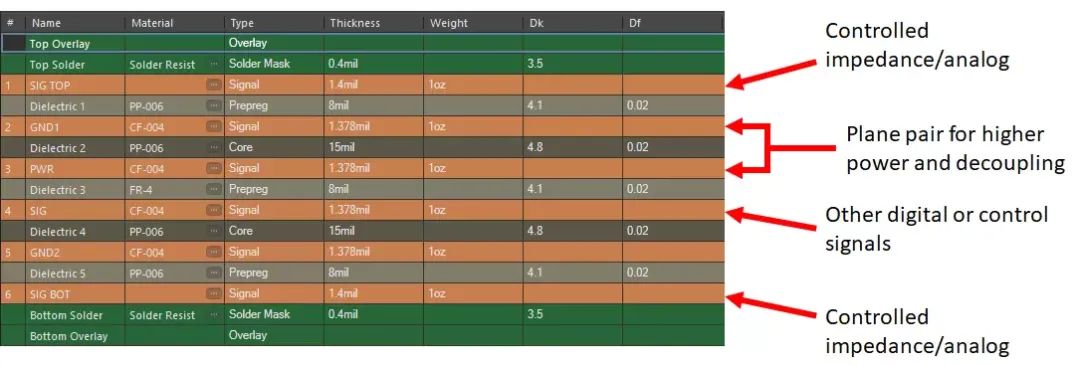

射頻板設(shè)計(jì)PCB疊層時(shí),推薦使用四層板結(jié)構(gòu),層設(shè)置架構(gòu)如下

完整的電源平面提供極低的電源阻抗和分布的去耦電容,同時(shí)射頻信號(hào)線有一個(gè)完整的參考地,為射頻信號(hào)提供完整恒定不變的參考,有利于射頻傳輸線阻抗的連續(xù)性。

地平面設(shè)計(jì)規(guī)則

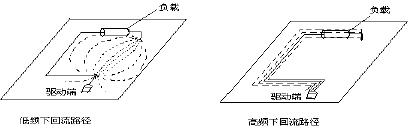

- 作為射頻信號(hào)線鏡像回流地的平面要完整,并且獨(dú)立定義,同時(shí)不要有任何其他信號(hào)線在地平面上布置;

- 對(duì)于Top Layer和Bottom Layer空白部分,建議做鋪地處理,并且通過(guò)間距不大于λ/20的過(guò)孔將各部分地連在一起;

- 對(duì)于高密度電路板(例如含CSP封裝)不建議使用2層電路板,盡可能采用4層板進(jìn)行設(shè)計(jì);

- 盡量不要將地平面做分地處理,除非保證在地平面上電流不會(huì)形成環(huán)流;

- 射頻信號(hào)線下的地平面要盡可能的寬,地平面過(guò)窄會(huì)引起寄生參數(shù)同時(shí)增加衰減;

- 地平面、頂層的地已經(jīng)連接兩層的過(guò)孔,應(yīng)盡量保證射頻信號(hào)線做到完全的“屏蔽”,以增加產(chǎn)品的EMC能力。

- 同時(shí)建議通過(guò)地孔將電源平面包裹起來(lái),避免不必要的電子輻射。

通常電源層相對(duì)于地層需要滿足“20H”原則,“20H原則”是指要確保電源平面邊緣比地平面(0V參考面)邊緣至少縮進(jìn)相當(dāng)于兩個(gè)平面之間間距的20倍,其中H就是指電源平面與地平面之間的距離,在20H時(shí)可以抑制70%的磁通泄漏,有效的提升EMI性能。

編輯:hfy

-

pcb

+關(guān)注

關(guān)注

4352文章

23417瀏覽量

406738 -

射頻

+關(guān)注

關(guān)注

106文章

5728瀏覽量

169732 -

射頻信號(hào)

+關(guān)注

關(guān)注

6文章

225瀏覽量

21276 -

去耦電容

+關(guān)注

關(guān)注

11文章

319瀏覽量

22813

發(fā)布評(píng)論請(qǐng)先 登錄

6層PCB疊層設(shè)計(jì)指南

射頻設(shè)計(jì)難題之PCB疊層

射頻設(shè)計(jì)難題之PCB疊層

評(píng)論