典型的時(shí)序模型由發(fā)起寄存器、組合邏輯和捕獲寄存器3部分組成,如圖1所示形成了三條時(shí)鐘路徑:原時(shí)鐘路徑(Source Clock path)、數(shù)據(jù)時(shí)鐘路徑(Data path)、目的時(shí)鐘路徑(Destination Clock path)。

1、建立時(shí)間(setup)和保持時(shí)間(hold)

如圖1所示,時(shí)鐘上升邊沿(Capture Edge 、Next Launch Edge)會將數(shù)據(jù)保存下來,但是必須要滿足一定的條件:

A,建立時(shí)間Tsu:在時(shí)鐘有效沿之前,數(shù)據(jù)必須保持穩(wěn)定的最小時(shí)間;

B,保持時(shí)間Th:在時(shí)鐘有效沿之后,數(shù)據(jù)必須保持穩(wěn)定的最小時(shí)間;

這就相當(dāng)于一個(gè)窗口時(shí)間,在有效邊沿的窗口時(shí)間內(nèi),數(shù)據(jù)必須保持穩(wěn)定;這里的時(shí)鐘信號時(shí)序和數(shù)據(jù)信號時(shí)序,都是寄存器實(shí)際感受到的時(shí)序。

2、發(fā)起沿和捕獲沿

如圖1所示,發(fā)起沿和捕獲沿通常相差一個(gè)時(shí)鐘周期同時(shí)捕獲沿也是下一個(gè)發(fā)起沿。

發(fā)起沿(LaunchEdge):數(shù)據(jù)被launch的時(shí)鐘邊沿;也就是說,每一個(gè)啟動沿,一般都會產(chǎn)生一個(gè)新的數(shù)據(jù)!

捕獲沿(CaptureEdge):數(shù)據(jù)被latch的時(shí)鐘邊沿;也就是說,每一個(gè)鎖存沿,都會有一個(gè)新的數(shù)據(jù)被保存!

3、時(shí)序模型2

如圖2所示:

Clk--時(shí)鐘源

Rega--發(fā)起寄存器

Regb--捕獲寄存器

Tclka--原時(shí)鐘延時(shí)

Tclkb--目的時(shí)鐘延時(shí)

Tco--發(fā)起沿有效到數(shù)據(jù)出現(xiàn)在發(fā)起寄存器Q端口所需時(shí)間

Tdata--數(shù)據(jù)延時(shí)(組合邏輯和走線延時(shí))

Tsu--捕獲寄存器建立時(shí)間

Th--捕獲寄存器保持時(shí)間

4、數(shù)據(jù)到達(dá)時(shí)間(Data Arrival Time)

數(shù)據(jù)到達(dá)時(shí)間(Data Arrival Time)=Launch Edge +Tclka+Tco+Tdata

已發(fā)起沿為時(shí)間參考點(diǎn),LaunchEdge 通常為0。

5、數(shù)據(jù)建立需求時(shí)間(setup)

數(shù)據(jù)建立需求時(shí)間(DataRequired Time(setup)) = Tclkb-Tsu-Clock Uncertainty

表明數(shù)據(jù)必須提前Tsu穩(wěn)定存在于捕獲寄存器的輸入端口。

6、數(shù)據(jù)保持需求時(shí)間(hold)

數(shù)據(jù)保持需求時(shí)間(DataRequired Time(hold))=Tclkb +Th-Clock Uncertainty

表明數(shù)據(jù)必須在時(shí)鐘捕獲沿(regb/clk)之后穩(wěn)定存在一段時(shí)間Th。

7、建立時(shí)間裕量(Setup Slack)

建立時(shí)間裕量(SetupSlack)= Data Required Time(setup)-Data Arrival Time(setup)

如果SetupSlack為正,則說明數(shù)據(jù)在規(guī)定的時(shí)間內(nèi)達(dá)到了目標(biāo)。反之,則認(rèn)為數(shù)據(jù)并沒有在規(guī)定的時(shí)間達(dá)到目標(biāo),此時(shí)REG2鎖存的數(shù)據(jù)很有可能存在亞穩(wěn)態(tài)。

8、保持時(shí)間裕量(Hold Slack)

保持時(shí)間裕量(holdSlack)=DataRequired Time(hold)-Data Arrival Time(hold)

如果為正,則認(rèn)為數(shù)據(jù)在被鎖存的時(shí)候有足夠多的穩(wěn)定時(shí)間,是有效的。反之則認(rèn)為數(shù)據(jù)有誤或者數(shù)據(jù)可能存在亞穩(wěn)態(tài)。

編輯:hfy

-

寄存器

+關(guān)注

關(guān)注

31文章

5421瀏覽量

123307 -

數(shù)據(jù)信號

+關(guān)注

關(guān)注

0文章

61瀏覽量

12098 -

Vivado

+關(guān)注

關(guān)注

19文章

828瀏覽量

68206

發(fā)布評論請先 登錄

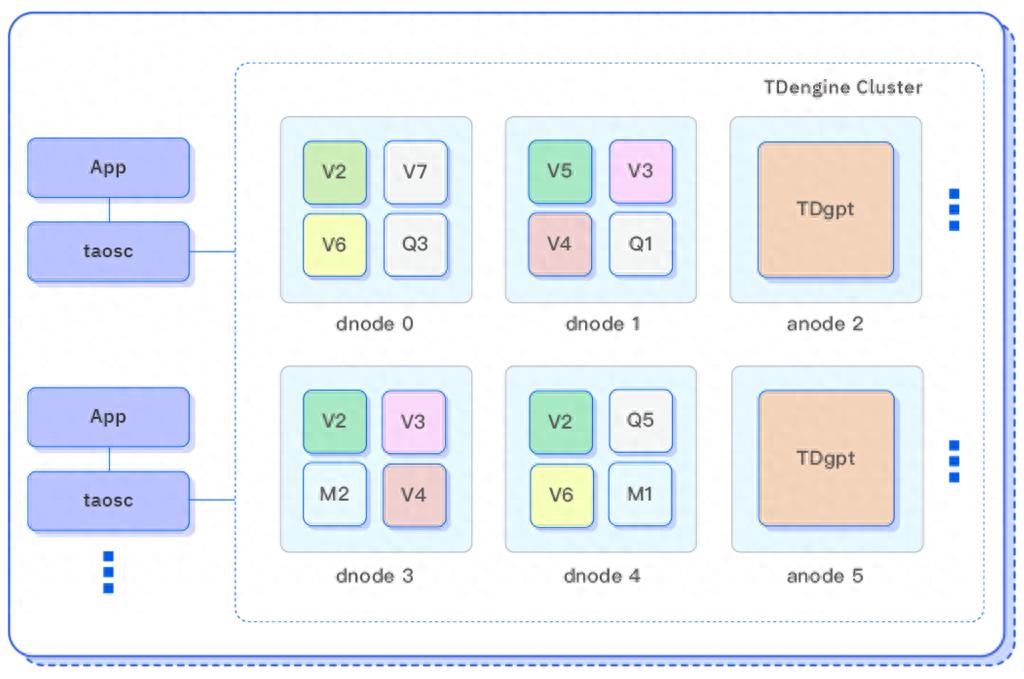

TDengine 發(fā)布時(shí)序數(shù)據(jù)分析 AI 智能體 TDgpt,核心代碼開源

一文詳解Vivado時(shí)序約束

AMD Vivado Design Suite IDE中的設(shè)計(jì)分析簡介

集成電路設(shè)計(jì)中靜態(tài)時(shí)序分析介紹

ads1248使用三條校準(zhǔn)指令校驗(yàn)時(shí),要使用內(nèi)部的VREF,還是使用外部的REF0?

Vivado Design Suite用戶指南: 設(shè)計(jì)分析與收斂技巧

TPS65950實(shí)時(shí)時(shí)鐘時(shí)序補(bǔ)償分析

Vivado使用小技巧

AI大模型與深度學(xué)習(xí)的關(guān)系

使用IBIS模型進(jìn)行時(shí)序分析

【vivado學(xué)習(xí)】典型時(shí)序模型的三條時(shí)鐘路徑分析

【vivado學(xué)習(xí)】典型時(shí)序模型的三條時(shí)鐘路徑分析

評論