在多時鐘設計中可能需要進行時鐘的切換。由于時鐘之間可能存在相位、頻率等差異,直接切換時鐘可能導致產生glitch。

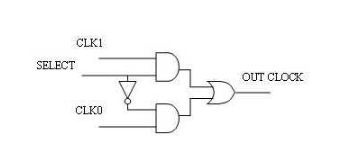

2|0組合邏輯實現時鐘切換:

2|1HDL代碼:

2|2電路圖:

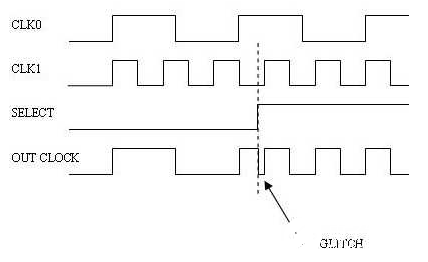

2|3波形圖:

2|4問題:

使用上述電路進行時鐘切換會導致在控制信號sel附近出現glitch。其原因在于控制信號可以在任意時刻進行時鐘切換,切換信號相對于兩個時鐘都是異步信號。

2|5解決方法:

使用寄存器使得控制信號僅在時鐘邊沿作用,避免在任何時鐘都為高電平是進行時鐘切換。

3|0適用于倍頻時鐘切換的時序邏輯電路

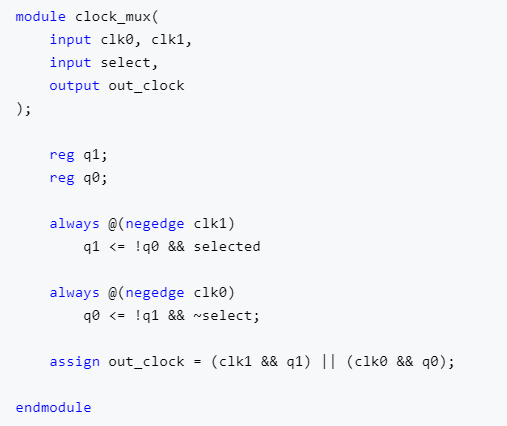

3|1HDL代碼:

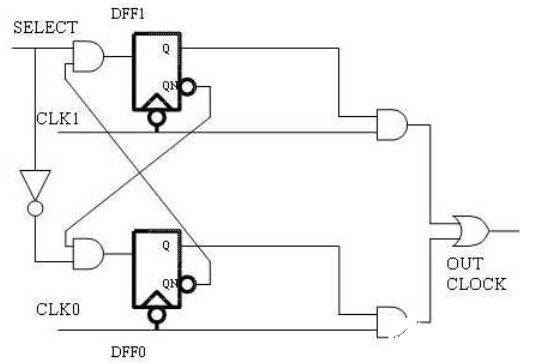

3|2電路圖:

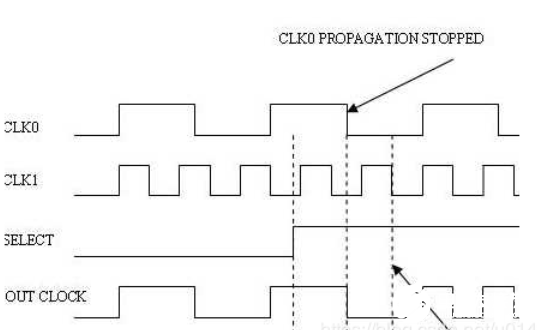

3|3波形圖:

3|4功能:

當切換的時鐘存在倍頻關系時,分別插入一個下降沿觸發的觸發器以確保控制信號僅在時鐘低電平時起作用。

3|5問題:

當DFF1輸入的變化非常接近CLK1的下降沿時,可能會導致DFF1的亞穩態問題;DFF0同理。

為什么可以用于倍頻時鐘之間的切換?

4|0異步時鐘切換的時序電路

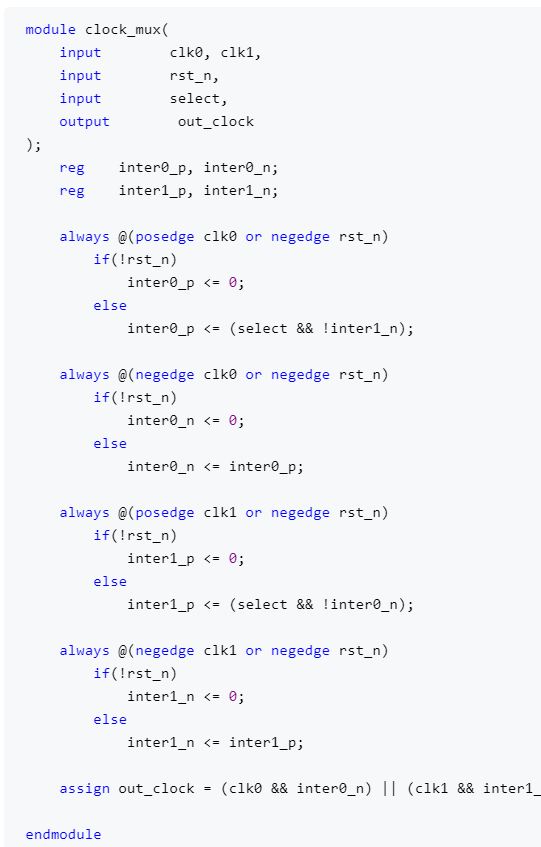

4|1HDL代碼:

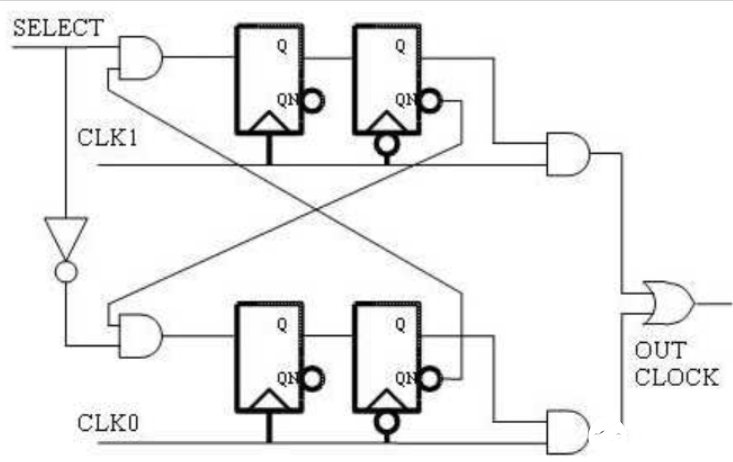

4|2電路圖:

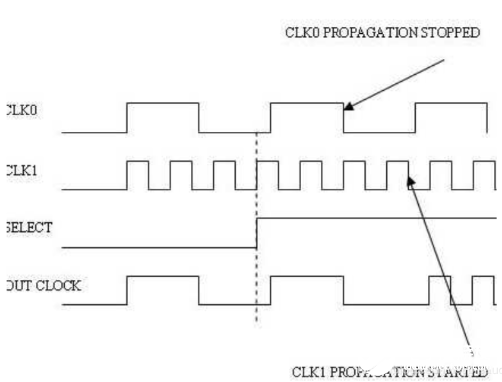

4|3波形圖:

4|4功能:

通過為每個時鐘源添加一個額外級的正邊沿觸發觸發器來提供針對亞穩態性的保護,CLK0的上升沿采樣到信號到下降沿傳遞至CLK1的正邊沿觸發器,并在CLK0下降沿后CLK1第一個上升沿之后的下降沿輸出。(不是很理解)

-

時鐘

+關注

關注

11文章

1879瀏覽量

132840 -

觸發器

+關注

關注

14文章

2032瀏覽量

61875 -

時序邏輯電路

+關注

關注

2文章

94瀏覽量

16768 -

時鐘設計

+關注

關注

0文章

27瀏覽量

11005 -

HDL代碼

+關注

關注

0文章

5瀏覽量

2170

發布評論請先 登錄

電容在時鐘電路中的應用有哪些

時鐘電路與晶振電路兩者的區別有哪些

HMC7044外參考時鐘切換失敗的原因?

時鐘緩沖器工作原理及常見時鐘緩沖器的國產替代情況

RTC時鐘芯片+電池的應用案例(一)

時序約束一主時鐘與生成時鐘

北斗衛星時鐘系統——ZREXT2000衛星時鐘擴展分機

LMK04828-EP參考時鐘自動切換的問題求解答

時鐘信號的驅動是什么

如何處理時鐘電路的常見故障

PLL1705/PLL1706雙通道PLL多時鐘發生器數據表

多時鐘設計中時鐘切換電路設計案例

多時鐘設計中時鐘切換電路設計案例

評論