。深入剖析PCBA加工的成本結(jié)構(gòu),有助于企業(yè)制定更具針對(duì)性的優(yōu)化策略。本文將從四個(gè)核心成本支出環(huán)節(jié)出發(fā),探討其成本構(gòu)成特點(diǎn)及潛在優(yōu)化空間。 PCBA加工 一、焊錫材料的質(zhì)量與成本 焊錫材料作為PCBA加工中的關(guān)鍵輔材,其質(zhì)量直接影響焊接品質(zhì)與產(chǎn)品可靠性。國產(chǎn)焊錫膏與進(jìn)口

![的頭像]() 發(fā)表于

發(fā)表于 04-23 16:40

?221次閱讀

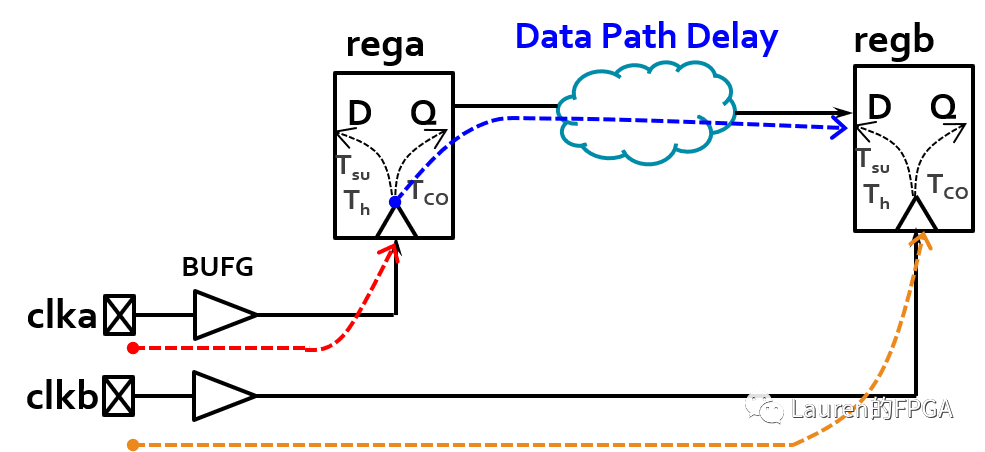

Vivado中時(shí)序分析工具默認(rèn)會(huì)分析設(shè)計(jì)中所有時(shí)鐘相關(guān)的時(shí)序路徑,除非時(shí)序約束中設(shè)置了時(shí)鐘組或false路徑。使用set_clock_gro

![的頭像]() 發(fā)表于

發(fā)表于 04-23 09:50

?291次閱讀

Vivado的時(shí)序約束是保存在xdc文件中,添加或創(chuàng)建設(shè)計(jì)的工程源文件后,需要?jiǎng)?chuàng)建xdc文件設(shè)置時(shí)序約束。時(shí)序約束文件可以直接創(chuàng)建或添加已存在的約束文件,創(chuàng)建約束文件有兩種方式:Constraints Wizard和Edit T

![的頭像]() 發(fā)表于

發(fā)表于 03-24 09:44

?2622次閱讀

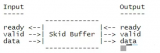

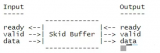

skid buffer(pipeline緩沖器)介紹 ??解決ready/valid兩路握手的時(shí)序困難,使路徑流水線化。 ??只關(guān)心valid時(shí)序參考這篇寫得很好的博客鏈接:?握手協(xié)議(pvld

![的頭像]() 發(fā)表于

發(fā)表于 03-08 17:10

?468次閱讀

Analysis,STA)是集成電路設(shè)計(jì)中的一項(xiàng)關(guān)鍵技術(shù),它通過分析電路中的時(shí)序關(guān)系來驗(yàn)證電路是否滿足設(shè)計(jì)的時(shí)序要求。與動(dòng)態(tài)仿真不同,STA不需要模擬電路的實(shí)際運(yùn)行過程,而是通過分析電路中的各個(gè)時(shí)鐘

![的頭像]() 發(fā)表于

發(fā)表于 02-19 09:46

?498次閱讀

AD轉(zhuǎn)換中需要注意 電流的回流路徑 這個(gè)電流的回流路徑具體指的是什么呢

是不是單片機(jī)和AD轉(zhuǎn)換芯片之間的數(shù)據(jù)線和DGND線構(gòu)成一個(gè)回路輸入信號(hào)和AGND

發(fā)表于 02-14 07:53

最近在看JT大佬出的一本高速PCB設(shè)計(jì)書籍,看到回流路徑這里,讓我想到最近兩個(gè)群里都提到關(guān)于這個(gè)知識(shí)點(diǎn)的問題。書籍很好,但是也會(huì)有一些疑問,帶著這些疑問我也查找了相關(guān)資料,我想著盡可能的結(jié)合書中知識(shí)以及自己的理解,把這個(gè)問題能給

![的頭像]() 發(fā)表于

發(fā)表于 12-25 10:17

?2011次閱讀

AGV系統(tǒng)由調(diào)度、車載控制、導(dǎo)航導(dǎo)引三部分構(gòu)成,實(shí)現(xiàn)物流自動(dòng)化智能化。調(diào)度系統(tǒng)分配任務(wù),車載系統(tǒng)控制導(dǎo)航裝卸,導(dǎo)航導(dǎo)引確保精確行駛。AGV采用雙控系統(tǒng),提高適應(yīng)性,用戶可實(shí)時(shí)查看運(yùn)行狀態(tài)。

![的頭像]() 發(fā)表于

發(fā)表于 10-18 17:48

?792次閱讀

時(shí)序邏輯電路確實(shí)具有記憶功能 。這一特性是時(shí)序邏輯電路與組合邏輯電路的本質(zhì)區(qū)別之一。

![的頭像]() 發(fā)表于

發(fā)表于 08-29 10:31

?1297次閱讀

在時(shí)序邏輯電路中,有效狀態(tài)和無效狀態(tài)的判斷是電路分析和設(shè)計(jì)的重要環(huán)節(jié)。有效狀態(tài)是指電路在實(shí)際工作過程中被利用到的狀態(tài),它們構(gòu)成了電路的有效循環(huán);而無效狀態(tài)則是指那些沒有被利用到,或者雖然存在但不影響電路正常工作的狀態(tài)。以下是對(duì)如何判斷時(shí)

![的頭像]() 發(fā)表于

發(fā)表于 08-12 15:51

?4549次閱讀

(Control Relay)是兩種不同的電子設(shè)備,它們?cè)诠δ芎蛻?yīng)用上有所區(qū)別。 電源時(shí)序器 1.1 概念 電源時(shí)序器是一種用于控制多個(gè)電源設(shè)備按特定順序開啟或關(guān)閉的電子設(shè)備。它可以根據(jù)用戶設(shè)定的

![的頭像]() 發(fā)表于

發(fā)表于 07-08 14:30

?1046次閱讀

電源時(shí)序器是一種電子設(shè)備,用于控制多個(gè)電源的開啟和關(guān)閉順序,以確保設(shè)備按照正確的順序啟動(dòng)和關(guān)閉。電源時(shí)序器廣泛應(yīng)用于工業(yè)自動(dòng)化、電力系統(tǒng)、通信系統(tǒng)等領(lǐng)域。 一、電源

![的頭像]() 發(fā)表于

發(fā)表于 07-08 14:19

?1425次閱讀

電源時(shí)序器是一種用于控制多個(gè)電源設(shè)備按照一定順序開啟或關(guān)閉的電子設(shè)備。它廣泛應(yīng)用于音響、舞臺(tái)燈光、電視廣播、工業(yè)自動(dòng)化等領(lǐng)域。本文將介紹電源時(shí)序器的原理及使用方法。

![的頭像]() 發(fā)表于

發(fā)表于 07-08 14:16

?4072次閱讀

結(jié)果當(dāng)然是要求系統(tǒng)時(shí)序滿足設(shè)計(jì)者提出的要求。

下面舉一個(gè)最簡單的例子來說明時(shí)序分析的基本概念。

假設(shè)信號(hào)需要從輸入到輸出在FPGA 內(nèi)部經(jīng)過一些邏輯延時(shí)和

發(fā)表于 06-17 17:07

TDK最新xEV解決方案,一文全知道! TDK致力于為各類xEV提供廣泛的產(chǎn)品組合,進(jìn)而推動(dòng)未來汽車的發(fā)展。 TDK在汽車行業(yè)中發(fā)揮著至關(guān)重要的作用,尤其是在電動(dòng)汽車時(shí)代,從先進(jìn)的電力電子器件

![的頭像]() 發(fā)表于

發(fā)表于 06-16 13:49

?628次閱讀

一文知道時(shí)序路徑的構(gòu)成

一文知道時(shí)序路徑的構(gòu)成

評(píng)論