1.設(shè)置安全間距(Clearance Constraint):定義同一個(gè)工作層面上兩個(gè)圖元之間的最小間距,例如焊盤(Pad)和走線(Track)之間的間距。可以雙擊它或者單擊按鈕 Properties進(jìn)入安全間距參數(shù)設(shè)置對(duì)話框進(jìn)行參數(shù)設(shè)置,參數(shù)包括PCB設(shè)計(jì)布線范圍(Rule scope)和PCB設(shè)計(jì)布線屬性(Rule Attributes)。

2.設(shè)置拐角模式(Rules Corners):定義PCB設(shè)計(jì)布線時(shí)拐角的形狀以及最小和最大的允許尺寸。

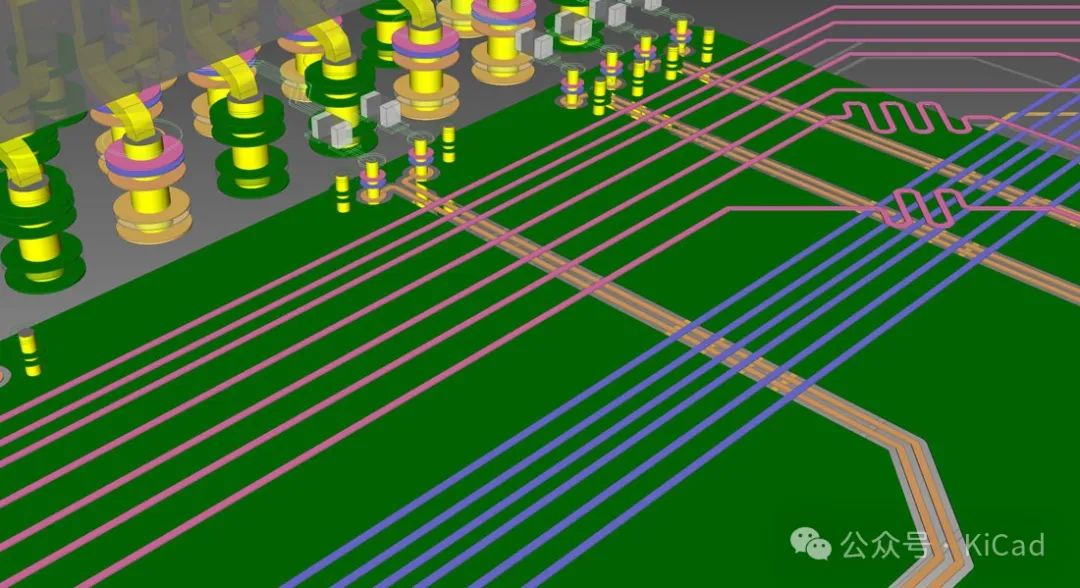

3.設(shè)置PCB設(shè)計(jì)布線工作層面(Routing Layers):用于設(shè)置PCB設(shè)計(jì)布線的工作層面以及各個(gè)PCB設(shè)計(jì)布線層面上的走線方向,它的PCB設(shè)計(jì)布線屬性里可以分別對(duì)頂層和底層的PCB設(shè)計(jì)布線方向進(jìn)行設(shè)置,PCB設(shè)計(jì)布線方向有水平方向、垂直方向等。

4.設(shè)置PCB設(shè)計(jì)布線優(yōu)先級(jí)(Routing Priority):指程序允許用戶設(shè)定各個(gè)網(wǎng)絡(luò)PCB設(shè)計(jì)布線的順序,優(yōu)先級(jí)高的PCB設(shè)計(jì)布線早,優(yōu)先級(jí)低的PCB設(shè)計(jì)布線遲。有0~100共101個(gè)優(yōu)先級(jí)選擇,0最低,100最高。

5.設(shè)置PCB設(shè)計(jì)布線拓?fù)浣Y(jié)果(Routing Topology):定義管腳到管腳之間PCB設(shè)計(jì)布線的規(guī)則。

6.設(shè)置過孔形式(Routing Via Style):用于定義各層之間過孔的類型和有關(guān)尺寸。

7.設(shè)置PCB設(shè)計(jì)布線寬度(Width Constraint):定義PCB設(shè)計(jì)布線時(shí)導(dǎo)線寬度的最大和最小允許值。

-

pcb

+關(guān)注

關(guān)注

4352文章

23412瀏覽量

406708 -

PCB布線

+關(guān)注

關(guān)注

21文章

468瀏覽量

42514

發(fā)布評(píng)論請(qǐng)先 登錄

高速PCB布局/布線的原則

PCB的EMC設(shè)計(jì)(一):層的設(shè)置與排布原則

高層數(shù)層疊結(jié)構(gòu)PCB的布線策略

Altium Designer中PCB設(shè)計(jì)規(guī)則設(shè)置

104條關(guān)于PCB布局布線的小技巧

KiCad使用 “F” 鍵自動(dòng)布線?

了解TI基于PCB布線規(guī)則的DDR時(shí)序規(guī)范

在DSP上實(shí)現(xiàn)DDR2 PCB布局布線

AM62 PCB設(shè)計(jì)逃逸布線應(yīng)用說明

飛凌嵌入式-ELFBOARD 解決PCB布線時(shí)無法捕捉到焊盤中心的問題

AM62x(AMC)PCB設(shè)計(jì)逃逸布線應(yīng)用說明

AM62Px PCB設(shè)計(jì)迂回布線

AM62x SiP PCB設(shè)計(jì)迂回布線

干貨!PCB布局布線九大最全要點(diǎn)

淺談PCB設(shè)置自動(dòng)布線的技巧

淺談PCB設(shè)置自動(dòng)布線的技巧

評(píng)論