高層數 PCB 的布線策略豐富多樣,具體取決于 PCB 的功能。這類電路板可能涉及多種不同類型的信號,從低速數字接口到具有不同信號完整性要求的多個高速數字接口。從布線規劃和為各接口分配信號層的角度來看,這無疑是一項極具挑戰性的任務。

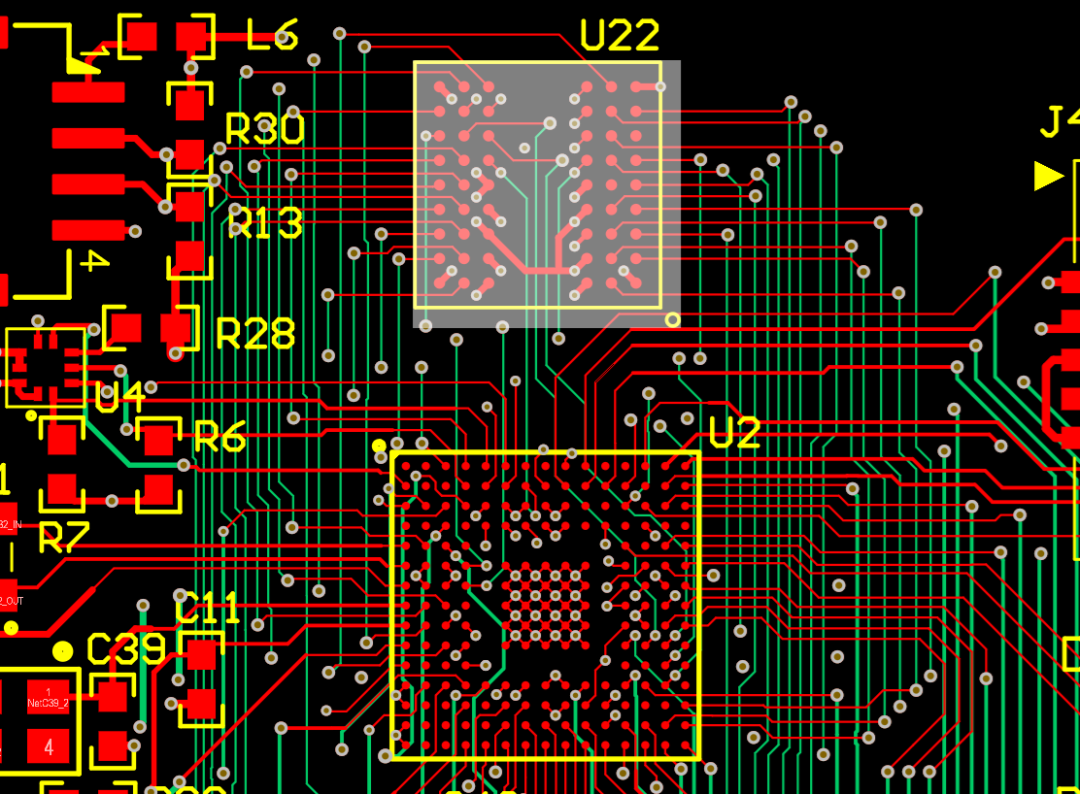

提及高層數 PCB 的布線策略,就不得不談到眾多BGA封裝的引腳布局設計。高引腳數 BGA 通常包含多種不同的數字接口,尤其是當元件為典型的微處理器或FPGA時。這是導致 PCB 層數增加的最常見因素之一。

由于高層數設計中往往同時面臨多個挑戰,本文將逐一解析這些挑戰,并分享能夠成功實現高層數 PCB 布線的實用策略。

是什么導致 PCB 層數增加?

如引言所述,導致 PCB 層數變高的最常見因素是大型BGA元件的存在。這類元件在器件底部具有高密度引腳,為使信號到達每個引腳,需要更多的線路層。由于這些元件多為專用ASIC、微處理器或FPGA,它們還集成了大量對信號完整性和布線要求各異的數字接口,以及眾多電源和接地引腳。

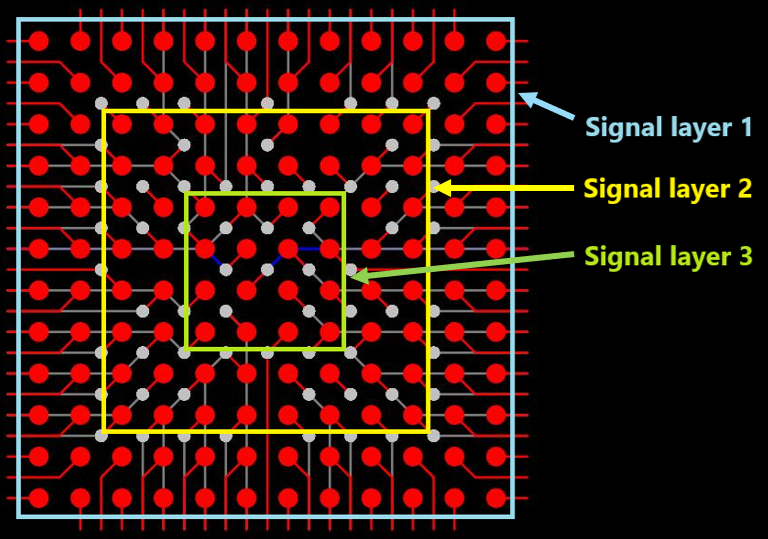

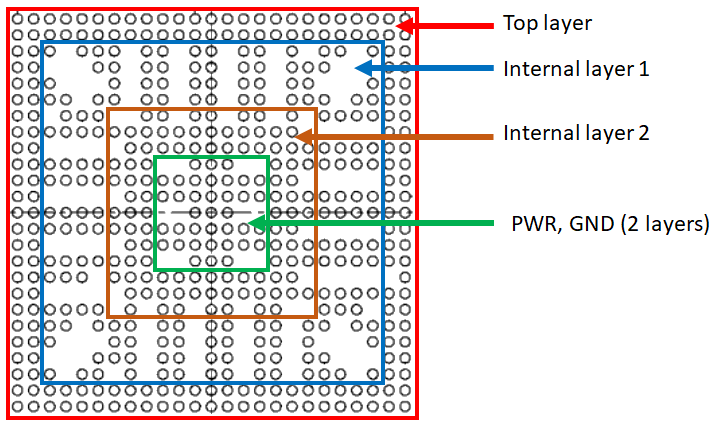

許多設計師都能熟悉估算 BGA 引腳全連接所需層數的簡單公式。當 BGA 的焊球間距足夠大(允許在引腳間布線)時,每層信號層可容納兩行 BGA 引腳:

對于粗間距 BGA 封裝(焊球間可布置走線),每層可布線 2 行 / 列信號。 部分 BGA 封裝的焊盤布局較為復雜,內層行可能存在缺失的焊球(如下圖示例),此類 BGA 的層數計算通常不同于上述標準 BGA。

當元件引腳間距極細(BGA 焊盤間無法布線)時,所需層數需翻倍;若大量引腳為電源和接地引腳,層數則會減少。此外,大量四方扁平封裝(Quad 封裝)也可能導致高層數需求,但其引腳數通常遠低于中等尺寸 BGA(高端 Quad 封裝約有幾百個引腳,而中等 BGA 引腳數更高)。

四大核心布線策略

策略 1:“無策略”

“無策略” 策略是迄今為止最簡單的方法,其核心是在確保可布線性的同時盡量減少層數。具體實施方式包括:選擇所需層數并通過標準扇出方法從 BGA 布線、采用固定層數緊湊排布所有走線,或自由布線并根據需求添加新信號層。該策略適用于以下場景:

無需按阻抗規格將不同信號分隔到不同層

所有接口均無阻抗要求(如串行外設接口 SPI)

所有接口的阻抗要求一致

有阻抗規格要求的接口數量極少(如 1-2 個)

盡管采用這種策略的布線可能顯得不夠規整,但通過弱化信號完整性要求以換取可布線性,能有效控制層數,避免其層數高于其他策略。

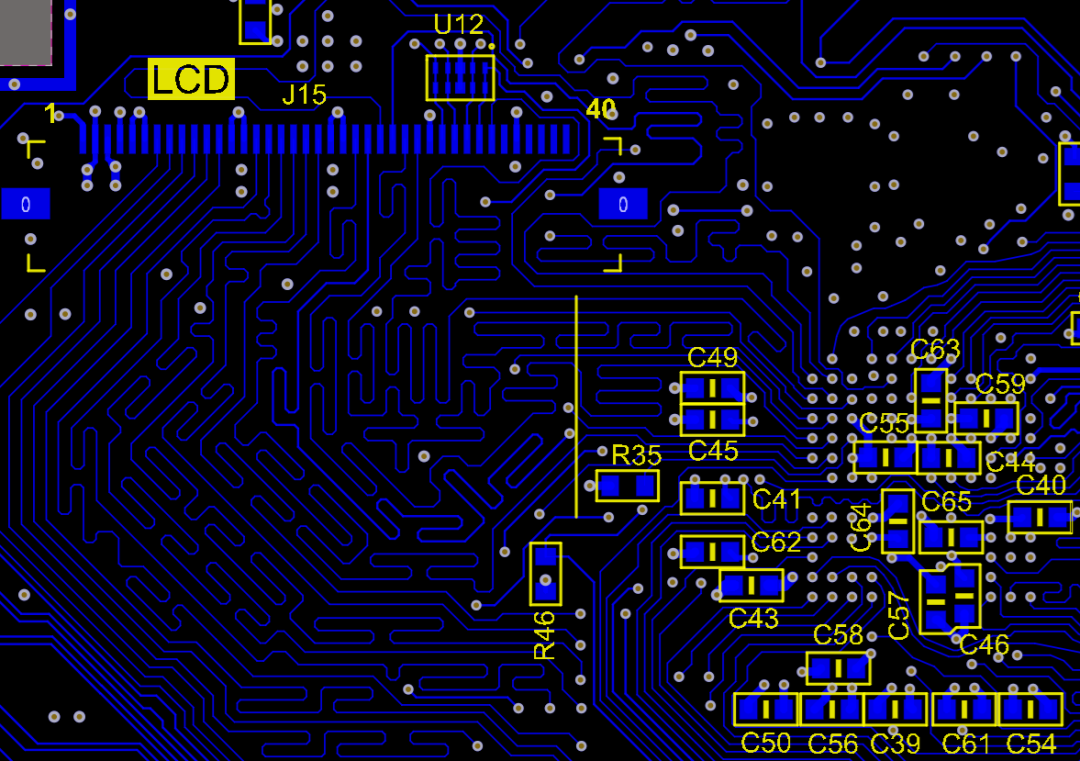

示例:該并行接口從 BGA(右下角)起始布線,連接至外接 LCD 模塊(左上角)。

策略 2:按接口優先級分配層

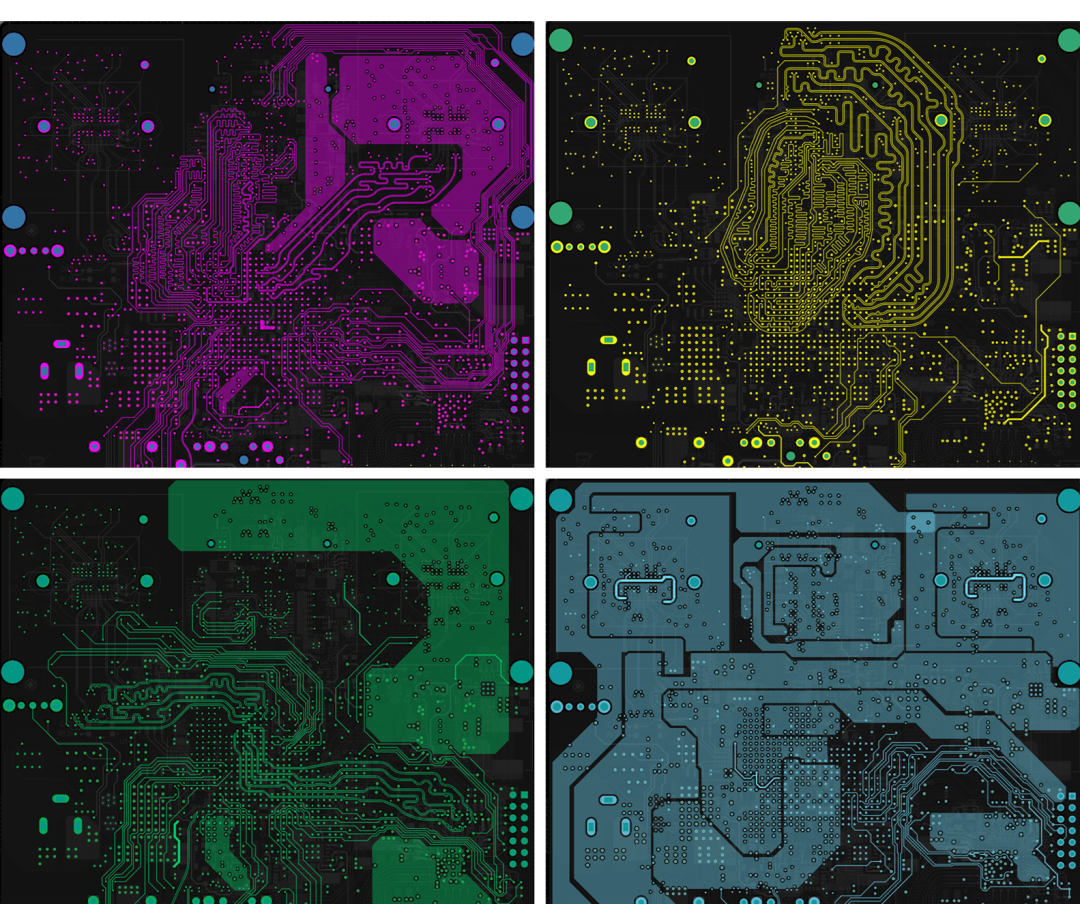

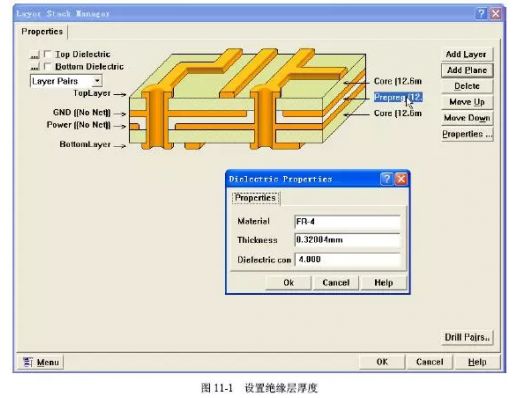

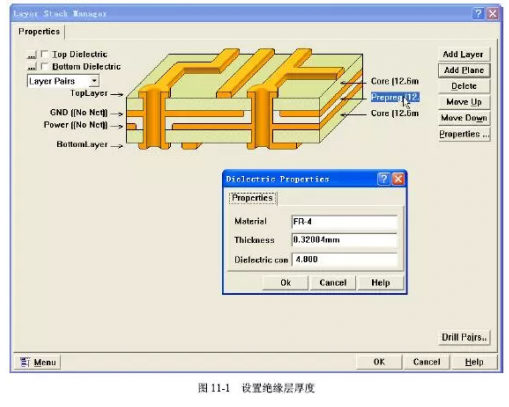

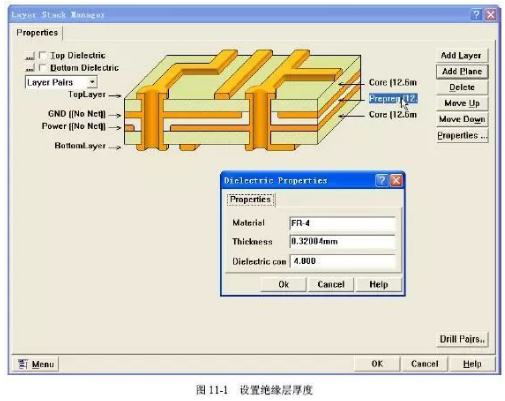

在此策略中,特定的阻抗受控接口會被分配專屬的信號層,并且主要在這些層內進行布線。制造商隨后采用阻抗控制方法,確定構建電路板層疊結構時使用的電氣特性。當存在多個需要阻抗控制且可能具有不同目標阻抗值的高速接口時,可采用這種策略。對于部分差分接口,盡管其標稱阻抗目標相同,但帶寬需求可能不同,這就需要為不同接口設置不同的線寬和間距。 在下方示例圖中,展示了 16 層疊結構中多個數字接口的分層分配情況,涉及的接口包括:

DDR4

CSI-2

1 Gbps LVDS

10 Gbps 以太網

具體可見下方圖表中這些接口如何被分配到不同層中。

高層數 PCB 中多數字接口的高速布線示例 您會注意到這些層上存在一些空白區域。需要明確的是,這種分層策略的主要目標是讓制造商更容易實現阻抗規格定義。當每層僅對應一種阻抗規格時,制造商就能更便捷地生產出滿足每個接口阻抗目標的層疊結構。 該策略的缺點在于可能會導致層數增加,且部分層會出現未利用的空白區域。若有需要,您可以用額外的地線或銅電源鋪銅來填充一些空白區域。在某些設計中,我傾向于將這些區域用于布置電源鋪銅,這甚至可能讓我省去一個專用電源層。此外,您仍然可以使用這些阻抗控制層來傳輸低速或配置信號,只要它們不要擠得太靠近高速走線即可。

策略 3:高速層與低速層分離

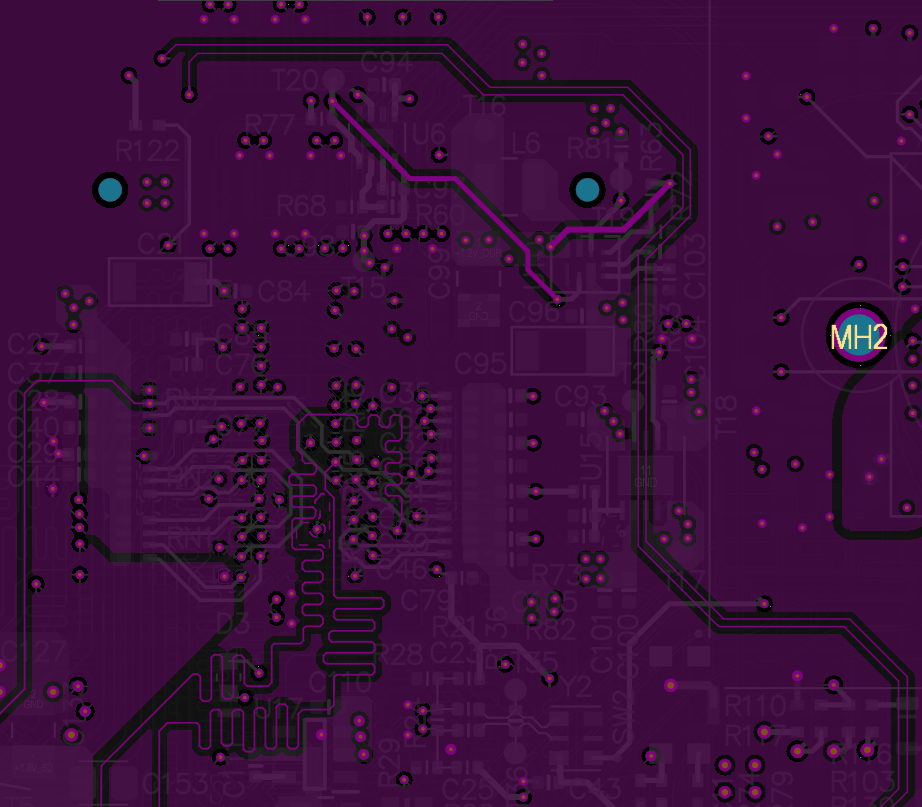

此策略適用于需要阻抗控制的接口數量較少,或所有阻抗受控接口具有相同阻抗要求的場景。通過將信號分隔到專用的高速層和低速層,可實現更清晰的分層設計。這類似于在六層板中設置四個信號層,將低速信號層相鄰放置的做法。 這種策略適合采用正交布線(相鄰層信號走向垂直),尤其當低速信號分布在相鄰層時效果更佳。例如,下方示例中的布線在兩個不同層上的元件之間采用正交走向:

這些輸入 / 輸出(I/O)屬于同步SDRAM接口,通過正交布線方法可輕松連接至存儲芯片。 由于低速信號占比比較高,此策略面臨的信號完整性挑戰較少,有助于維持合理的層數,避免因過度分層導致設計復雜。

策略 4:電源與信號共層設計

在高層數電路板設計中,我經常采用的另一種布線策略是將部分信號與電源鋪銅整合到同一層。 層數增加的常見原因不僅是需要布線的信號或接口數量龐大,多個電源通路和電源供應也會導致層數上升。新手設計師可能認為每個電源通路都需要一個專用電源層,但這會導致創建過多層數,使用不必要的銅箔。更優的策略是將電源通路以多邊形鋪銅形式繪制在層上。 在繪制了電源鋪銅的層中,允許布置信號走線,尤其是低速信號或配置信號。如下圖所示的示例布線:

只要保持足夠間距,在電源層布線是可行的。 這種方法可與策略 2 結合使用,利用未分配給接地層的剩余層來布置低速信號,而高速信號仍可根據需要在策略 2 下擁有專屬層。通過省去專用電源層和低速信號層,有效避免層數過高。 此外,含電源鋪銅的層仍可布置阻抗受控走線,但需執行間距規則以防止過大電容影響走線阻抗。這與在共面接地層布線的原理一致:避免使用全局電氣間距規則,而是創建網絡和層專屬的間距規則。在 Altium Designer 中,可通過自定義查詢(利用 InNet/InNetClass 和 InLayer 條件)設置此類規則。

無論是制造電力電子設備,還是應對跨領域協作挑戰,Altium Designer 的全套 PCB 設計功能與 Altium 365 平臺都能輕松滿足需求,支持設計數據無縫共享與生產流程高效推進。這僅僅是 Altium 解決方案的一小部分,立即免費試用 Altium Designer + Altium 365,探索高層數 PCB 設計的無限可能!

關于Altium

Altium有限公司隸屬于瑞薩集團,總部位于美國加利福尼亞州圣迭戈,是一家致力于加速電子創新的全球軟件公司。Altium提供數字解決方案,以最大限度提高電子設計的生產力,連接整個設計過程中的所有利益相關者,提供對元器件資源和信息的無縫訪問,并管理整個電子產品生命周期。Altium生態系統加速了各行業及各規模企業的電子產品實現進程。

-

pcb

+關注

關注

4346文章

23361瀏覽量

405761 -

電路板

+關注

關注

140文章

5072瀏覽量

101129 -

altium

+關注

關注

47文章

964瀏覽量

119519 -

BGA

+關注

關注

5文章

563瀏覽量

48053 -

Designer

+關注

關注

0文章

131瀏覽量

36274

原文標題:【技術博客】高層數層疊結構 PCB 的布線策略

文章出處:【微信號:AltiumChina,微信公眾號:Altium】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

高層數層疊結構PCB的布線策略

高層數層疊結構PCB的布線策略

評論