近年來(lái),先進(jìn)封裝技術(shù)的內(nèi)驅(qū)力已從高端智能手機(jī)領(lǐng)域演變?yōu)楦咝阅苡?jì)算和人工智能等領(lǐng)域,涉及高性能處理器、存儲(chǔ)器、人工智能訓(xùn)練和推理等。當(dāng)前集成電路的發(fā)展受“四堵墻”(“存儲(chǔ)墻”“面積墻”“功耗墻”和“功能墻”)制約,以芯粒(Chiplet)異質(zhì)集成為核心的先進(jìn)封裝技術(shù),將成為集成電路發(fā)展的關(guān)鍵路徑和突破口。文章概述近年來(lái)國(guó)際上具有“里程碑”意義的先進(jìn)封裝技術(shù),闡述中國(guó)大陸先進(jìn)封裝領(lǐng)域發(fā)展的現(xiàn)狀與優(yōu)勢(shì),分析中國(guó)大陸先進(jìn)封裝關(guān)鍵技術(shù)與世界先進(jìn)水平的差距,最后對(duì)未來(lái)中國(guó)大陸先進(jìn)封裝發(fā)展提出建議。

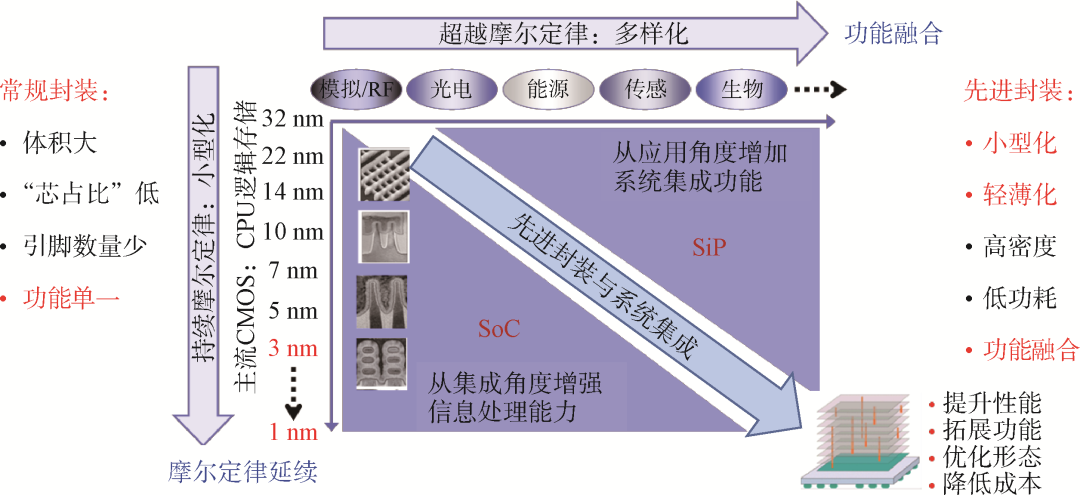

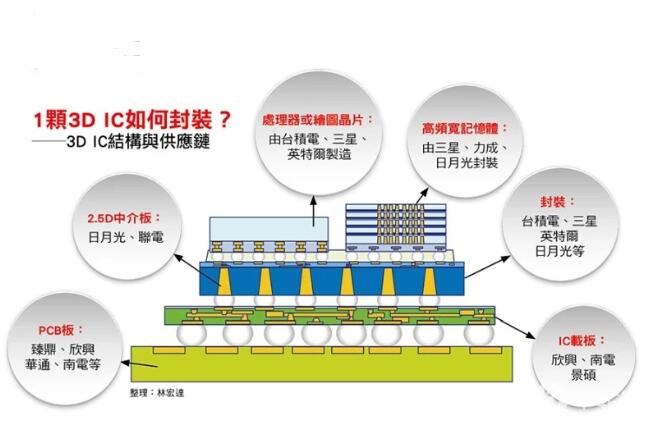

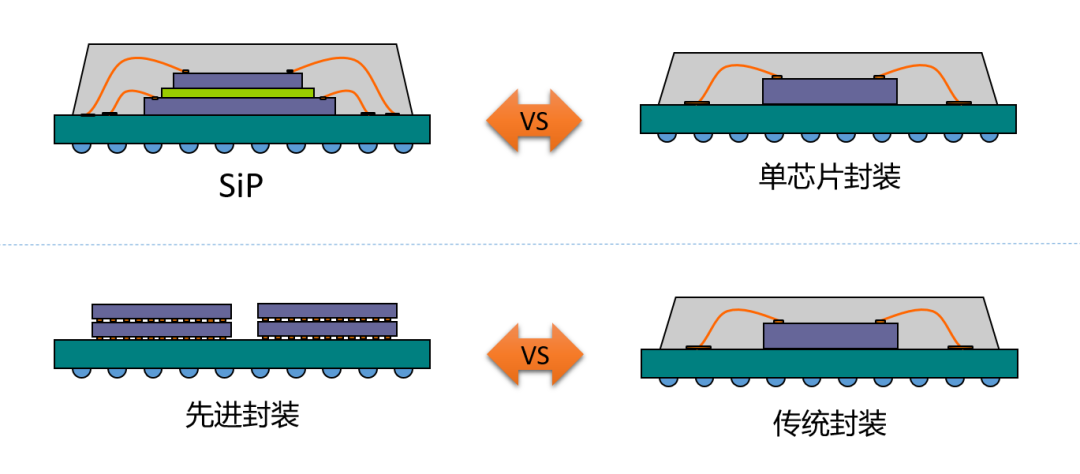

集成電路是國(guó)之重器,設(shè)計(jì)、制造和封裝是集成電路產(chǎn)業(yè)發(fā)展的三大支柱;封裝是芯片實(shí)用化的起點(diǎn),是溝通芯片內(nèi)部世界與外部系統(tǒng)的橋梁。集成電路沿著兩條技術(shù)路線(xiàn)發(fā)展(圖1),一條是持續(xù)摩爾定律,向小型化方向發(fā)展,即通過(guò)微縮互補(bǔ)金屬氧化物半導(dǎo)體(Complementary Metal- Oxide-Semiconductor, CMOS)器件的晶體管柵極尺寸增加芯片晶體管數(shù)量,從而提升芯片的性能。到目前為止,工藝制程已發(fā)展至5 nm節(jié)點(diǎn),主要產(chǎn)品為圖像處理器(GPU)和中央處理器(CPU),全世界只有中國(guó)臺(tái)灣積體電路制造股份有限公司(簡(jiǎn)稱(chēng)臺(tái)積電)、美國(guó)英特爾和韓國(guó)三星等公司具備10 nm及以下節(jié)點(diǎn)的制造能力。另一條是超越摩爾定律,向多樣化方向發(fā)展,即采用先進(jìn)的封裝技術(shù)將處理、模擬/射頻(Radio Frequency, RF)、光電、能源、傳感、生物等集成在一個(gè)系統(tǒng)內(nèi),進(jìn)行系統(tǒng)級(jí)封裝(System in Package, SiP),實(shí)現(xiàn)系統(tǒng)性能的提升。相比常規(guī)封裝,先進(jìn)封裝具有小型化、輕薄化、高密度、低功耗和功能融合等優(yōu)點(diǎn),不僅可以提升性能、拓展功能、優(yōu)化形態(tài),相比系統(tǒng)級(jí)芯片(System on Chip, SoC),還可以降低成本。

圖1 集成電路發(fā)展路線(xiàn)圖

01 先進(jìn)封裝技術(shù)發(fā)展特點(diǎn)

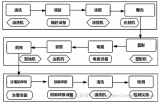

封裝技術(shù)的發(fā)展史是芯片性能不斷提高、系統(tǒng)不斷小型化的歷史,大致分為4個(gè)階段:第1階段(1970年前),直插型封裝,以雙列直插封裝(Dual In-line Package, DIP)為主;第2階段(1970—1990年),以表面貼裝技術(shù)衍生出的小外形封裝(Small Outline Package, SOP)、J型引腳小外形封裝(Small Outline J-leaded, SOJ)、無(wú)引腳芯片載體(Leadless Chip Carrier, LCC)、扁平方形封裝(Quad Flat Package, QFP)4大封裝技術(shù)和針柵陣列(Pin Grid Array, PGA)技術(shù)為主;第3階段(1990—2000年),球柵陣列(Ball Grid Array, BGA)、芯片尺寸封裝(Chip Scale Package, CSP)、倒裝芯片(Flip-Chip, FC)封裝等先進(jìn)封裝技術(shù)開(kāi)始興起;第4階段(2000年至今),從二維封裝向三維封裝發(fā)展,出現(xiàn)了晶圓級(jí)封裝(Wafer Level Package, WLP)、系統(tǒng)級(jí)封裝、扇出型(Fan-Out, FO)封裝、2.5D/3D封裝、嵌入式多芯片互連橋接(Embedded Multi-die Interconnect Bridge, EMIB)等先進(jìn)封裝技術(shù)。

近年來(lái),先進(jìn)封裝技術(shù)的內(nèi)驅(qū)力已從高端智能手機(jī)領(lǐng)域演變?yōu)楦咝阅苡?jì)算和人工智能等領(lǐng)域,涉及高性能處理器、存儲(chǔ)器、人工智能訓(xùn)練和推理等。

當(dāng)前,除了傳統(tǒng)委外封測(cè)代工廠(chǎng)(OSAT)和科研機(jī)構(gòu)做封裝外,晶圓代工廠(chǎng)(Foundry)、整合元器件制造商(IDM)、無(wú)廠(chǎng)半導(dǎo)體公司(Fabless)、原始設(shè)備制造商(OEM)都在大力發(fā)展先進(jìn)封裝或相關(guān)關(guān)鍵技術(shù)。目前臺(tái)積電已成為先進(jìn)封裝技術(shù)創(chuàng)新的引領(lǐng)者之一,相繼推出了基板上晶圓上的芯片(Chip on Wafer on Substrate, CoWoS)封裝、整合扇出型(Integrated Fan-Out, InFO)封裝、系統(tǒng)整合芯片(System on Integrated Chips, SoIC)等;英特爾推出了EMIB、Foveros和Co-EMIB等先進(jìn)封裝技術(shù),力圖通過(guò)2.5D、3D和埋入式3種異質(zhì)集成形式實(shí)現(xiàn)互連帶寬倍增與功耗減半的目標(biāo);三星電子推出了扇出型面板級(jí)封裝(Fan-Out Panel Level Package, FOPLP)技術(shù),在大面積的扇出型封裝上進(jìn)一步降低封裝體的剖面高度、增強(qiáng)互連帶寬、壓縮單位面積成本,取得性?xún)r(jià)比的優(yōu)勢(shì)。

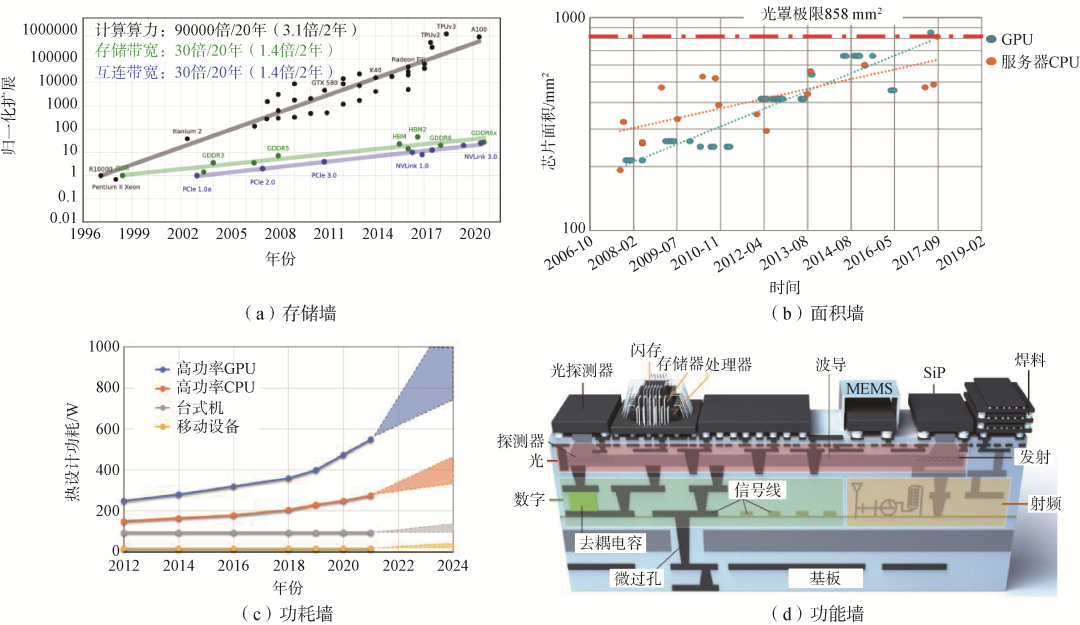

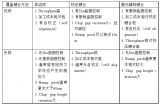

當(dāng)前集成電路的發(fā)展受“存儲(chǔ)墻”“面積墻”“功耗墻”和“功能墻”這“四堵墻”的制約。如圖2(a)。所示,處理器的峰值算力每?jī)赡暝鲩L(zhǎng)3.1倍,而動(dòng)態(tài)存儲(chǔ)器的帶寬每?jī)赡暝鲩L(zhǎng)1.4倍,存儲(chǔ)器的發(fā)展速度遠(yuǎn)落后于處理器,相差1.7倍。為了突破“存儲(chǔ)墻”,業(yè)界提出了存內(nèi)計(jì)算和近存計(jì)算兩種技術(shù)途徑,其中存內(nèi)計(jì)算的能效高、精度低;近存計(jì)算的算力高、精度高,它是一種基于先進(jìn)封裝的技術(shù)途徑,通過(guò)超短互連技術(shù),可實(shí)現(xiàn)存儲(chǔ)器和處理器之間數(shù)據(jù)的近距離搬運(yùn)。

圖2 集成電路發(fā)展面臨的挑戰(zhàn)

當(dāng)芯片制程相同時(shí),通過(guò)增大芯片面積可以集成更多的晶體管數(shù)量,從而提升芯片的性能,然而,芯片尺寸受限于光刻機(jī)的光罩極限,如圖2(b)所示,當(dāng)前最先進(jìn)的極紫外光刻機(jī)的最大光罩面積為858 mm2(26 mm×33 mm)。2020年,美國(guó)英偉達(dá)公司發(fā)布了A100 GPU芯片,采用臺(tái)積電7 nm鰭式場(chǎng)效應(yīng)晶體管(Fin Field-Effect Transistor, FinFET)工藝,通過(guò)常規(guī)手段制造了接近1個(gè)光罩面積的芯片,面積達(dá)826 mm2(~25.5 mm×32.4 mm),擁有540億個(gè)晶體管,單精度(FP32)算力高達(dá)19.5 TFLOPS,存儲(chǔ)帶寬為2.039 TB/s。2019年,美國(guó)人工智能初創(chuàng)公司Cerebras System通過(guò)臺(tái)積電芯片間連接技術(shù)(Cross-die Wires)推出了世界上最大的芯片,面積達(dá)到46225 mm2(215 mm×215 mm),約等于A100的56倍,存儲(chǔ)帶寬達(dá)20 PB/s,該技術(shù)雖突破了1個(gè)光罩面積,但成本極高。當(dāng)前,通過(guò)先進(jìn)封裝技術(shù)集成多顆芯片是突破芯片“面積墻”的一種低成本主流方案。

如圖2(c)所示,近年來(lái)單個(gè)GPU和CPU的熱設(shè)計(jì)功耗(Thermal Design Power, TDP)逐年增大。2024年單個(gè)GPU的TDP將突破千瓦級(jí),由多個(gè)GPU芯片和高帶寬存儲(chǔ)器(High Bandwidth Memory, HBM)陣列組成的系統(tǒng),TDP可能突破萬(wàn)瓦級(jí),熱設(shè)計(jì)者將面臨極大的挑戰(zhàn),為突破“功耗墻”,迫切需要采用更先進(jìn)的冷卻技術(shù)。

單一襯底可實(shí)現(xiàn)的功能有限,為突破“功能墻”,可通過(guò)多芯片異質(zhì)集成技術(shù),將傳感、存儲(chǔ)、計(jì)算、通信等不同功能的元器件集成在一起,實(shí)現(xiàn)電、磁、熱、力等多物理場(chǎng)的有效融合,如圖2(d)所示。

02 先進(jìn)封裝技術(shù)研究進(jìn)展

以芯粒(Chiplet,又稱(chēng)小芯片)異質(zhì)集成為核心的先進(jìn)封裝技術(shù),將成為集成電路發(fā)展的關(guān)鍵路徑和突破口。本節(jié)將介紹與芯粒相關(guān)的先進(jìn)封裝技術(shù)研究進(jìn)展,包括芯粒異質(zhì)集成技術(shù)和典型先進(jìn)封裝技術(shù)兩部分。

2.1 芯粒異質(zhì)集成技術(shù)

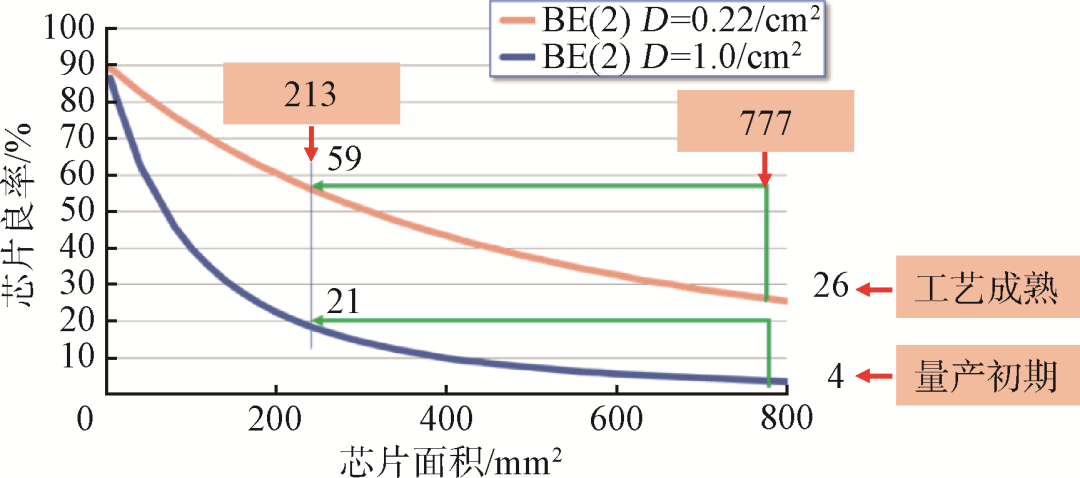

增大芯片尺寸可增多晶體管數(shù)量,從而可以集成更復(fù)雜的微體系結(jié)構(gòu)、更多的片上存儲(chǔ)器以及更多的內(nèi)核,提高芯片性能。然而,芯片尺寸受限于光罩極限,且芯片良率隨尺寸的增大而降低。如圖3所示,工藝成熟后,當(dāng)芯片面積從213 mm2增至777 mm2時(shí),良率降低了33%,因此,芯片的成本隨尺寸的增大而增加,芯粒異質(zhì)集成技術(shù)已成為維持摩爾定律和超越光罩極限的一種有效方法。

圖3 芯片良率與芯片面積的關(guān)系

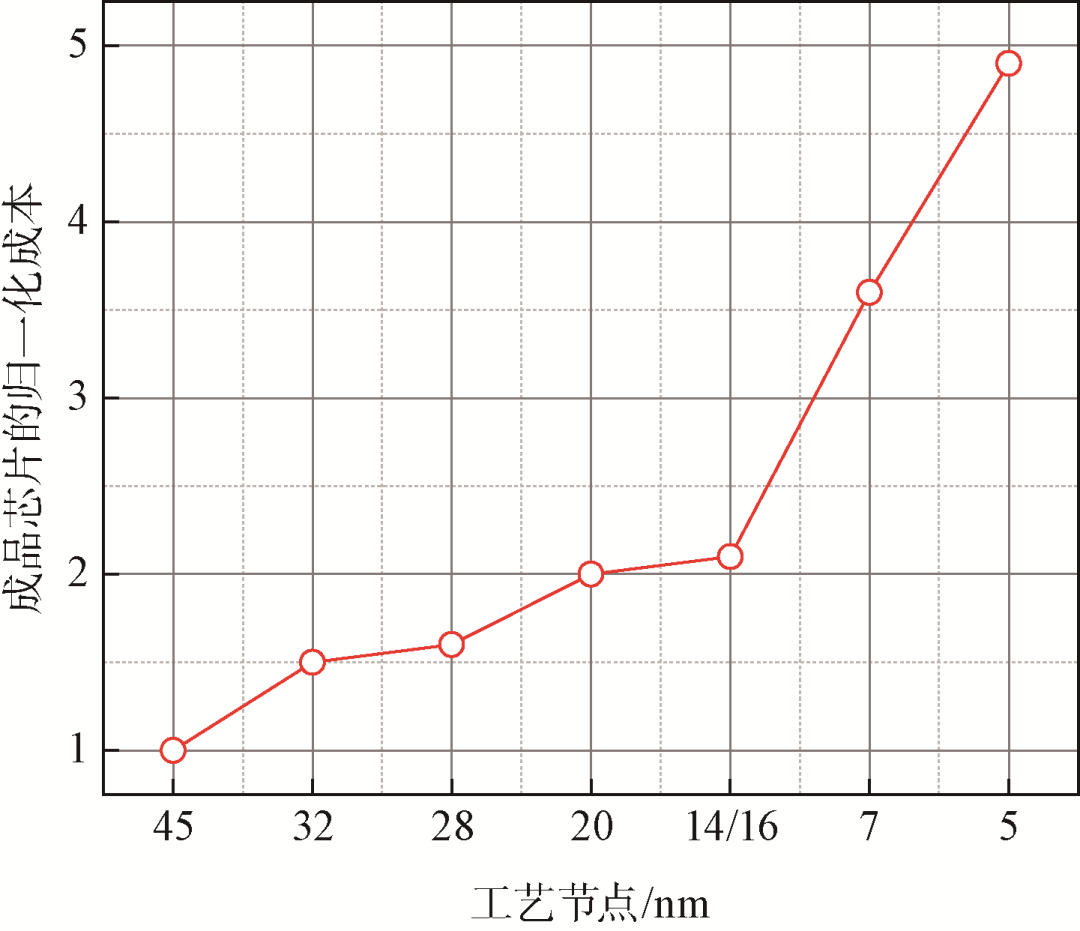

采用更先進(jìn)的制程也可提升芯片的性能。然而,隨著工藝節(jié)點(diǎn)向小微縮,采用先進(jìn)制程制造大芯片的成本越來(lái)越高,如圖4所示。相比采用45 nm節(jié)點(diǎn)制造的250 mm2的芯片,采用16 nm工藝節(jié)點(diǎn)后,芯片每平方毫米的成本增加1倍以上,采用5 nm工藝后,成本將增加4~5倍,因此摩爾定律已從單個(gè)晶體管微縮向系統(tǒng)級(jí)微縮演變。芯粒是一種有效的片間互連和封裝架構(gòu),即將大芯片拆分成多顆芯粒,以搭積木的形式將不同功能、不同合適工藝節(jié)點(diǎn)制造的芯粒封裝在一起。拆解后的小芯片可形成貨架產(chǎn)品,便于快速靈活的開(kāi)發(fā),降低開(kāi)發(fā)成本與周期的同時(shí),化整為零,極大減少了知識(shí)產(chǎn)權(quán)(Intellectual Property, IP)問(wèn)題。同時(shí),多種芯片的靈活集成可有效提高產(chǎn)品的功能性,利用常規(guī)工藝即可實(shí)現(xiàn)先進(jìn)的集成芯片性能,從而以全新的角度解決先進(jìn)制程技術(shù)局限導(dǎo)致的技術(shù)代際落后問(wèn)題,形成芯粒異質(zhì)集成的差異化競(jìng)爭(zhēng)。

圖4 芯片成本隨工藝節(jié)點(diǎn)微縮遞增

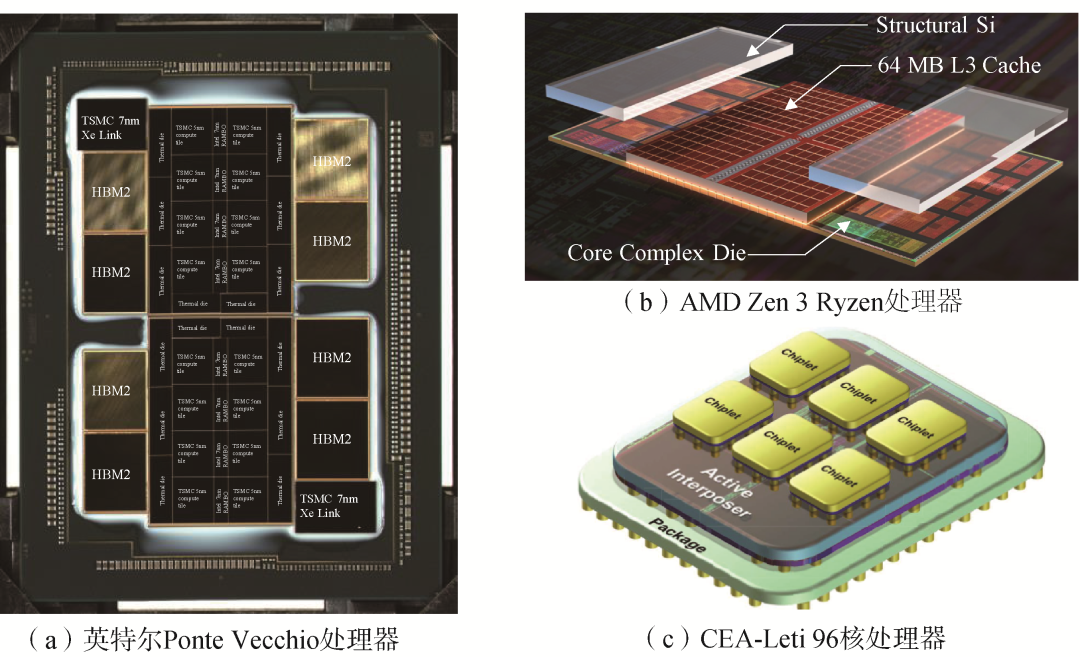

2017年8月美國(guó)國(guó)防部高級(jí)研究計(jì)劃局(DARPA)的“電子復(fù)興計(jì)劃”中,正式發(fā)布了“通用異質(zhì)集成和知識(shí)產(chǎn)權(quán)復(fù)用策略”項(xiàng)目(CHIPS),其目標(biāo)是促成一個(gè)兼容、模塊化、IP復(fù)用的芯粒生態(tài)系統(tǒng),DARPA整合了軍工企業(yè)、半導(dǎo)體企業(yè)、電子設(shè)計(jì)自動(dòng)化(Electronic Design Automation, EDA)企業(yè)以及高校共同推進(jìn)此項(xiàng)目。近年來(lái),美國(guó)英特爾、AMD和法國(guó)原子能委員會(huì)電子與信息技術(shù)實(shí)驗(yàn)室(CEA-Leti)分別推出了Ponte Vecchio處理器、Zen 3 Ryzen處理器和96核處理器等芯粒產(chǎn)品,如圖5所示。其中,Ponte Vecchio處理器集成了47個(gè)功能單元和16個(gè)散熱單元,Zen 3 Ryzen處理器實(shí)現(xiàn)了CPU核和三級(jí)靜態(tài)緩存的三維垂直堆疊,96核處理器集成了6個(gè)相同的計(jì)算芯粒。

圖5 典型芯粒產(chǎn)品

2014年9月華為開(kāi)發(fā)了首款全功能的基于臺(tái)積電16 nm FinFET工藝的網(wǎng)絡(luò)處理器,通過(guò)CoWoS封裝技術(shù)集成了1個(gè)16 nm 32核ARM Cortex-A57、1顆28 nm邏輯芯片和1顆28 nm輸入/輸出(I/O)芯片,相比上一代產(chǎn)品,性能提升了3倍。

2.2 典型先進(jìn)封裝技術(shù)

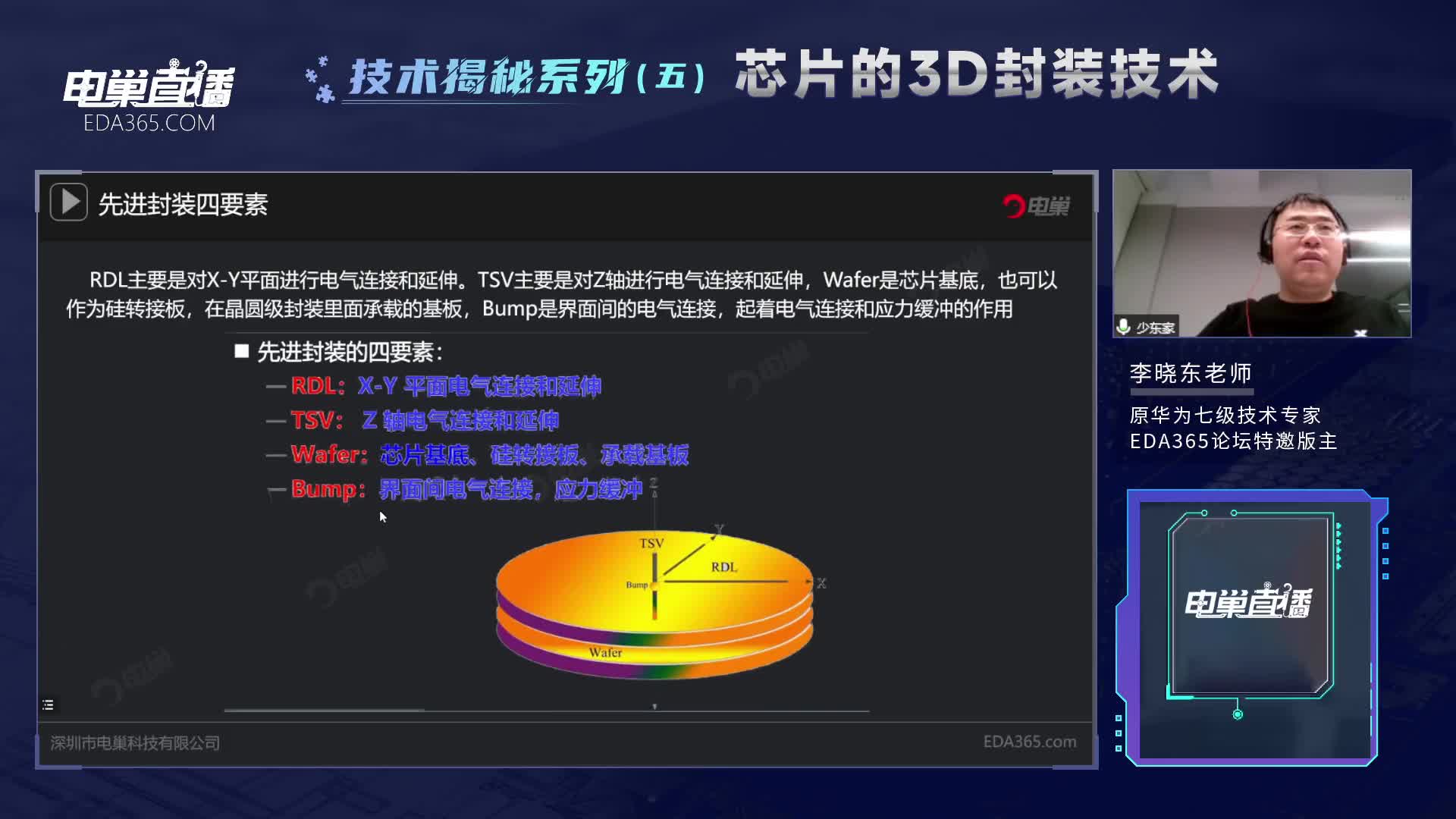

芯粒異質(zhì)集成涉及的典型先進(jìn)封裝技術(shù)包括硅通孔(Through Silicon Via, TSV)、超高密扇出、EMIB以及混合鍵合等。

2.2.1 硅通孔技術(shù)

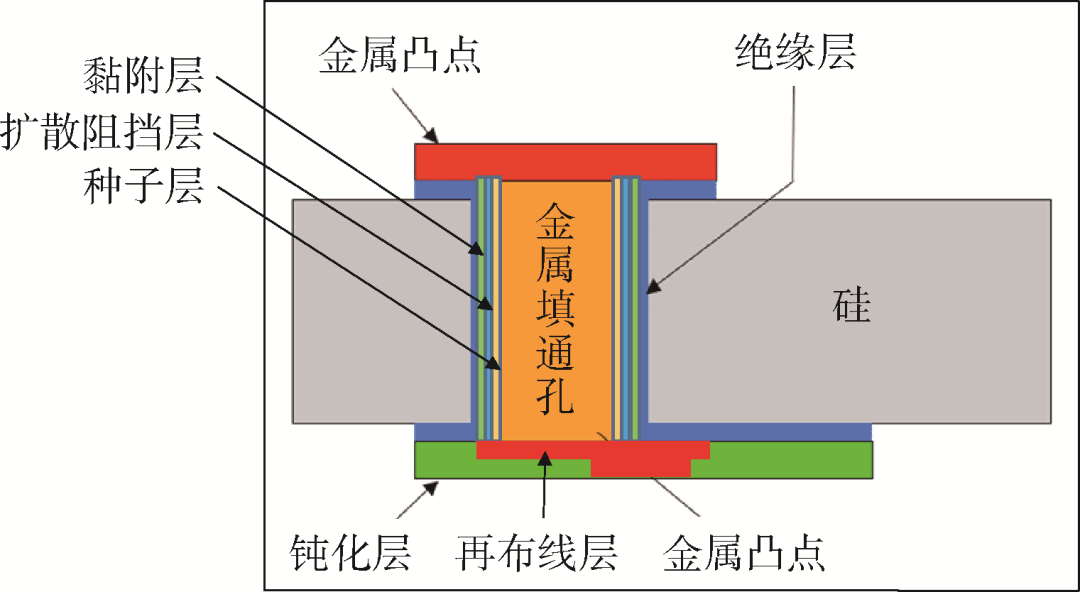

TSV是一種垂直互連技術(shù),它是由威廉·肖克利(William Shockley)于1958年提出的,目前應(yīng)用最廣泛的填銅TSV,由日本超級(jí)先鋒協(xié)會(huì)首創(chuàng)電子技術(shù)聯(lián)盟(1999—2003年)率先實(shí)現(xiàn)。國(guó)際半導(dǎo)體技術(shù)路線(xiàn)藍(lán)圖將TSV定義為連接硅晶圓兩面并與硅襯底和其他通孔絕緣的電互連結(jié)構(gòu),其基本結(jié)構(gòu)示意圖如圖6所示,TSV的尺寸多為10 μm×100 μm和30 μm×200 μm,開(kāi)口率介于0.1%~1%。相比平面互連,TSV可減小互連長(zhǎng)度和信號(hào)延遲,降低寄生電容和電感,實(shí)現(xiàn)芯片間的低功耗和高速通信,增加寬帶和實(shí)現(xiàn)封裝小型化。當(dāng)前TSV主要用于硅轉(zhuǎn)接板、芯片三維堆疊等方面。其中,硅轉(zhuǎn)接板作為芯片和有機(jī)基板的中間層,因與硅芯片的熱膨脹系數(shù)相同,在硅轉(zhuǎn)接板上可集成多顆具有高密度凸點(diǎn)的芯片,如美國(guó)賽靈思的現(xiàn)場(chǎng)可編程門(mén)陣列(Field-Programmable Gate Array, FPGA)產(chǎn)品;可作為HBM和處理器的互連通道,如英偉達(dá)A100產(chǎn)品;可實(shí)現(xiàn)兩顆SoC芯片的拼接,如蘋(píng)果最新發(fā)布的M1 Ultra芯片。硅轉(zhuǎn)接板以是否集成特定功能分為無(wú)源和有源轉(zhuǎn)接板,無(wú)源轉(zhuǎn)接板僅包含金屬互連層,有源轉(zhuǎn)接板包含可集成供電、片內(nèi)網(wǎng)絡(luò)通信等功能。芯片三維堆疊技術(shù)可通過(guò)TSV實(shí)現(xiàn)多芯片的短距離高速通信,HBM就是一種典型的應(yīng)用。

圖6 TSV基本結(jié)構(gòu)示意圖

1)無(wú)源轉(zhuǎn)接板技術(shù)

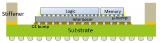

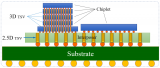

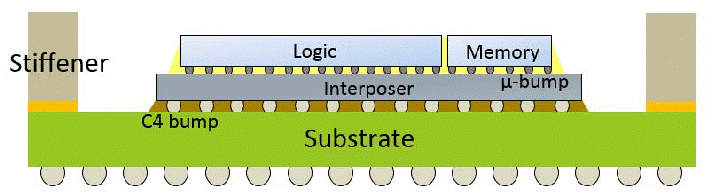

臺(tái)積電的CoWoS是一項(xiàng)2.5D封裝技術(shù),采用的是無(wú)源轉(zhuǎn)接板,其主要工藝特點(diǎn)如下:①通過(guò)微凸點(diǎn)將多顆芯片并排鍵合至硅基無(wú)源轉(zhuǎn)接板晶圓上,形成芯片至晶圓(Chip on Wafer, CoW)裝配體;②減薄晶圓背面以露出TSV;③制備可控塌陷芯片連接(C4)凸點(diǎn);④切割晶圓并將切好的晶圓倒裝焊至封裝基板(Substrate)上,形成最終的CoWoS封裝。

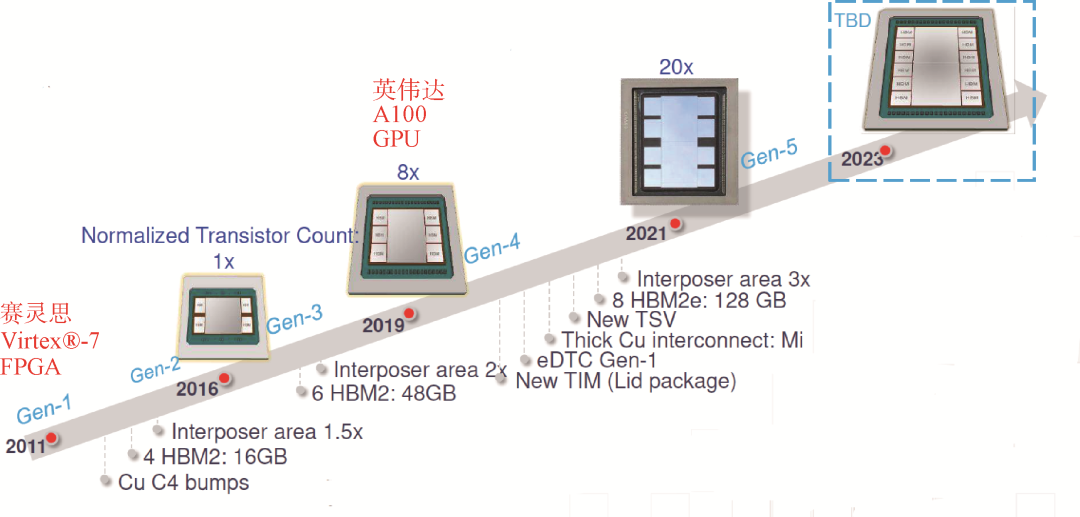

圖7為臺(tái)積電CoWoS封裝技術(shù)路線(xiàn)。自2012年起,該技術(shù)已發(fā)展5代,通過(guò)掩膜版拼接技術(shù),無(wú)源轉(zhuǎn)接板尺寸從接近1個(gè)光罩面積增至3個(gè)光罩面積(2500 mm2)。前兩代為同質(zhì)芯片集成,主要集成硅基邏輯芯片,從第3代起演變?yōu)楫愘|(zhì)芯片集成,主要集成邏輯SoC芯片和HBM陣列。為提高芯片的電源完整性,其開(kāi)始在無(wú)源轉(zhuǎn)接板內(nèi)集成深溝槽電容。

圖7 臺(tái)積電CoWoS封裝技術(shù)路線(xiàn)

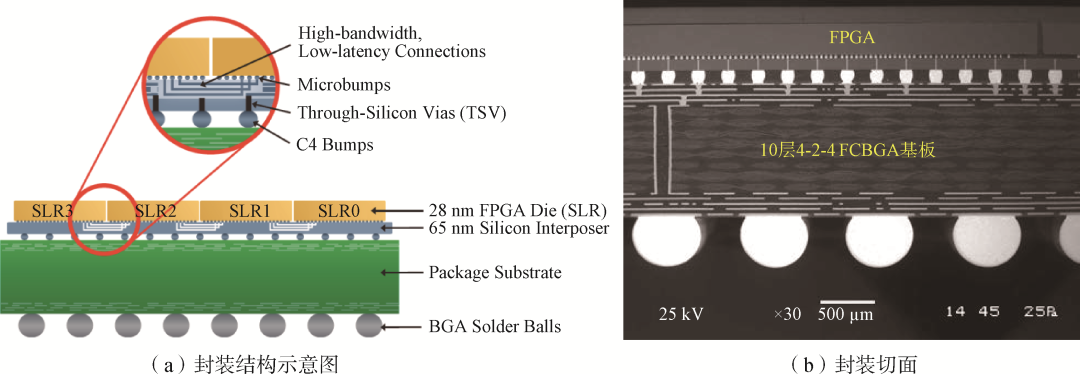

2011年,賽靈思推出了當(dāng)時(shí)世界上最大的FPGA產(chǎn)品。為了解決大芯片良率低的問(wèn)題,該公司采用臺(tái)積電的第1代CoWoS封裝技術(shù)(圖8),將4顆28 nm FPGA小芯片組裝在1個(gè)100 μm厚采用65 nm工藝制造的無(wú)源轉(zhuǎn)接板上,每顆芯粒的尺寸為7 mm×12 mm,硅轉(zhuǎn)接板尺寸為25 mm×31 mm,接近1個(gè)光罩面積,基板為10層FCBGA基板,尺寸為42.5 mm×42.5 mm。

圖8 賽靈思FPGA CoWoS封裝

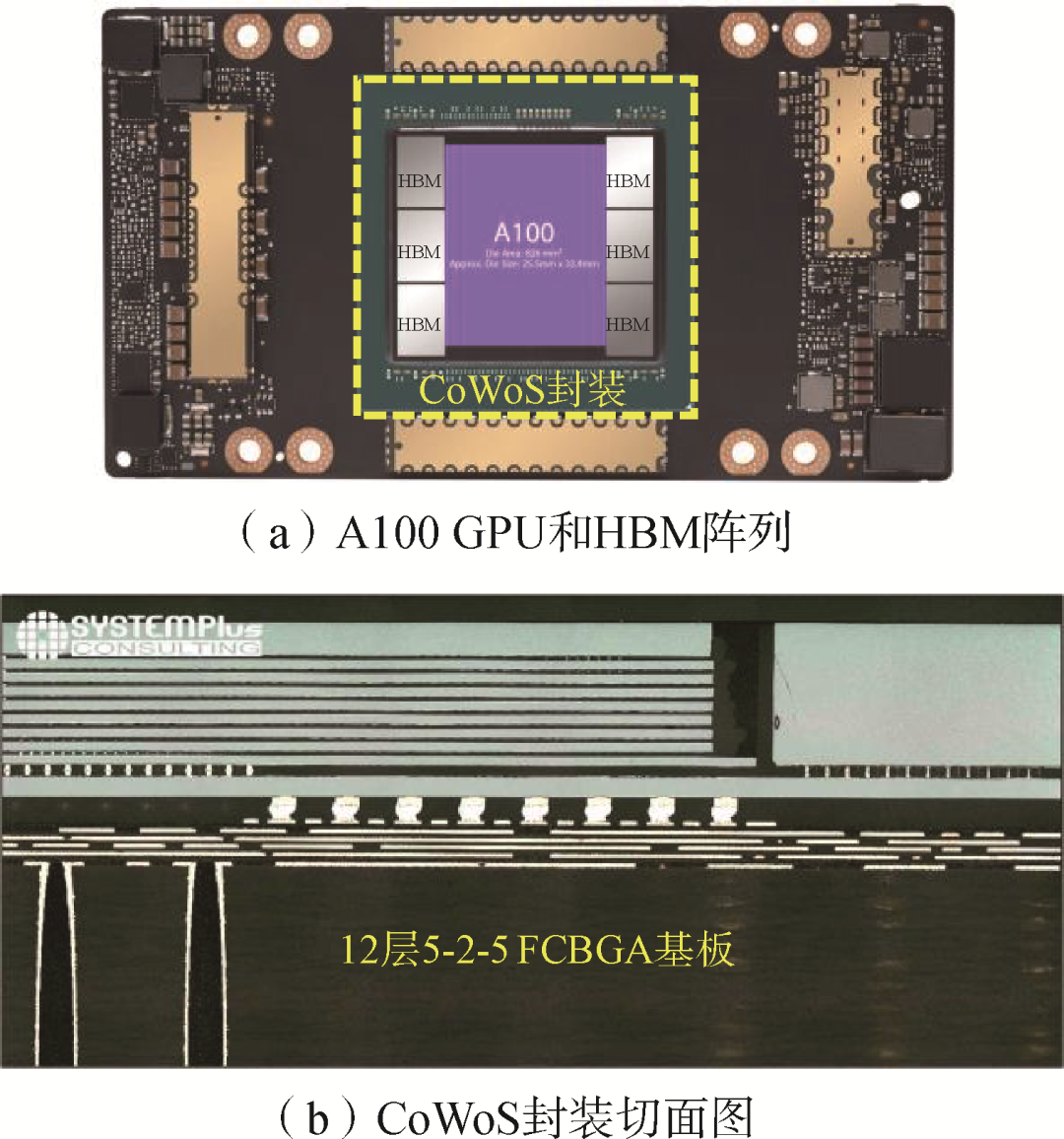

2020年,英偉達(dá)采用臺(tái)積電第4代CoWoS技術(shù)封裝了其A100 GPU系列產(chǎn)品(圖9(a)),將1顆英偉達(dá)A100 GPU芯片和6個(gè)三星電子的HBM2集成在一個(gè)1700 mm2的無(wú)源轉(zhuǎn)接板上,每個(gè)HBM2集成1顆邏輯芯片和8個(gè)動(dòng)態(tài)隨機(jī)存取存儲(chǔ)器(DRAM),基板為12層倒裝芯片球柵格陣列(Flip-Chip Ball Grid Array, FCBGA)基板(圖9(b)),尺寸為55 mm×55 mm。

圖9 英偉達(dá)A100 GPU CoWoS封裝

2)有源轉(zhuǎn)接板技術(shù)

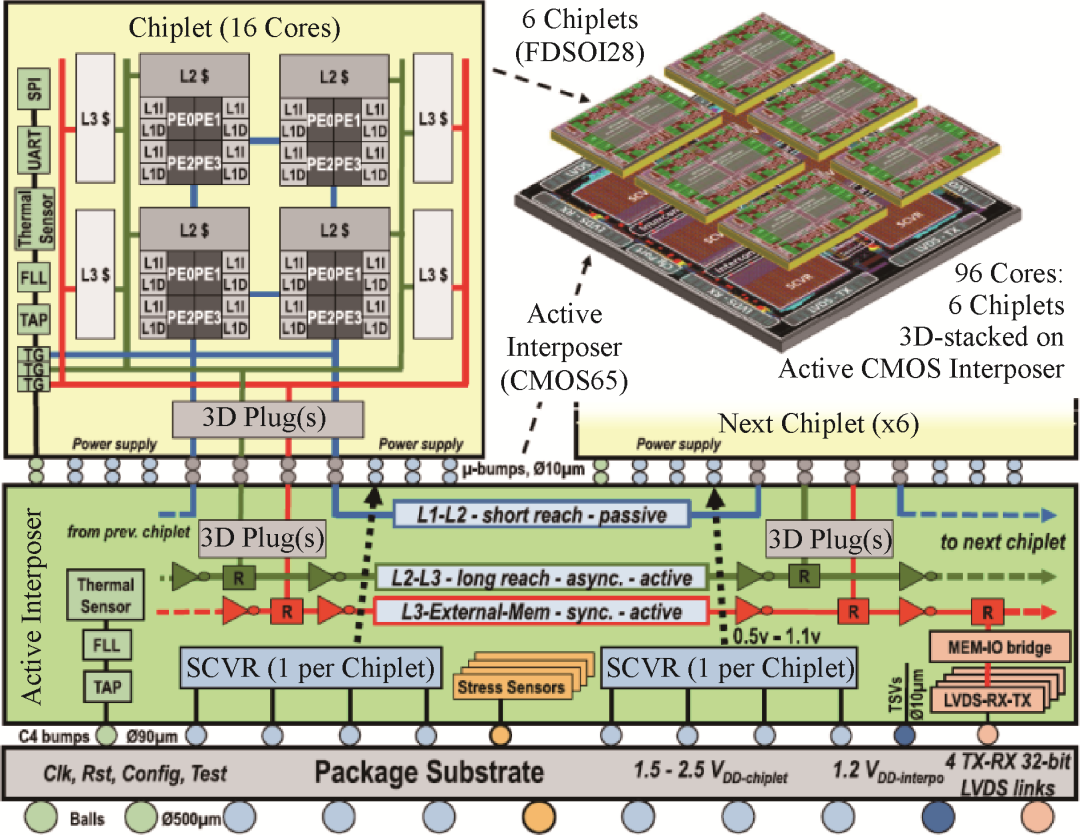

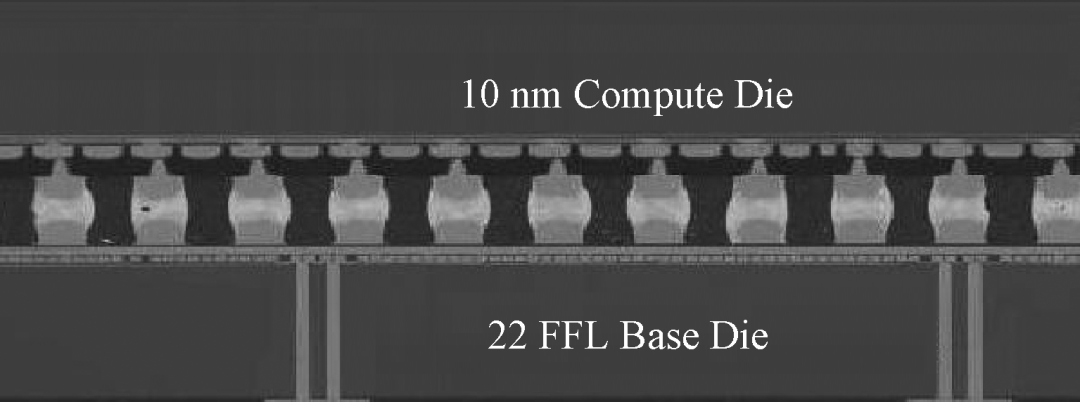

有源轉(zhuǎn)接板是無(wú)源轉(zhuǎn)接板的技術(shù)延伸,在無(wú)源轉(zhuǎn)接板內(nèi)部集成一些功能單元。法國(guó)CEA-Leti開(kāi)發(fā)了一款基于65 nm CMOS工藝的有源轉(zhuǎn)接板,面積約200 mm2,擁有1500萬(wàn)個(gè)晶體管,7層金屬,集成了可近距離直接給芯片供電的開(kāi)關(guān)式電容電壓調(diào)節(jié)器(Switching Capacitor Voltage Regulator, SCVR)、片間通信的分布式片上網(wǎng)絡(luò)、片外通信的系統(tǒng)I/O以及可測(cè)性設(shè)計(jì)(Design For Test, DFT)等功能。采用20 μm間距的微凸點(diǎn),將6個(gè)基于28 nm全耗盡型絕緣體上硅(Fully Depleted Silicon-On-Insulator, FDSOI)工藝的計(jì)算芯粒和一個(gè)基于65 nm CMOS工藝的有源轉(zhuǎn)接板面對(duì)面熱壓鍵合在一起,每顆芯粒的面積為22.4 mm2,擁有3.95億個(gè)晶體管,16核,集成后總共有96核,實(shí)現(xiàn)了220 GOPS的系統(tǒng)算力,電壓轉(zhuǎn)換效率為82%,芯片間互連帶寬密度為3 Tb/(s·mm-2),能效為0.59 pJ/b(圖10)。英特爾開(kāi)發(fā)了一款基于22 nm工藝的有源轉(zhuǎn)接板,包含11層金屬和TSV,TSV與頂部金屬層相鄰,面積為90.85 mm2,集成了供電、PCIe Gen3、USB Type C等功能。通過(guò)Foveros技術(shù)將基于10 nm FinFET先進(jìn)工藝的計(jì)算芯片和22 nm成熟工藝的有源轉(zhuǎn)接板面對(duì)面連接在一起,如圖11所示。其中,計(jì)算芯片有13層金屬,面積為82.5 mm2,融合了混合CPU架構(gòu)、圖像等功能。

圖10 CEA-Leti 96核處理器集成技術(shù)

圖11 英特爾Foveros技術(shù)

3)HBM技術(shù)

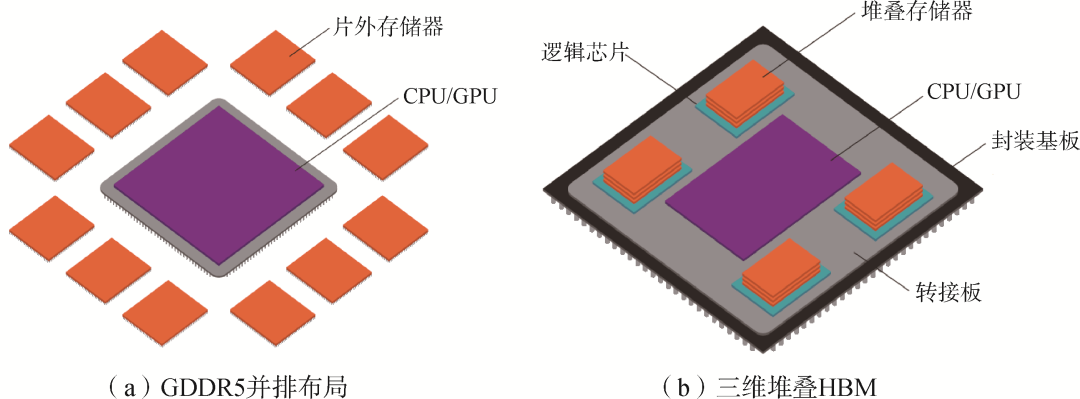

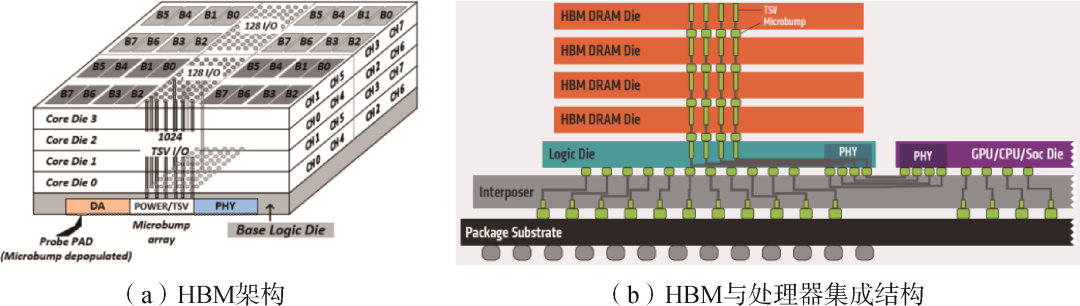

如前所述,存儲(chǔ)器的“存儲(chǔ)墻”限制了計(jì)算芯片性能的發(fā)揮,第5版圖形用雙倍數(shù)據(jù)傳輸率存儲(chǔ)器(GDDR5)的帶寬極限為32 GB/s,由邏輯芯片和多層DRAM堆疊而成的HBM技術(shù)突破了帶寬瓶頸,HBM1和HBM2的帶寬分別為128 GB/s和256 GB/s,未來(lái)HBM3可突破1.075 TB/s。當(dāng)片外存儲(chǔ)從并排布局圖形用雙倍數(shù)據(jù)傳輸率(Graphics Double Data Rate, GDDR)存儲(chǔ)器轉(zhuǎn)為三維堆疊HBM,容量為1 GB時(shí),HBM模組占用面積減少94%,如圖12(a)和圖12(b)所示。第1代HBM的架構(gòu)如圖13(a)所示,由邏輯芯片和4層DRAM堆疊在一起,每個(gè)HBM有8個(gè)通道,每個(gè)通道有128個(gè)I/O,因此每個(gè)HBM有1024個(gè)I/O,即1024個(gè)TSV,位于HBM的中間區(qū)域。存儲(chǔ)器和處理器通過(guò)無(wú)源轉(zhuǎn)接板上的再布線(xiàn)層(Re-Distributed Layer, RDL)將HBM邏輯芯片的端口物理層(Port Physical Layer, PHY)與處理器的PHY連接在一起,如圖13(b)所示。

圖12 片外存儲(chǔ)從并排布局轉(zhuǎn)為三維堆疊

圖13 HBM架構(gòu)和封裝集成示意圖

2.2.2 超高密度扇出技術(shù)

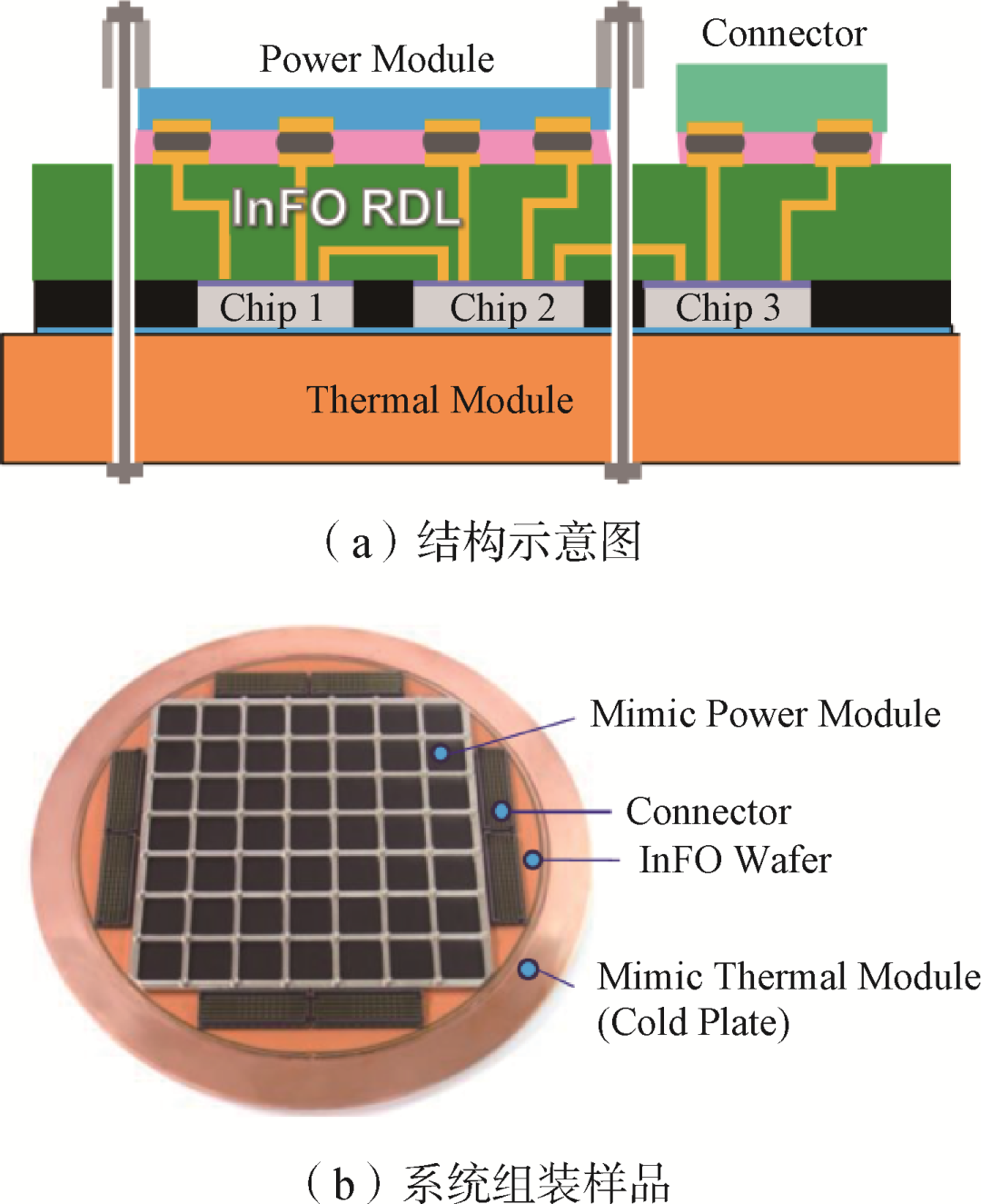

2020年,臺(tái)積電發(fā)布了一種超高密度扇出封裝技術(shù),即集成扇出型晶圓上系統(tǒng)(InFO_SoW),如圖14所示,通過(guò)超高密度扇出封裝技術(shù)將多顆好的晶粒(Known Good Die, KGD)、供電、散熱模塊和連接器緊湊地集成在晶圓上,包含6層RDL,前3層線(xiàn)寬/線(xiàn)距為5/5 μm,用于細(xì)線(xiàn)路芯片間互連;后3層線(xiàn)寬/線(xiàn)距為15/20 μm,用于供電和連接器互連。相比印制電路板(Printed Circuit Board, PCB)級(jí)多芯片模塊,InFO_SoW具有高帶寬、低延遲和低功耗的特點(diǎn)。

圖14 臺(tái)積電InFO_SoW技術(shù)

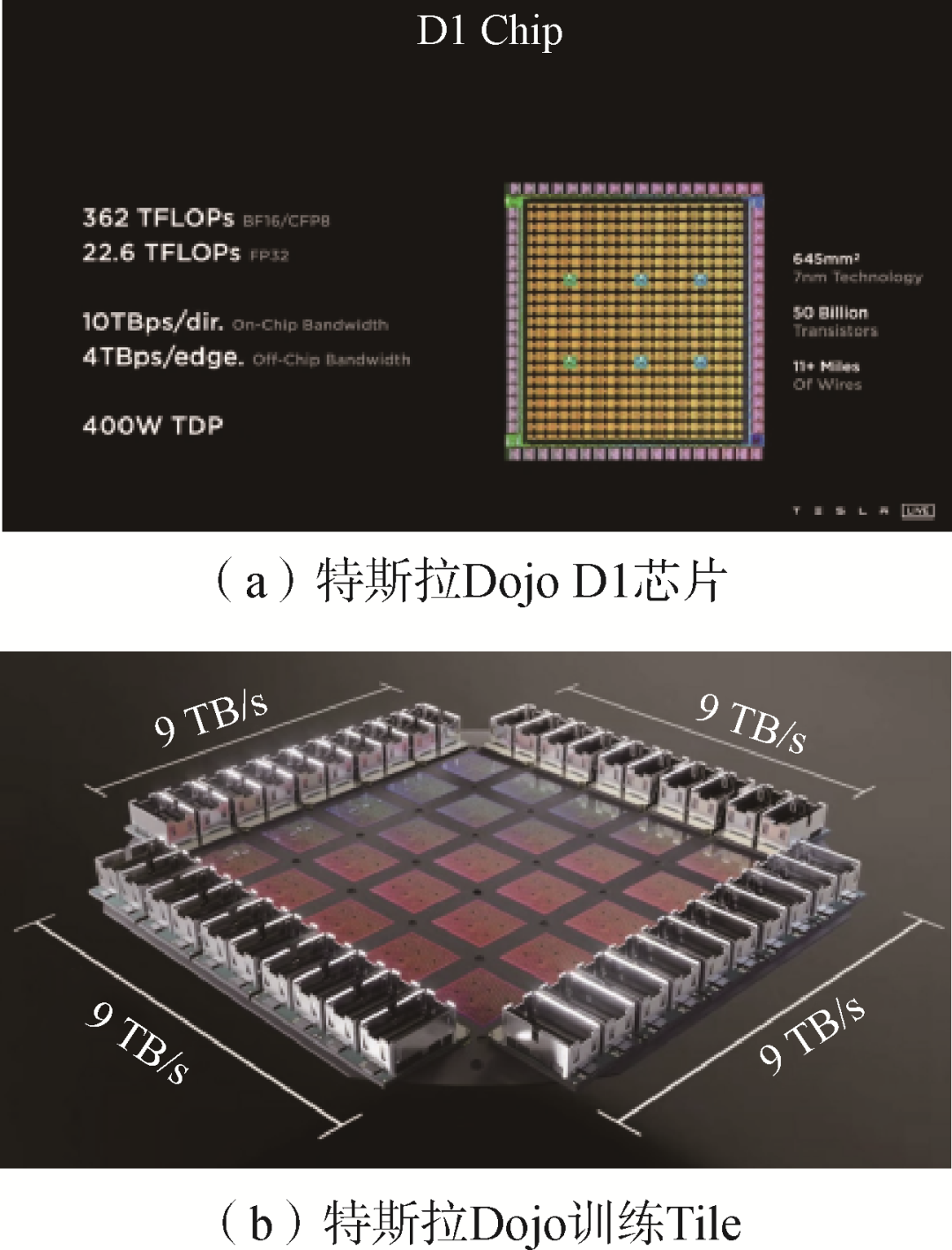

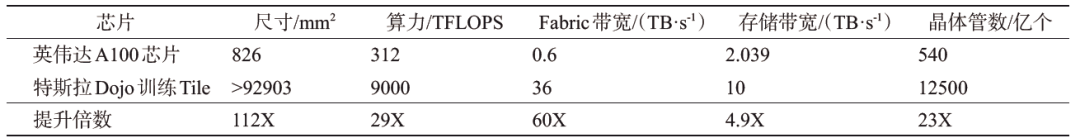

2021年8月19日,特斯拉人工智能(Artificial Intelligence, AI)日推出了其自研的面向AI專(zhuān)用領(lǐng)域的Dojo D1芯片,如圖15(a)所示。D1芯片采用臺(tái)積電7 nm工藝,面積為645 mm2,晶體管數(shù)量達(dá)500億個(gè),1 mm2面積上的晶體管數(shù)量已超過(guò)英偉達(dá)A100芯片,包含354個(gè)訓(xùn)練節(jié)點(diǎn),BF16/CFP8的峰值算力高達(dá)362 TFLOPS,TDP為400 W。通過(guò)臺(tái)積電InFO_SoW封裝技術(shù)將25顆D1芯片集成在一起,再將供電、散熱、連接器等模塊集成進(jìn)來(lái),形成1個(gè)Dojo訓(xùn)練Tile,BF16/CFP8算力高達(dá)9.1 PFLOPS,如圖15(b)所示。將120個(gè)Dojo訓(xùn)練Tile組裝成了ExaPOD超級(jí)計(jì)算機(jī),ExaPOD含有3000顆D1芯片,106.2萬(wàn)個(gè)訓(xùn)練節(jié)點(diǎn),BF16/CFP8算力可以達(dá)到1.1 EFLOPS。表1對(duì)比了英偉達(dá)A100芯片與特斯拉Dojo訓(xùn)練Tile的主要性能指標(biāo)。從表1中可以看出,晶圓級(jí)片上大規(guī)模集成可大幅提升系統(tǒng)算力和帶寬,是提升系統(tǒng)能力的一種重要途徑。

圖15 特斯拉Dojo D1芯片晶圓級(jí)片上大規(guī)模集成

表1 英偉達(dá)A100芯片與特斯拉Dojo訓(xùn)練Tile主要性能指標(biāo)對(duì)比

2.2.3 EMIB技術(shù)

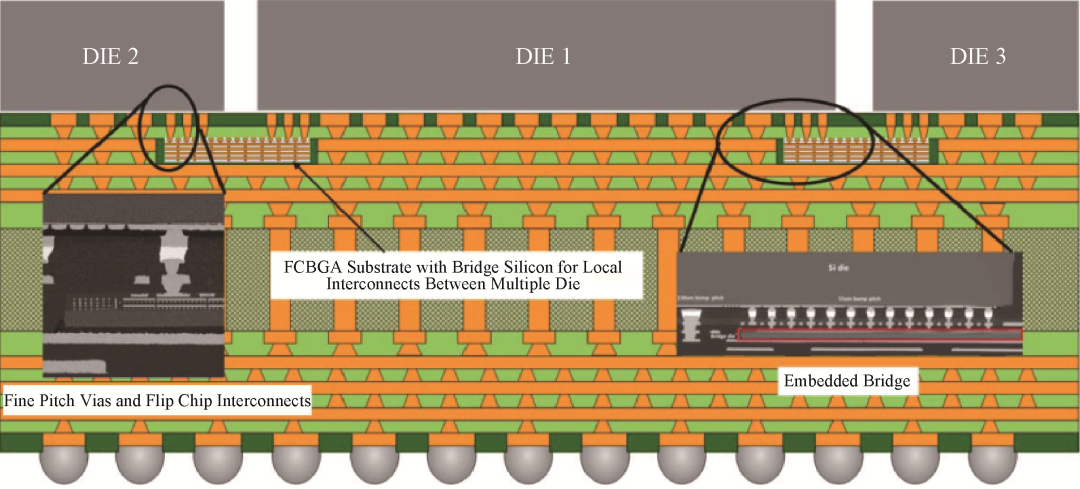

EMIB技術(shù)最早由英特爾的Mahajan和Sane于2008年提出,后又經(jīng)Braunisch和Starkston等改進(jìn),近年來(lái)已發(fā)展成為英特爾最具代表性的先進(jìn)封裝技術(shù)之一,已用于其多款FPGA產(chǎn)品,如Agilex FPGA和Direct RF FPGA。它是在有機(jī)基板中埋入若干超薄的(厚度一般小于100 μm)、高密度的硅橋,實(shí)現(xiàn)兩兩芯片間的互連,如圖16所示。目前英特爾可量產(chǎn)的硅橋尺寸為2 mm×2 mm~12 mm×12 mm,包含4層RDL和1層焊盤(pán),線(xiàn)寬/線(xiàn)距為1 μm/1 μm。EMIB可提供芯片間局部高密度互連,可靈活地放置在基板任意需要互連的地方,不限制芯片的集成數(shù)量與位置,不影響基板上其他線(xiàn)路的布局布線(xiàn)。

圖16 英特爾EMIB互連技術(shù)2.2.4 混合鍵合技術(shù)

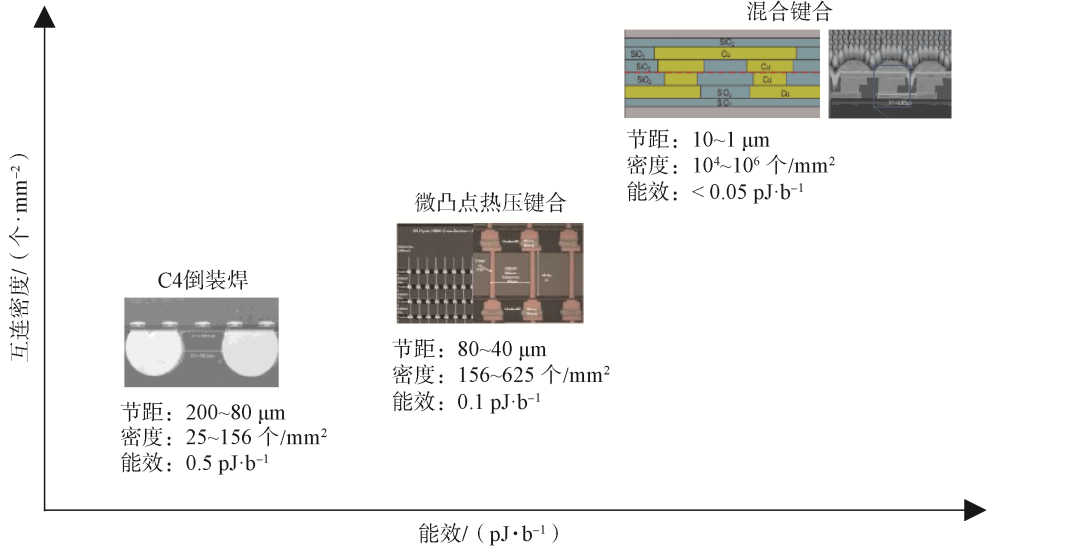

圖17為鍵合技術(shù)的演進(jìn),其中混合鍵合是通過(guò)銅—銅金屬鍵合和二氧化硅—二氧化硅介質(zhì)層鍵合實(shí)現(xiàn)無(wú)凸點(diǎn)永久鍵合的芯片三維堆疊高密度互連技術(shù),可實(shí)現(xiàn)極小間距的芯片焊盤(pán)互連,每平方毫米可互連的芯片焊盤(pán)數(shù)為104~106個(gè),可以提供更高的互連密度、更小更簡(jiǎn)單的電路、更大的帶寬、更小的電容和更低的功耗。與傳統(tǒng)C4焊點(diǎn)和微凸點(diǎn)連接技術(shù)相比,混合鍵合技術(shù)的主要優(yōu)點(diǎn)有:①實(shí)現(xiàn)芯片之間無(wú)凸點(diǎn)互連,微凸點(diǎn)的取消將進(jìn)一步降低芯片之間通道的寄生電感和信號(hào)延時(shí);②實(shí)現(xiàn)芯片之間超細(xì)間距的互連,比微凸點(diǎn)提高10倍以上,超細(xì)間距的互連將增加布線(xiàn)有效使用面積,大幅增加通道數(shù)量,實(shí)現(xiàn)數(shù)據(jù)處理串并轉(zhuǎn)換,簡(jiǎn)化I/O端口電路,增大帶寬;③實(shí)現(xiàn)超薄芯片制備,通過(guò)芯片減薄可使芯片厚度和重量大幅降低,并且可進(jìn)一步提升系統(tǒng)中芯片的互連帶寬;④實(shí)現(xiàn)鍵合可靠性的提高,銅—銅觸點(diǎn)間以分子尺度融合,取消了焊料連接,二氧化硅—二氧化硅以分子共價(jià)鍵鍵合取消了底填材料,極大提高了界面鍵合強(qiáng)度,增強(qiáng)了芯片的環(huán)境適應(yīng)性。

圖17 鍵合技術(shù)的演進(jìn)

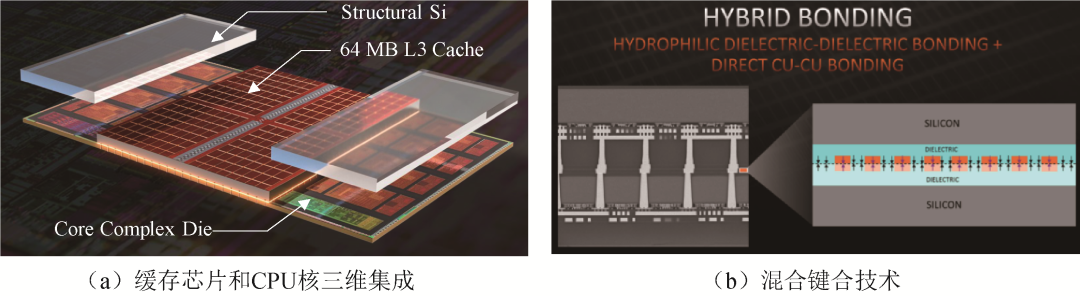

美國(guó)AMD通過(guò)混合鍵合技術(shù)將兩個(gè)64 MB三級(jí)靜態(tài)緩存芯片和1個(gè)含TSV的8核CPU垂直鍵合在一起,實(shí)現(xiàn)了3D芯粒,如圖18所示,其混合鍵合的間距為9 μm,互連密度約12345個(gè)/mm2,相比間距為36 μm的微凸點(diǎn),互連密度提升大于15倍,互連能效提升大于3倍。

圖18 AMD 3D芯粒技術(shù)

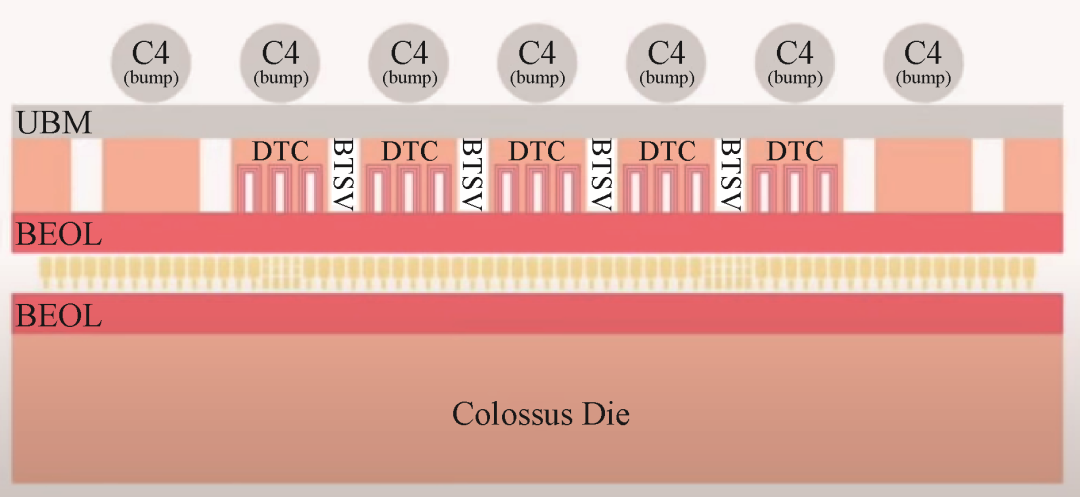

2022年3月,英國(guó)AI芯片公司Graphcore發(fā)布了一款智能處理單元(Intelligent Processing Unit, IPU)產(chǎn)品Bow,其結(jié)構(gòu)示意圖如圖19所示,采用臺(tái)積電SoIC-WoW(Wafer on Wafer,晶圓對(duì)晶圓)混合鍵合技術(shù),將7 nm的處理器晶圓和供電晶圓堆疊在一起。其中,供電晶圓上含有深溝槽電容,用來(lái)存儲(chǔ)電荷,背面TSV允許互連至晶圓內(nèi)層;較上一代相同7 nm制程,采用3D WoW封裝技術(shù)后,性能提升40%,功耗降低16%。

圖19 臺(tái)積電SoIC-WoW混合鍵合技術(shù)

(來(lái)源:Graphcore公司)

03 中國(guó)大陸先進(jìn)封裝技術(shù)發(fā)展現(xiàn)狀

和存在的問(wèn)題

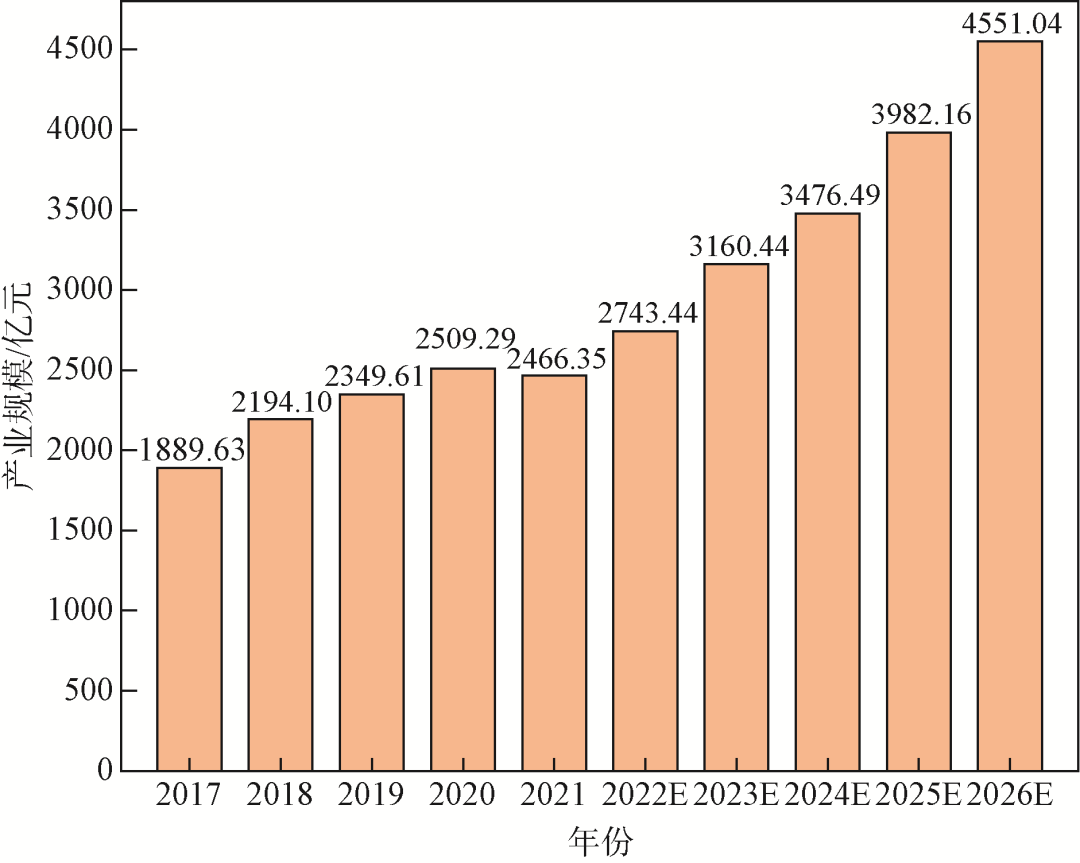

中國(guó)大陸封裝測(cè)試(簡(jiǎn)稱(chēng)封測(cè))企業(yè)主要集中于長(zhǎng)江三角洲地區(qū),根據(jù)中國(guó)半導(dǎo)體行業(yè)協(xié)會(huì)統(tǒng)計(jì),2020年中國(guó)大陸封測(cè)產(chǎn)品銷(xiāo)售額達(dá)到2509.29億元,江蘇、上海、浙江3個(gè)省份2020年封測(cè)產(chǎn)品銷(xiāo)售額合計(jì)達(dá)到1838.3億元,占2020年中國(guó)大陸封測(cè)產(chǎn)品銷(xiāo)售額的73.3%。2021年中國(guó)大陸封測(cè)產(chǎn)品銷(xiāo)售額降至2466.35億元,同比下降1.7%,2022年將再次增長(zhǎng),預(yù)計(jì)增至2743.44億元,同比增長(zhǎng)11.2%,預(yù)計(jì)2026年中國(guó)大陸集成電路封測(cè)市場(chǎng)規(guī)模將達(dá)4551.04億元,如圖20所示。包括BGA、CSP、WLP、FO、SiP和2.5D/3D等在內(nèi)的先進(jìn)封裝業(yè)務(wù)占比也逐年上升,2021年中國(guó)大陸規(guī)模以上的集成電路封測(cè)企業(yè)先進(jìn)封裝產(chǎn)品銷(xiāo)售額占整個(gè)封裝產(chǎn)業(yè)的35%左右,在保持增長(zhǎng)勢(shì)頭的同時(shí),與國(guó)際大廠(chǎng)仍有不小的差距。

圖20 2017—2026年中國(guó)大陸封測(cè)市場(chǎng)規(guī)模及預(yù)測(cè)

(來(lái)源:中國(guó)半導(dǎo)體行業(yè)協(xié)會(huì))

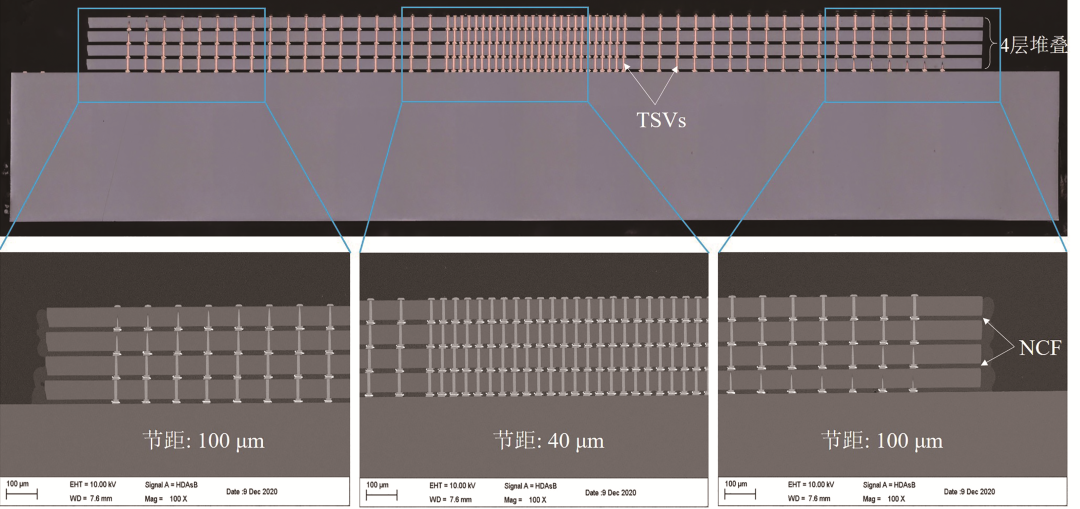

目前中國(guó)大陸產(chǎn)業(yè)領(lǐng)頭羊多注重基于解決集成電路工藝瓶頸的產(chǎn)業(yè)化,對(duì)于核心高端產(chǎn)品技術(shù)以及面向多功能與集成度的前瞻性技術(shù)缺乏相關(guān)技術(shù)布局。以長(zhǎng)電科技、通富微電、華天科技、華進(jìn)半導(dǎo)體為代表的封裝企業(yè),在WLP、SiP及三維堆疊等方向?qū)崿F(xiàn)部分產(chǎn)品量產(chǎn)與應(yīng)用。開(kāi)展先進(jìn)封裝主要的研究機(jī)構(gòu),如中國(guó)科學(xué)院微電子研究所、中國(guó)科學(xué)院上海微系統(tǒng)與信息技術(shù)研究所、清華大學(xué)、北京大學(xué)、武漢大學(xué)、華中科技大學(xué)、北京理工大學(xué)、桂林電子科技大學(xué)、中國(guó)電子科技集團(tuán)有限公司、中國(guó)航天科技集團(tuán)有限公司等單位已形成了較強(qiáng)的研發(fā)力量,在晶圓級(jí)/板級(jí)扇出型封裝、異質(zhì)芯片2.5D集成、Si基芯片3D疊層封裝等技術(shù)方面,經(jīng)過(guò)長(zhǎng)期的實(shí)踐摸索,形成的技術(shù)積累縮短了與國(guó)外先進(jìn)封裝技術(shù)的差距。圖21為中國(guó)科學(xué)院微電子研究所聯(lián)合華進(jìn)半導(dǎo)體開(kāi)發(fā)的三維堆疊芯片封裝。

圖21 中國(guó)科學(xué)院微電子研究所聯(lián)合華進(jìn)半導(dǎo)體開(kāi)發(fā)的三維堆疊芯片封裝

與世界先進(jìn)水平相比,中國(guó)大陸先進(jìn)封裝技術(shù)存在以下問(wèn)題。

(1)目前中國(guó)大陸封裝領(lǐng)域總體仍以傳統(tǒng)的中低端封裝為主,從先進(jìn)封裝營(yíng)收占總營(yíng)收的比例和高密度集成等先進(jìn)封裝技術(shù)發(fā)展方面,僅FC技術(shù)相對(duì)成熟,而以TSV為代表的2.5D/3D封裝和以扇出型封裝為代表的高密度扇出型技術(shù),與國(guó)外公司的技術(shù)差距明顯,在先進(jìn)封裝全球產(chǎn)業(yè)鏈中仍未占據(jù)重要位置,中國(guó)大陸總體先進(jìn)封裝技術(shù)水平與國(guó)際領(lǐng)先水平還有一定的差距。未來(lái)對(duì)高端先進(jìn)封裝技術(shù)的需求將越來(lái)越多,因此實(shí)現(xiàn)高端先進(jìn)封裝技術(shù)突破越來(lái)越重要。

(2)先進(jìn)封裝關(guān)鍵裝備及材料尚未實(shí)現(xiàn)自主可控。支撐中國(guó)大陸封裝產(chǎn)業(yè)鏈發(fā)展的整體基礎(chǔ)技術(shù)水平不高,先進(jìn)封測(cè)技術(shù)所需的關(guān)鍵封裝、測(cè)試設(shè)備和材料主要依賴(lài)進(jìn)口,難以滿(mǎn)足市場(chǎng)需求。

(3)先進(jìn)封裝設(shè)計(jì)主要依賴(lài)境外商用EDA工具,中國(guó)大陸封裝級(jí)EDA還處于起步階段,與境外主流EDA廠(chǎng)商差距比較明顯,市場(chǎng)占有率較低,用戶(hù)反饋和迭代次數(shù)少,導(dǎo)致中國(guó)大陸EDA工具發(fā)展緩慢。

04 中國(guó)大陸先進(jìn)封裝技術(shù)發(fā)展建議

針對(duì)中國(guó)大陸先進(jìn)封裝領(lǐng)域的薄弱環(huán)節(jié),重點(diǎn)攻關(guān)核心封裝工藝、關(guān)鍵封裝裝備及材料痛點(diǎn),加快布局EDA工具,推進(jìn)中國(guó)大陸集成電路封裝領(lǐng)域自主可控高質(zhì)量發(fā)展。

(1)先進(jìn)封裝工藝。基于明確的產(chǎn)業(yè)應(yīng)用需求,開(kāi)發(fā)合適的封裝工藝,并重點(diǎn)攻關(guān)核心封裝工藝,對(duì)于需在前道平臺(tái)上加工的部分工藝,需明確前道和后道工藝分工,進(jìn)行前、后道協(xié)同設(shè)計(jì)和迭代優(yōu)化。

(2)核心封裝材料。首先形成良好的材料—封裝—應(yīng)用產(chǎn)業(yè)鏈,基于產(chǎn)業(yè)應(yīng)用需求,對(duì)標(biāo)國(guó)外進(jìn)口材料,材料廠(chǎng)商開(kāi)發(fā)相應(yīng)的封裝材料,并測(cè)試評(píng)估和比較材料性能。然后,在國(guó)內(nèi)先進(jìn)封裝平臺(tái)上進(jìn)行多輪迭代使用,最終實(shí)現(xiàn)進(jìn)口材料國(guó)產(chǎn)化替代。

(3)關(guān)鍵封裝裝備。隨著應(yīng)用需求的不斷遞進(jìn),先進(jìn)封裝技術(shù)不斷升級(jí),封裝廠(chǎng)商需向裝備廠(chǎng)商提出明確的需求,并與設(shè)備廠(chǎng)商協(xié)同開(kāi)發(fā)關(guān)鍵封裝裝備。然后,在國(guó)內(nèi)先進(jìn)封裝平臺(tái)上,加快國(guó)產(chǎn)裝備的試用和迭代。

(4)EDA工具。發(fā)展國(guó)產(chǎn)EDA工具是一個(gè)漫長(zhǎng)的過(guò)程,需要用戶(hù)不斷反饋和軟件迭代。發(fā)展國(guó)產(chǎn)EDA工具不僅僅局限于EDA算法和點(diǎn)工具研究,還需做好規(guī)劃,具有集成能力,最終形成自主可控的EDA平臺(tái)。

(5)產(chǎn)業(yè)鏈。預(yù)防美國(guó)針對(duì)中國(guó)大陸集成電路高端技術(shù)的進(jìn)一步出口管制,加快發(fā)展中國(guó)大陸集成電路封裝領(lǐng)域創(chuàng)新聯(lián)合體,強(qiáng)化建設(shè)先進(jìn)封裝聯(lián)合攻關(guān)公共平臺(tái),完善國(guó)內(nèi)芯粒異質(zhì)集成產(chǎn)業(yè)鏈。

05 結(jié)束語(yǔ)

近年來(lái),以高性能計(jì)算、人工智能和5G通信為代表的需求牽引,加速了集成電路的發(fā)展,以尺寸微縮為主線(xiàn)的摩爾定律發(fā)展放緩,22 nm工藝節(jié)點(diǎn)以下芯片的設(shè)計(jì)和制造成本呈指數(shù)級(jí)增加,芯片尺寸受限于光刻機(jī)的最大曝光面積,單一襯底上可集成的功能有限,SoC單片向芯粒異質(zhì)集成“改道”是集成電路發(fā)展的重要趨勢(shì)。依據(jù)功能劃分,將原先的大尺寸SoC芯片拆成芯粒,主要功能采用先進(jìn)制程,次要功能采用成熟制程,再通過(guò)先進(jìn)封裝技術(shù),實(shí)現(xiàn)成本較低、性能接近的集成電路產(chǎn)品,其中先進(jìn)封裝技術(shù)不再局限于后道工藝,一些關(guān)鍵工藝需在前道平臺(tái)上進(jìn)行,因此需進(jìn)行前后道協(xié)同設(shè)計(jì)開(kāi)發(fā)。中國(guó)需快速布局芯粒領(lǐng)域的技術(shù)研發(fā),通過(guò)路徑創(chuàng)新,降低中國(guó)大陸集成電路發(fā)展同集成電路既有全球體系直接對(duì)沖的風(fēng)險(xiǎn),實(shí)現(xiàn)靈活、高效、系統(tǒng)級(jí)的新型集成電路發(fā)展模式,推動(dòng)集成電路的創(chuàng)新發(fā)展與自主可控。

審核編輯:湯梓紅

?

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論