半導(dǎo)體器件有許多封裝形式,按封裝的外形、尺寸、結(jié)構(gòu)分類可分為引腳插入型、表面貼裝型和高級封裝三類。從DIP、SOP、QFP、PGA、BGA到CSP再到SIP,技術(shù)指標(biāo)一代比一代先進(jìn)。總體說來,半導(dǎo)體封裝經(jīng)歷了三次重大革新:第一次是在20世紀(jì)80年代從引腳插入式封裝到表面貼片封裝,它極大地提高了印刷電路板上的組裝密度;第二次是在20世紀(jì)90年代球型矩陣封裝的出現(xiàn),滿足了市場對高引腳的需求,改善了半導(dǎo)體器件的性能;芯片級封裝、系統(tǒng)封裝等是現(xiàn)在第三次革新的產(chǎn)物,其目的就是將封裝面積減到最小。半導(dǎo)體產(chǎn)品在由二維向三維發(fā)展,從技術(shù)發(fā)展方向半導(dǎo)體產(chǎn)品出現(xiàn)了系統(tǒng)級封裝(SiP)等新的封裝方式,從技術(shù)實(shí)現(xiàn)方法出現(xiàn)了倒裝(FlipChip),凸塊(Bumping),晶圓級封裝(Waferlevelpackage),2.5D封裝(interposer,RDL等),3D封裝(TSV)等先進(jìn)封裝技術(shù)。

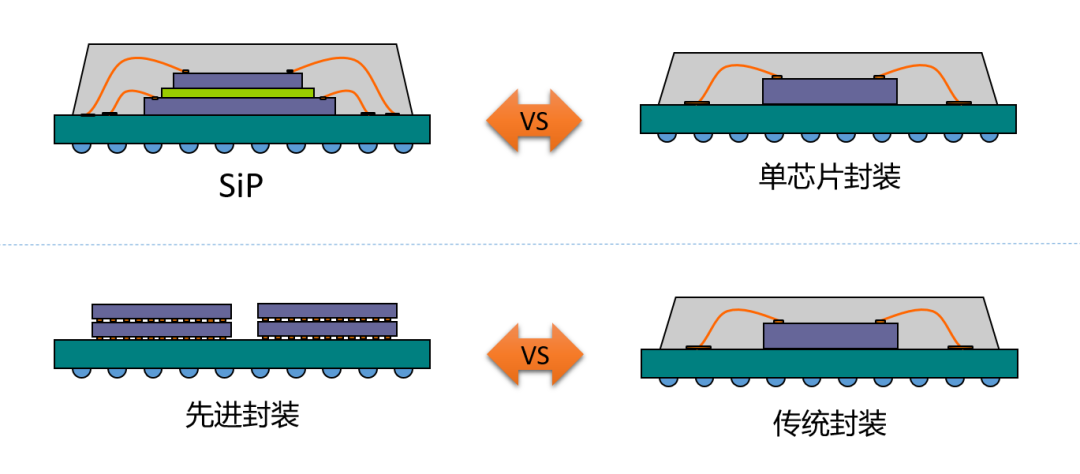

傳統(tǒng)封裝vs先進(jìn)封裝

傳統(tǒng)封裝概念從最初的三極管直插時(shí)期后開始產(chǎn)生。傳統(tǒng)封裝過程如下:將晶圓切割為晶粒(Die)后,使晶粒貼合到相應(yīng)的基板架的小島(LeadframePad)上,再利用導(dǎo)線將晶片的接合焊盤與基板的引腳相連(WireBond),實(shí)現(xiàn)電氣連接,最后用外殼加以保護(hù)(Mold,或Encapsulation)。典型封裝方式有DIP、SOP、TSOP、QFP等。

先進(jìn)封裝主要是指倒裝(FlipChip),凸塊(Bumping),晶圓級封裝(Waferlevelpackage),2.5D封裝(interposer,RDL等),3D封裝(TSV)等封裝技術(shù)。先進(jìn)封裝在誕生之初只有WLP,2.5D封裝和3D封裝幾種選擇,近年來,先進(jìn)封裝的發(fā)展呈爆炸式向各個(gè)方向發(fā)展,而每個(gè)開發(fā)相關(guān)技術(shù)的公司都將自己的技術(shù)獨(dú)立命名注冊商標(biāo),如臺積電的InFO、CoWoS,日月光的FoCoS,Amkor的SLIM、SWIFT等。盡管很多先進(jìn)封裝技術(shù)只有微小的區(qū)別,大量的新名詞和商標(biāo)被注冊,導(dǎo)致行業(yè)中出現(xiàn)大量的不同種類的先進(jìn)封裝,而其誕生通常是由客制化產(chǎn)品的驅(qū)動(dòng)。

先進(jìn)封裝優(yōu)勢

先進(jìn)封裝提高加工效率,提高設(shè)計(jì)效率,減少設(shè)計(jì)成本。

先進(jìn)封裝主要包括倒裝類(FlipChip,Bumping),晶圓級封裝(WLCSP,F(xiàn)OWLP,PLP),2.5D封裝(Interposer)和3D封裝(TSV)等。以晶圓級封裝為例,產(chǎn)品生產(chǎn)以圓片形式批量生產(chǎn),可以利用現(xiàn)有的晶圓制備設(shè)備,封裝設(shè)計(jì)可以與芯片設(shè)計(jì)一次進(jìn)行。這將縮短設(shè)計(jì)和生產(chǎn)周期,降低成本。

先進(jìn)封裝提高封裝效率,降低產(chǎn)品成本。

隨著后摩爾定律時(shí)代的到來,傳統(tǒng)封裝已經(jīng)不再能滿足需求。傳統(tǒng)封裝的封裝效率(裸芯面積/基板面積)較低,存在很大改良的空間。芯片制程受限的情況下,改進(jìn)封裝便是另一條出路。舉例來說,QFP封裝效率最高為30%,那么70%的面積將被浪費(fèi)。DIP、BGA浪費(fèi)的面積會更多。

先進(jìn)封裝以更高效率、更低成本、更好性能為驅(qū)動(dòng)。

先進(jìn)封裝技術(shù)于上世紀(jì)90年代出現(xiàn),通過以點(diǎn)帶線的方式實(shí)現(xiàn)電氣互聯(lián),實(shí)現(xiàn)更高密度的集成,大大減小了對面積的浪費(fèi)。SiP技術(shù)及PoP技術(shù)奠定了先進(jìn)封裝時(shí)代的開局,2D集成技術(shù),如WaferLevelPackaging(WLP,晶圓級封裝),F(xiàn)lip-Chip(倒晶),以及3D封裝技術(shù),ThroughSiliconVia(硅通孔,TSV)等技術(shù)的出現(xiàn)進(jìn)一步縮小芯片間的連接距離,提高元器件的反應(yīng)速度,未來將繼續(xù)推進(jìn)著先進(jìn)封裝發(fā)展的腳步。

先進(jìn)封裝技術(shù)

Flip-Chip & Bumping

FlipChip指的是芯片倒裝,以往的封裝技術(shù)都是將芯片的有源區(qū)面朝上,背對基板和貼后鍵合。而FlipChip則將芯片有源區(qū)面對著基板,通過芯片上呈陣列排列的焊料凸點(diǎn)(Bumping)實(shí)現(xiàn)芯片與襯底的互聯(lián)。硅片直接以倒扣方式安裝到PCB從硅片向四周引出I/O,互聯(lián)長度大大縮短,減小了RC(Resistance-Capacitance)延遲,有效的提高了電性能。

FlipChip的優(yōu)勢主要在于以下幾點(diǎn):小尺寸,功能增強(qiáng)(增加I/O數(shù)量),性能增強(qiáng)(互聯(lián)短),提高了可靠性(倒裝芯片可減少2/3的互聯(lián)引腳數(shù)),提高了散熱能力(芯片背面可以有效進(jìn)行冷卻)。

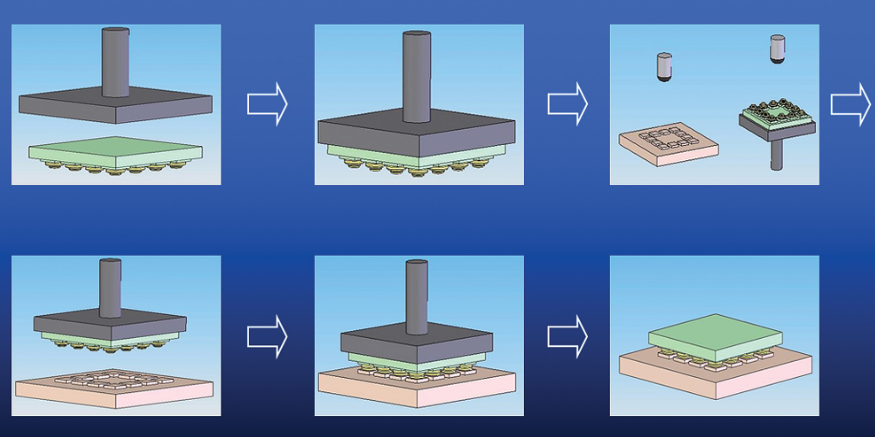

倒裝芯片晶體貼裝技術(shù)

Bumping是一種新型的芯片與基板間電氣互聯(lián)的方式。

可以通過小的球形導(dǎo)電材料實(shí)現(xiàn),這種導(dǎo)電球體被稱為Bump,制作導(dǎo)電球這一工序被稱為Bumping。當(dāng)粘有Bump的晶粒被倒臵(Flip-Chip)并與基板對齊時(shí),晶粒便很容易的實(shí)現(xiàn)了與基板Pad(觸墊)的連接。相比傳統(tǒng)的引線連接,F(xiàn)lip-Chip有著諸多的優(yōu)勢,比如更小的封裝尺寸與更快的器件速度。

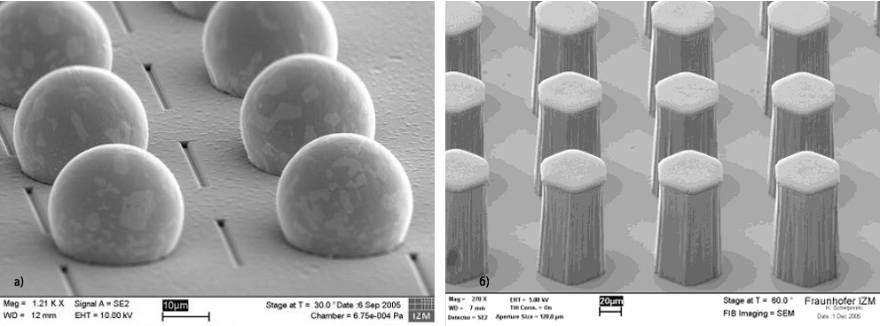

焊球端子和柱式端子

FlipChip的關(guān)鍵一步是Bumping,可以通過在晶圓上制作外延材料來實(shí)現(xiàn)。

當(dāng)芯片制作工序完成后,制造UBM(Underbumpmetallization)觸墊將被用于實(shí)現(xiàn)芯片和電路的連接,Bump也會被淀積與觸點(diǎn)之上。焊錫球(Solderball)是最常見的Bumping材料,但是根據(jù)不同的需求,金、銀、銅、鈷也是不錯(cuò)的選擇。對于高密度的互聯(lián)及細(xì)間距的應(yīng)用,銅柱是一種新型的材料。焊錫球在連接的時(shí)候會擴(kuò)散變形,而銅柱會很好的保持其原始形態(tài),這也是銅柱能用于更密集封裝的原因。

FlipChip產(chǎn)品對應(yīng)不同bumping類型增長速度不一。

根據(jù)Yole預(yù)測,采用倒裝芯片技術(shù)的集成電路出貨量將保持穩(wěn)定增長,預(yù)計(jì)產(chǎn)能將以9.8%的復(fù)合年增長率擴(kuò)張,從2014年的約合1600萬片12寸晶圓增長到2020年的2800萬片。終端應(yīng)用主要為計(jì)算類芯片,如臺式機(jī)和筆記本電腦的CPU、GPU和芯片組應(yīng)用等。

其中鍍金晶圓凸點(diǎn)(Au-platedwaferbumping)將穩(wěn)定增長,由于IC顯示驅(qū)動(dòng)器(4K2K超高清電視和高清晰度、大屏幕平板電腦和智能手機(jī))的市場驅(qū)動(dòng)。預(yù)計(jì)產(chǎn)能將以4%的復(fù)合年增長率擴(kuò)大,從2014年的430萬片增長到2020年的540萬片。

金釘頭凸點(diǎn)(Austudbumping)產(chǎn)能將略有下滑,從2014年的30.4萬片降到2020年的29.3萬片,主要原因是射頻器件從倒裝芯片轉(zhuǎn)移至晶圓級芯片尺寸封裝(WLCSP)。但是,新興應(yīng)用的需求將增加,如CMOS圖像傳感器模組、高亮度LED等。

中道封裝技術(shù)需求增長,將帶來行業(yè)上下游的跨界競爭。針對3DIC和2.5D中介層平臺的“中端工藝(middleend-process)”基礎(chǔ)設(shè)施的出現(xiàn)將使Fab和IDM受益,并在較小程度上分給OSAT。2.5D中介層平臺的發(fā)展將會產(chǎn)生價(jià)值的轉(zhuǎn)移,從襯底供應(yīng)商轉(zhuǎn)向前端代工廠。

2.5D封裝:RDL&中介層

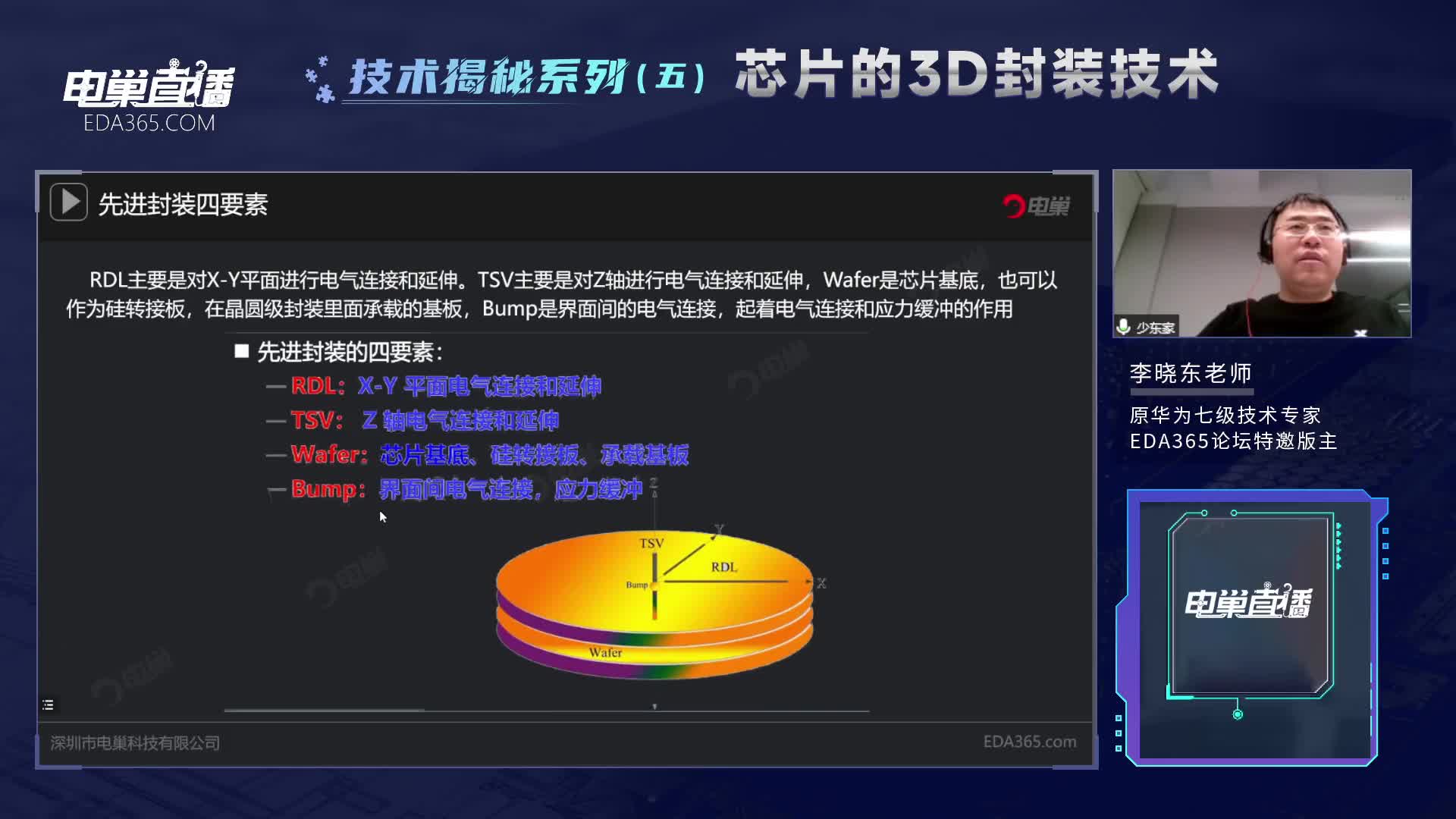

RDL(Redistributionlayer,再分布層):在晶圓水平上,觸點(diǎn)再分布可以很高效的進(jìn)行。再分布層用于使連線路徑重新規(guī)劃,落到我們希望的區(qū)域,也可以獲得更高的觸點(diǎn)密度。再分布的過程,實(shí)際上是在原本的晶圓上又加了一層或幾層。首先淀積的是一層電介質(zhì)用于隔離,接著我們會使原本的觸點(diǎn)裸露,再淀積新的金屬層來實(shí)現(xiàn)重新布局布線。UBM在這里會被用到,作用是支撐焊錫球或者其他材料的接觸球。

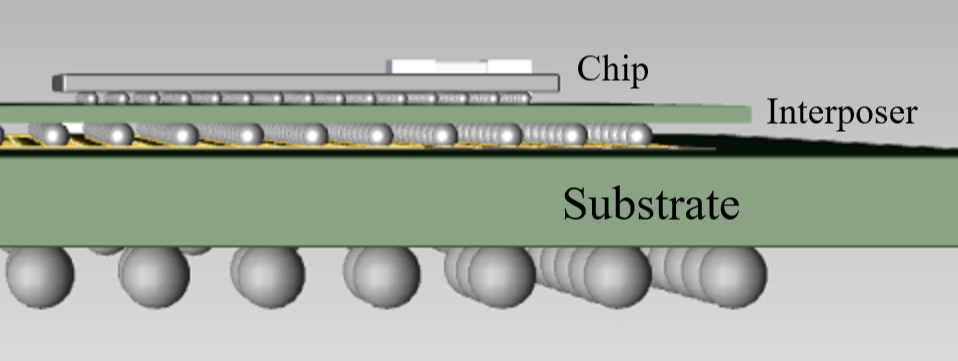

中介層(Interposer):指的是焊錫球和晶粒之間導(dǎo)電層。它的作用是擴(kuò)大連接面,使一個(gè)連接改線到我們想要的地方。與再分布層作用類似。

中間層(Interposer)示意

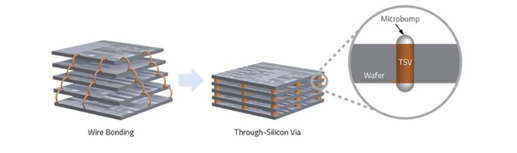

3D封裝:TSV,PoP和MEMS

TSV(Through-siliconvia,硅通孔):Bump和RDL會占用芯片接合到基板上的平面面積,TSV可以將芯片堆疊起來使三維空間被利用起來。更重要的是,堆疊技術(shù)改善了多芯片連接時(shí)的電學(xué)性質(zhì)。引線鍵合可以被用于堆疊技術(shù),但TSV吸引力更大。TSV實(shí)現(xiàn)了貫穿整個(gè)芯片厚度的電氣連接,更開辟了芯片上下表面之間的最短通路。芯片之間連接的長度變短也意味著更低的功耗和更大的帶寬。TSV技術(shù)最早在CMOS圖像傳感器中被應(yīng)用,未來在FPGA、存儲器、傳感器等領(lǐng)域都將被應(yīng)用。根據(jù)Yole預(yù)測,2016~2021年,應(yīng)用TSV技術(shù)的晶圓數(shù)量將以10%的年復(fù)合增長率增長。3D存儲芯片封裝也會在將來大量的用到TSV。

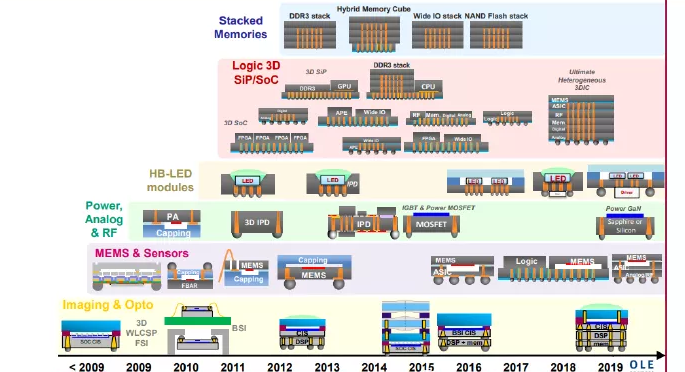

3DIC和TSV技術(shù)演進(jìn)路徑

TSV技術(shù)示意圖

PoP(PackageonPackage,堆疊封裝):PoP是一種將分離的邏輯和存儲BGA(Ballgridarray,球狀引腳柵格陣列)包在垂直方向上結(jié)合起來的封裝技術(shù)。在這種結(jié)構(gòu)中,兩層以上的封裝單元自下而上堆疊在一起,中間留有介質(zhì)層來傳輸信號。PoP技術(shù)增大了器件的集成密度,底層的封裝單元直接與PCB板接觸。傳統(tǒng)的PoP是基于基板的堆疊,隨著存儲器對高帶寬的需求,球間間隔要求更小,未來將會與FOWLP技術(shù)相結(jié)合,做基于芯片的堆疊。

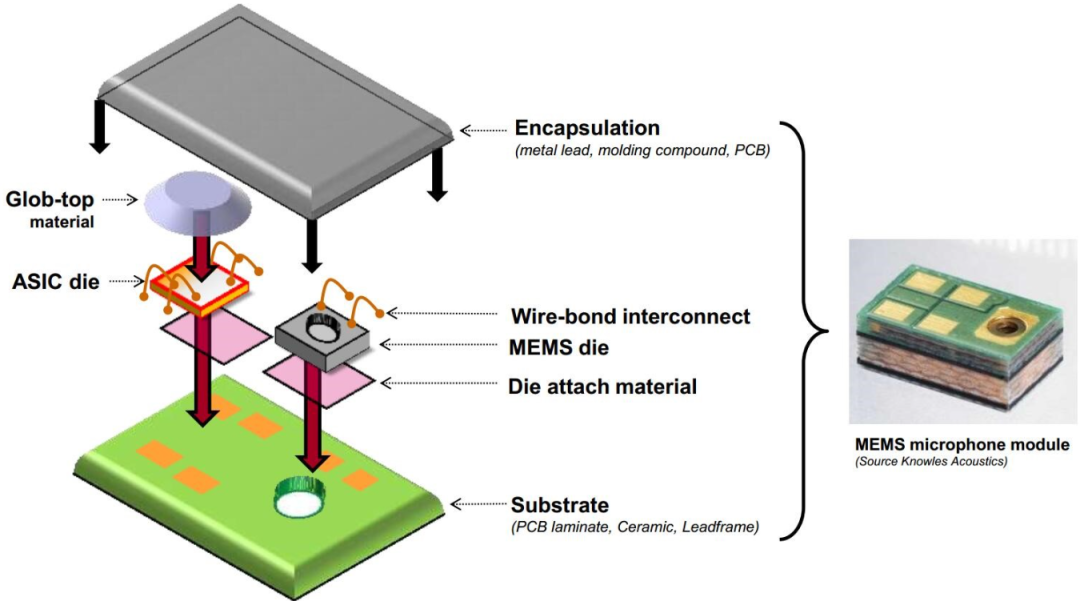

MEMS封裝:微機(jī)電系統(tǒng)在近些年應(yīng)用越來越廣泛,隨著傳感器、物聯(lián)網(wǎng)應(yīng)用的大規(guī)模落地,MEMS封裝也備受關(guān)注。MEMS的封裝不同與集成電路封裝,分為芯片級、模組級、卡級、板級、門級等多元垂直分級封裝,設(shè)計(jì)時(shí)也需考慮不同模組間的相互影響。目前MEMS封裝市場規(guī)模在27億美元左右,20162020年間將會維持16.7%的年復(fù)合增長率高速增長。其中RFMEMS封裝市場是主要驅(qū)動(dòng),20162020年間,年復(fù)合增長率高達(dá)35.1%。

MEMS封裝技術(shù)示意圖

在整個(gè)MEMS生態(tài)系統(tǒng)中,MEMS封裝發(fā)展迅速,晶圓級和3D集成越來越重要。主要的趨勢是為低溫晶圓鍵合等單芯片集成開發(fā)出與CMOS兼容的MEMS制造工藝。另一個(gè)新趨勢是裸片疊層應(yīng)用于低成本無鉛半導(dǎo)體封裝,這種技術(shù)可為量產(chǎn)帶來更低的成本和更小的引腳封裝。但是,MEMS器件的CMOS和3D集成給建模、測試和可靠性帶來挑戰(zhàn)。

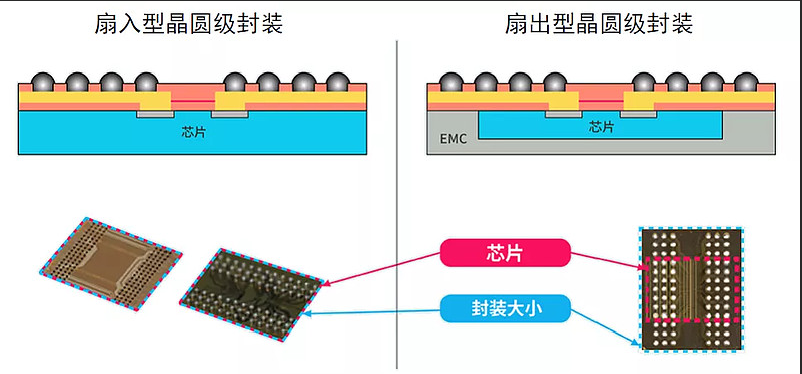

FIWLP&FOWLP,PLP

首先要提及Wafer-levelpackaging(WLP,晶圓級封裝)的概念。在傳統(tǒng)封裝概念中,晶圓是先被切割成小的晶粒,之后再進(jìn)行連接和塑封。而晶圓級封裝工序恰好相反,晶圓級封裝將晶粒在被切割前封裝完成,保護(hù)層將會被附著在晶圓的正面或是背面,電路連接在切割前已經(jīng)完成。

FIWLP:Fan-inWafer-levelpackaging,又稱WLCSP(Wafer-levelChipScalePackage),扇入式晶圓級封裝,也就是傳統(tǒng)的晶圓級封裝,切割晶粒在最后進(jìn)行,適用于低引腳數(shù)的集成電路。隨著集成電路信號輸出的引腳數(shù)目的增加,焊錫球的尺寸也就變得越來越嚴(yán)格,PCB對集成電路封裝后尺寸以及信號輸出接腳位臵的調(diào)整需求得不到滿足,因此衍生出了扇出型晶圓級封裝。扇入晶圓級封裝的特征是封裝尺寸與晶粒同大小。

FOWLP:Fan-outWafer-levelpackaging,扇出式晶圓級封裝,開始就將晶粒切割,再重布在一塊新的人工模塑晶圓上。它的優(yōu)勢在于減小了封裝的厚度,增大了扇出(更多的I/O接口),獲得了更優(yōu)異的電學(xué)性質(zhì)及更好的耐熱表現(xiàn)。

FIWLP與FOWLP用途不同,均為今后的主流封裝手段。FIWLP在模擬和混合信號芯片中用途最廣,其次是無線互聯(lián),CMOS圖像傳感器也采用FIWLP技術(shù)封裝。FOWLP將主要用于移動(dòng)設(shè)備的處理器芯片中。根據(jù)Yole的預(yù)測,2018年以前FOWLP的主要驅(qū)動(dòng)為蘋果智能手機(jī)的處理器芯片,2018年以后的FOWLP的主要驅(qū)動(dòng)除了其他安卓手機(jī)處理器的增長,主要是高密度FOWLP在其他處理芯片的應(yīng)用,如AI、機(jī)器學(xué)習(xí)、物聯(lián)網(wǎng)等領(lǐng)域。

FIWLP與FOWLP技術(shù)示意圖

PLP:全稱Panel-levelpackaging,平板級封裝,封裝方法與FOWLP類似,只不過將晶粒重組于更大的矩形面板上,而不是圓形的晶圓。更大的面積意味著節(jié)約更多的成本,更高的封裝效率。而且切割的晶粒為方形,晶圓封裝會導(dǎo)致邊角面積的浪費(fèi),矩形面板恰恰解決了浪費(fèi)問題。但也對光刻及對準(zhǔn)提出了更高的要求。

審核編輯:湯梓紅

-

半導(dǎo)體

+關(guān)注

關(guān)注

335文章

28599瀏覽量

232524 -

電路板

+關(guān)注

關(guān)注

140文章

5090瀏覽量

101515 -

BGA

+關(guān)注

關(guān)注

5文章

565瀏覽量

48139 -

先進(jìn)封裝

+關(guān)注

關(guān)注

2文章

462瀏覽量

510

原文標(biāo)題:【漲知識】傳統(tǒng)封裝vs先進(jìn)封裝區(qū)別和分類!

文章出處:【微信號:today_semicon,微信公眾號:今日半導(dǎo)體】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

傳統(tǒng)封裝和先進(jìn)封裝的區(qū)別在哪

HRP晶圓級先進(jìn)封裝替代傳統(tǒng)封裝技術(shù)研究(HRP晶圓級先進(jìn)封裝芯片)

#硬聲創(chuàng)作季 先進(jìn)封裝技術(shù)詳解——什么是良率?什么是晶圓級封裝?什么是2.5D封裝?

#硬聲創(chuàng)作季 【科普向】傳統(tǒng)封裝與先進(jìn)封裝有何差異?——為什么需要先進(jìn)封裝

傳統(tǒng)封裝你了解多少,小白快捷學(xué)習(xí) | 第1集 #傳統(tǒng)封裝 #先進(jìn)封裝 #芯片封裝 #華芯邦 #

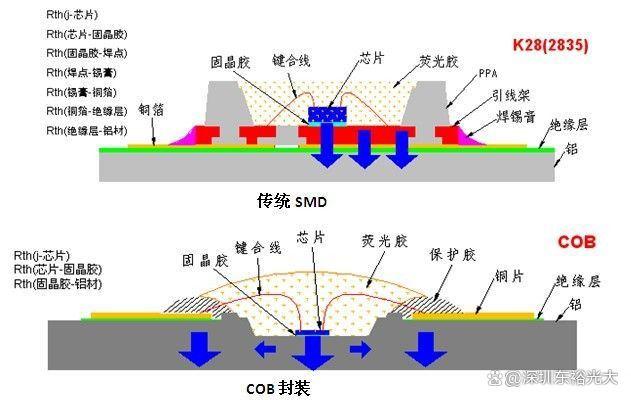

關(guān)于LED封裝的不同,COB封裝與傳統(tǒng)LED封裝的區(qū)別

先進(jìn)封裝對比傳統(tǒng)封裝的優(yōu)勢及封裝方式

SiP與先進(jìn)封裝有什么區(qū)別

什么是先進(jìn)封裝?先進(jìn)封裝和傳統(tǒng)封裝區(qū)別 先進(jìn)封裝工藝流程

什么是先進(jìn)封裝?和傳統(tǒng)封裝有什么區(qū)別?

HRP晶圓級先進(jìn)封裝替代傳統(tǒng)封裝技術(shù)研究

COB封裝與傳統(tǒng)封裝的區(qū)別及常見問題

先進(jìn)封裝與傳統(tǒng)封裝的區(qū)別

先進(jìn)封裝的重要設(shè)備有哪些

傳統(tǒng)封裝和先進(jìn)封裝的區(qū)別

傳統(tǒng)封裝和先進(jìn)封裝的區(qū)別

評論