以《戰(zhàn)略緒論》一書聞名的近代法國戰(zhàn)略大師薄富爾曾說:「戰(zhàn)略的要義是『預(yù)防』而非『治療』,『未來和準(zhǔn)備』比『現(xiàn)在和執(zhí)行』更重要。」半導(dǎo)體業(yè)界亦同,當(dāng)摩爾定律所預(yù)言的制程微縮曲線開始鈍化,將不同制程性質(zhì)的芯片,透過多芯片封裝包在一起,以最短的時程推出符合市場需求的產(chǎn)品,就成為重要性持續(xù)水漲船高的技術(shù)顯學(xué)。 而這些先進芯片封裝也成為超級電腦和人工智能的必備武器。別的不提,光論nVidia 和AMD 的高效能運算專用GPU、Google 第二代TPU、無數(shù)「人工智能芯片」,就處處可見HBM 記憶體的存在。

畢竟天底下沒有面面俱到的半導(dǎo)體制程,觀察到先進制程晶圓廠每隔4 年成本倍增的「摩爾第二定律」,也突顯了電晶體單位成本越來越高的殘酷現(xiàn)實。AMD 處理器從7 納米制程開始全面性「Chiplet 化」,將7 納米制程的CPU 核心和12 納米制程的I/O 記憶體控制器分而治之,實乃不得不然。

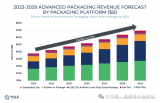

發(fā)展方興未艾的先進封裝技術(shù)

也因此,無論臺積電還是英特爾,無不拼命加碼,相關(guān)產(chǎn)品也如雨后春筍一個個冒出頭來,而AMD 更在未來產(chǎn)品計畫,大剌剌寫著「融合2.5D 與3D 的X3D 封裝」(雖然大概也是直接沿用臺積電的現(xiàn)有技術(shù)),以達成超過時下產(chǎn)品十倍的記憶體頻寬密度。

稍微替各位復(fù)習(xí)一下什么是「2.5D」封裝,臺積電擁有超過60 個實際導(dǎo)入案例的CoWos(Chip-on-Wafer-on-Substrate)算是這領(lǐng)域最為知名的技術(shù),包含近期奪下超級電腦Top500 榜首的Fujitsu A64FX。英特爾用自家EMIB(Embedded Multi-Die Interconnect Bridge)將Kaby Lake 處理器與AMD Vega 繪圖核心「送作堆」的Kaby Lake-G,也曾是轟動一時的熱門話題。

有別于「2D」的SiP(System-in-Package),2.5D 封裝在SiP 基板和芯片之間,插入了矽中介層(Silicon Interposer),透過矽穿孔(TSV,Through-Silicon Via)連接上下的金屬層,克服SiP 基板(像多層走線印刷電路板)難以實做高密度布線而限制芯片數(shù)量的困難。

「疊疊樂」的3D 封裝就不難理解了,臺積電就靠著可減少30% 的封裝厚度InFO(Integrated Fan-Out),在iPhone 7 的A10 處理器訂單爭奪戰(zhàn)擊敗三星,終結(jié)了消費者購買iPhone 6S 還得擔(dān)心拿到三星版A9 的尷尬處境(筆者不幸曾是受害者之一)。但3D 封裝的散熱手段與熱量管理,也是明擺在半導(dǎo)體產(chǎn)業(yè)界的艱巨挑戰(zhàn)。

英特爾相對應(yīng)的3D 封裝技術(shù)則為Foveros。最近正式發(fā)表、代號Lakefield 的「混合式x86 架構(gòu)處理器」,堆疊了「1 大4 小核心」的10 納米制程(代號P1274)運算芯片、22 納米制程(代號P1222)系統(tǒng)I/O 芯片和PoP(Package-on-Package)封裝的記憶體,待機耗電量僅2mW。

英特爾2019 年7 月公布的Co-EMIB,用2.5D 的EMIB 連接多個3D 的Foveros 封裝,「整合成具備更多功能」的單一芯片。為EMIB 概念延伸的ODI(Omni-Directional Interconnect)則用來填補EMIB 與Foveros 之間的鴻溝,為封裝內(nèi)眾多裸晶連接提供更高靈活性,細節(jié)在此不論。

連接封裝內(nèi)多顆裸晶之間的匯流排也是不可或缺的技術(shù)。 英特爾在2017 年將EMIB 連接裸晶的「矽橋」(Silicon Bridge)正式命名為「先進介面匯流排」(AIB,Advanced Interface Bus)并公開免費授權(quán),2018 年將AIB 捐贈給美國國防先進研究計劃署(DARPA),當(dāng)作免專利費的裸晶互連標(biāo)準(zhǔn),MDIO(Multi-Die I/O)則是AIB 的下一代。臺積電相對應(yīng)技術(shù)則為LIPINCON(Low-voltage-INPackage-INterCONnect),規(guī)格與英特爾互有長短。

超級電腦用的系統(tǒng)單芯片并非IBM 和Fujitsu 的專利

長期關(guān)心ARM 指令集相容處理器與超級電腦的讀者,想必對先前采用Fujitsu A64FX 處理器打造的日本理化學(xué)研究所的「富岳」并不陌生。這顆臺積電7 納米制程并CoWoS 2.5D 封裝4 顆8GB HBM2 記憶體的產(chǎn)物,堪稱當(dāng)代最具代表性的「超級電腦專用系統(tǒng)單芯片」,讓人不得不想起十幾年前的IBM BlueGene /L。

曾在21 世紀(jì)初期靠著「地球模擬器」(Earth Simulator)獨領(lǐng)風(fēng)騷兩年多的NEC,其SX 向量處理器的最新成員SX-Aurora TSUBASA,也是臺積電16 納米制程、2.5D 封裝6 顆8GB HBM2 記憶體的超級電腦心臟。

而英特爾的Xeon Phi 系列更是知名代表,透過2.5D 封裝包了8 顆2GB MCDRAM(Multi-Channel DRAM),可設(shè)定為快取記憶體、主記憶體或混合兩者之用。雖然Xeon Phi 家族兩年前慘遭腰斬,中斷自從Larrabee 以來的「超級多核心x86」路線,英特爾決定整個砍掉重練,一步一腳印重頭打造「傳統(tǒng)GPU」當(dāng)作未來高效能運算與人工智能應(yīng)用的基礎(chǔ),但異質(zhì)多芯片封裝的重要性仍不減反增,最起碼被英特爾從AMD 挖角、主導(dǎo)GPU 發(fā)展的Raja Koduri,自己是這樣講的,也沒什么懷疑的空間。

不過AMD 也并未缺席,并看似有后來居上的氣勢,而且這并非突發(fā)奇想,早在2010 年之前,就開始進行長期研究,至今超過十年,并「很有可能」以EHP(Exascale Heterogenous Processor)之名開花結(jié)果,融合2.5D 與3D 封裝的X3D 則是達成EHP 的關(guān)鍵。

Exa 意指Peta 的1 千倍,也是近年來超級電腦的下一個競爭指標(biāo),像預(yù)定采用AMD Zen 2 世代EPYC 處理器的美國國家核能安全管理局El Capitan 超級電腦,理論運算效能就超過2ExaFlops。

AMD 自從2007 年購并ATI 之后,整合處理器與繪圖核心的APU 之路,一直走得相當(dāng)掙扎,遲遲難以找到適合的產(chǎn)品規(guī)格與市場定位,不是CPU 不夠好、GPU 不夠強、就是兩者都不上不下,到了Zen 2 世代才算脫胎換骨。 這些年來,AMD 在超級電腦市場逐漸邊緣化,今年6 月的Top500 只剩下10 臺AMD CPU 和一臺AMD GPU,更需要強力的新兵器,才能「突破英特爾和nVidia 的封鎖」。身為「超級電腦APU」的EHP 就成為AMD 默默進行的新方向。

以加拿大ATI身分在2010年申請「藉由假矽穿孔替3D封裝進行導(dǎo)熱」(Dummy TSV To Improve Process Uniformity and Heat Dissipation)專利為起點,AMD一路累積了「記憶體運算的快取資料一致性」 (2016年)、「3D晶粒堆疊的熱量管理」(2017年)、「擁有極致頻寬與可延展性能耗比的GPU架構(gòu)」(2017年)、「記憶體內(nèi)運算的陣列」(2018年) 、「回圈脫離預(yù)測(2018年)以改善閑置模式的效率」到「混合CPU與GPU的動態(tài)記憶體管理」(2018年)等成果,確定了AMD在2015年的財務(wù)分析師大會透露的「伺服器專用APU」與當(dāng)年7月IEEE Micro發(fā)表的「藉由異質(zhì)運算實現(xiàn)百億億級運算」(Achieving Exascale Capabilities through Heterogeneous Computing)計畫并不是玩假的,更何況現(xiàn)在AMD當(dāng)家作主的還是一位以務(wù)實聞名的全球薪酬最高女性執(zhí)行長。

根據(jù)已公開的資料,EHP 概略規(guī)格如下,但后面勢必將隨著技術(shù)演進而有更動:

32 個CPU 核心(當(dāng)時是8 顆4 核心CCD)。

8 顆32 個GPU CU,總計256 CU 與16,384 個串流處理器(那時預(yù)定是GCN 第五代的Vega,看來將會推進到CDNA)。

8 塊4GB HBM2 記憶體堆疊。

時脈1GHz 時,雙倍浮點精確度理論效能為16TeraFlops,如十萬顆組成超級電腦,就是1.6ExaFlops,預(yù)估耗電量為20MW。

AMD 在2015 年7 月IEEE Micro 專文,表示32 個CPU 核心、320 個時脈1GHz 的GPU CU(20,480 個串流處理器)、3TB/s 記憶體頻寬、160W 功耗,是能耗比最好的組態(tài),總之實際的產(chǎn)品一定會變。

EHP 和X3D 的技術(shù)資產(chǎn)會「推己及人」到Zen 3 世代EPYC 處理器「Milan」的可怕傳言(像10 顆CCD 湊80 核心或塞HBM2 當(dāng)L4 之類的),一直沒有停過。

EHP 也有配置芯片封裝以外的外部記憶體,像斷電后資料不會消失的NVRAM(Non-Volatile RAM,如英特爾/Micro 的3D Xpoint 和發(fā)展中SST-MRAM 等)和「記憶體內(nèi)運算」的PIM (Processing-In-Memory,記憶體內(nèi)建位元運算電路),相關(guān)的動態(tài)記憶體管理與快取資料一致性,也是AMD 需要克服的技術(shù)門檻,至于軟體環(huán)境的完備性,更將是AMD 能否追上nVidia 的最核心因素。

同場加映:nVidia 也沒吃飽閑著

近來因「光明的未來前瞻性」而讓公司市值一舉超越英特爾的nVidia,在高效能運算、人工智能與自駕車等領(lǐng)域的優(yōu)勢地位幾乎是牢不可破。除了帳面硬體規(guī)格,發(fā)展了十多年的CUDA 應(yīng)用環(huán)境生態(tài)、遠遠超越英特爾和AMD 的GPU 虛擬化(這讓客戶使用AMD GPU 部署云端個人電腦的效益會明顯不如nVidia,云端服務(wù)業(yè)者的虛擬GPU 亦同,比較一下可負荷用戶端數(shù)量,就知道差別有多大了)和更多「不足外人道也」之處,才是支撐nVidia 股價的真正根基。 將話題拉回多芯片封裝這件事,就算不論以「訓(xùn)練」為主的高階GPU,nVidia 連「推論」用的芯片研究案都走向「多芯片封裝延展性」。

但各位有沒有想過一個更有趣的可能性:既然nVidia 高階GPU 都這么大顆,干么不干脆「順便」包一顆高效能的ARM(或RISC-V)指令集相容處理器,不再是英特爾、AMD 處理器的「附屬品」,讓GPU 變身成「可自行開機的超級電腦系統(tǒng)單芯片」? 事實上,nVidia GPU 內(nèi)本來就有內(nèi)建好幾顆簡稱為Falcon(Fast Logic Controller)的微控制器,用來輔助GPU 運算處理,像支援影像圖形解碼到安全性機制,或減輕CPU 執(zhí)行驅(qū)動程式的負擔(dān),如以前因為Windows 作業(yè)系統(tǒng)的延遲程序呼叫(DPC,Deferred Procedure Call)會逾時而不能進行的排程等。 2016 年,nVidia 先采用柏克萊大學(xué)的開源RISC-V 指令集相容處理器Rocket,開發(fā)出第一代Falcon 微控制器,2017 年第二代產(chǎn)品擴展到64 位元,并自行新增自定義的新指令。前述由27 顆封裝而成的RC18 推論芯片,也是RISC-V 核心,每秒可執(zhí)行128 兆次推論,功耗僅13.5W。 那么未來,假如nVidia 將「更多的工作」搬到GPU 內(nèi)的RISC-V 核心,特別是驅(qū)動程式涉及大量GPU 底層機密資訊的「下面那一層」丟過去,或經(jīng)由GPU 虛擬化掩蓋起來,又會發(fā)生什么事?這件牽扯到另一個少人知悉的潛在需求了:來自官方的開源驅(qū)動程式。

弦外之音:GPU 驅(qū)動程式開源的沖擊

臺面上看不到或少人著墨的議題,舉足輕重的程度往往遠超乎看熱鬧外行人的想像。 無論超級電腦還是人工智能(尤其是人命關(guān)天的自動駕駛),基于安全性考量,芯片廠商的客戶或多或少都希望檢視所有程式碼,理所當(dāng)然包含驅(qū)動程式,這就是GPU 驅(qū)動程式開源之所以如此重要的主因。但偏偏這又是暗藏大量商業(yè)機密的黑盒子,要如何滿足客戶需求又不讓機密外泄,大方釋出「官方開源驅(qū)動程式」,就是nVidia、AMD 甚至即將「GPU 戰(zhàn)線復(fù)歸」的英特爾,已經(jīng)面對很久的機會與挑戰(zhàn)。 技術(shù)的發(fā)展跟著應(yīng)用的需求走,這恐怕也將會注定AMD 靠著「超級電腦APU」反攻高效能運算市場的企圖能否悲愿成就的鎖鑰。點到為止,剩下的就留給各位慢慢思考了。 本文轉(zhuǎn)載自:半導(dǎo)體行業(yè)觀察

原文標(biāo)題:市場 | 芯片巨頭決戰(zhàn)先進封裝

文章出處:【微信公眾號:旺材芯片】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

責(zé)任編輯:haq

-

芯片

+關(guān)注

關(guān)注

459文章

52165瀏覽量

436086 -

封裝

+關(guān)注

關(guān)注

128文章

8484瀏覽量

144776 -

gpu

+關(guān)注

關(guān)注

28文章

4909瀏覽量

130649 -

人工智能

+關(guān)注

關(guān)注

1804文章

48697瀏覽量

246437

原文標(biāo)題:市場 | 芯片巨頭決戰(zhàn)先進封裝

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

先進封裝工藝面臨的挑戰(zhàn)

玻璃基芯片先進封裝技術(shù)會替代Wafer先進封裝技術(shù)嗎

先進封裝成為AI時代的核心技術(shù)發(fā)展與創(chuàng)新

先進封裝的核心概念、技術(shù)和發(fā)展趨勢

先進封裝技術(shù)- 6扇出型晶圓級封裝(FOWLP)

先進封裝的技術(shù)趨勢

先進封裝技術(shù)的類型簡述

晶圓微凸點技術(shù)在先進封裝中的應(yīng)用

先進封裝技術(shù)綜述

發(fā)展方興未艾的先進封裝技術(shù)

發(fā)展方興未艾的先進封裝技術(shù)

評論