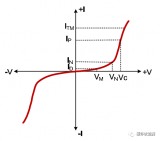

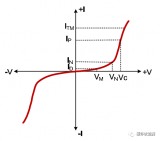

在大沖擊電流的作用下,ZnO非線性電阻具有動態伏安特性,作用在閥片上的實時電壓值不僅和實時電流值有關,而且和波頭時間有關,并導致沖擊電壓和沖擊電流不是同時而是電樂先于電流達到峰值。圖2.23所示為文獻[45]實測的對應8/20us和1/2.5us的雙指數電流沖擊波的電壓響應,作用在ZnO閥片上的電壓均超前電流到達峰值,試驗中的測量采用帶孔閥片的同軸布置方式,可以減小試驗回路中電感的影響。所有測量結果表明,在雷電流范圍內電壓峰值都比電流峰值出現早。

另外比較圖2.23(a)和(b)可以看出,1/2.5us電流波形的沖擊殘壓明顯高于8/20us的沖擊殘壓。說明ZnO閥片的沖擊殘壓還與波頭時間有關,波頭時間越短,沖擊殘樂越高。試驗表明,當施加的沖擊電流的波頭時間小于8ps時,動態效應就比較明顯,如沖擊電流幅值不變,其波頭時間從8μs減小到1us時,殘壓增加6%左右[46]。

圖2.24所示為對應圖2.23中電流電壓的實時波形所作的動態伏安特性。從圖中可以看出,動態伏安特性呈回環狀。

般采用的式(2.1)和式(2.2)所示為ZnO閥片中電流密度和電壓梯度幅值間的對應關系,通常稱為靜態伏安特性,可表示為U=f(I)(2.39)即電壓幅值U是電流幅值】的函數。實際上在沖擊電流作用下電壓幅值不僅與電流幅值有關,而且還與其變化率有關:

u-パ1照(2.40)即動態伏安特性的電壓幅值是電流幅值和電流變化率的函數。

2024-03-22 08:00:53

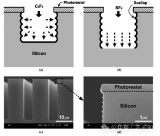

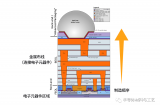

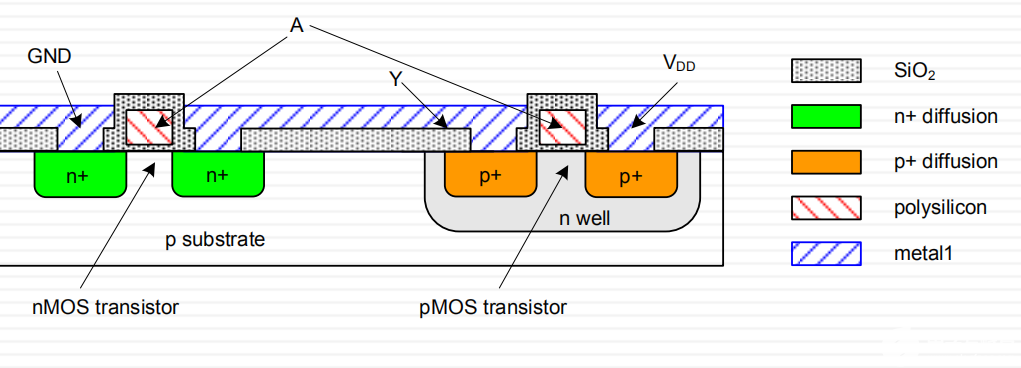

由于只有熱氧化法可以提供最低界面陷阱密度的高質量氧化層,因此通常采用熱氧化的方法生成柵氧化層和場氧化層。

2024-03-13 09:49:05 103

103

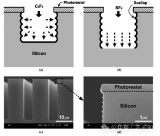

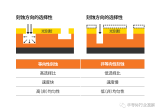

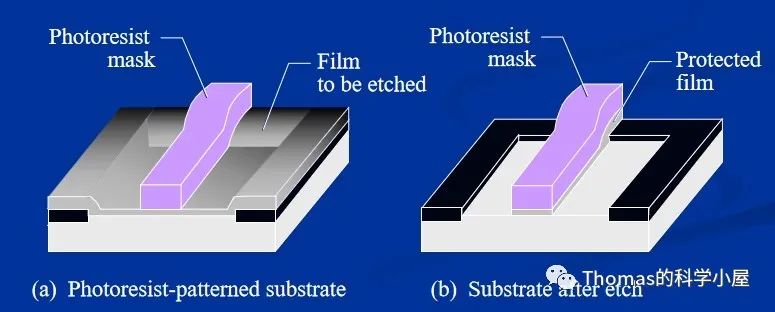

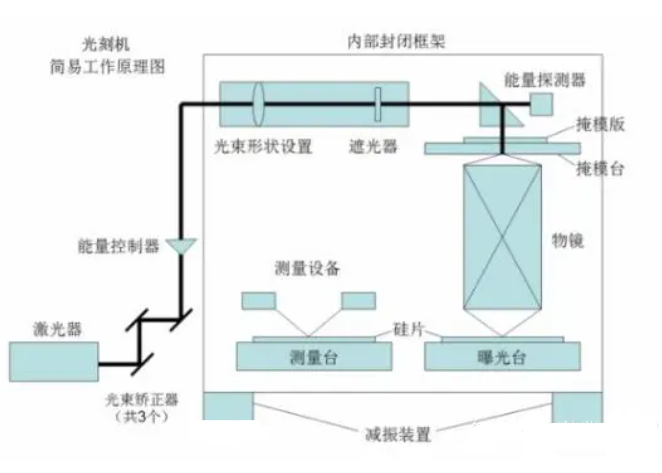

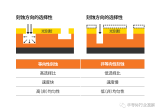

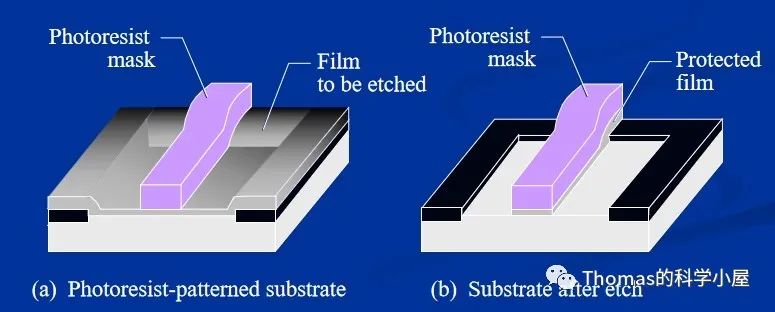

刻蝕機的刻蝕過程和傳統的雕刻類似,先用光刻技術將圖形形狀和尺寸制成掩膜,再將掩膜與待加工物料模組裝好,將樣品置于刻蝕室內,通過化學腐蝕或物理磨蝕等方式將待加工物料表面的非掩膜區域刻蝕掉,以得到所需的凹槽和溝槽。

2024-03-11 15:38:24 461

461

碳化硅圓盤壓敏電阻 |碳化硅棒和管壓敏電阻 | MOV / 氧化鋅 (ZnO) 壓敏電阻 |帶引線的碳化硅壓敏電阻 | 硅金屬陶瓷復合電阻器 |ZnO 塊壓敏電阻 關于EAK碳化硅壓敏電阻我們

2024-03-08 08:37:49

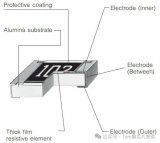

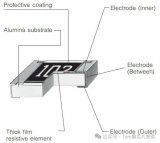

:電阻器件的數據手冊中通常會說明其制造工藝和材料類型,通過查閱相關數據手冊可以進一步確認電阻是薄膜還是厚膜。

需要注意的是,有些電阻可能是混合型的,既有薄膜又有厚膜的特性,因此在判斷電阻類型時需綜合考慮多個因素。如果無法確定電阻的類型,可以咨詢相關技術人員或參考電阻器件的制造商的說明。

2024-03-07 07:49:07

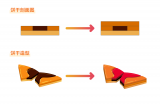

相對于塊體材料,膜一般為二維材料。薄膜和厚膜從字面上區分,主要是厚度。薄膜一般厚度為5nm至2.5μm,厚膜一般為2μm至25μm,但厚度并不是區分薄膜和厚膜的標準。

2024-02-28 11:08:51 370

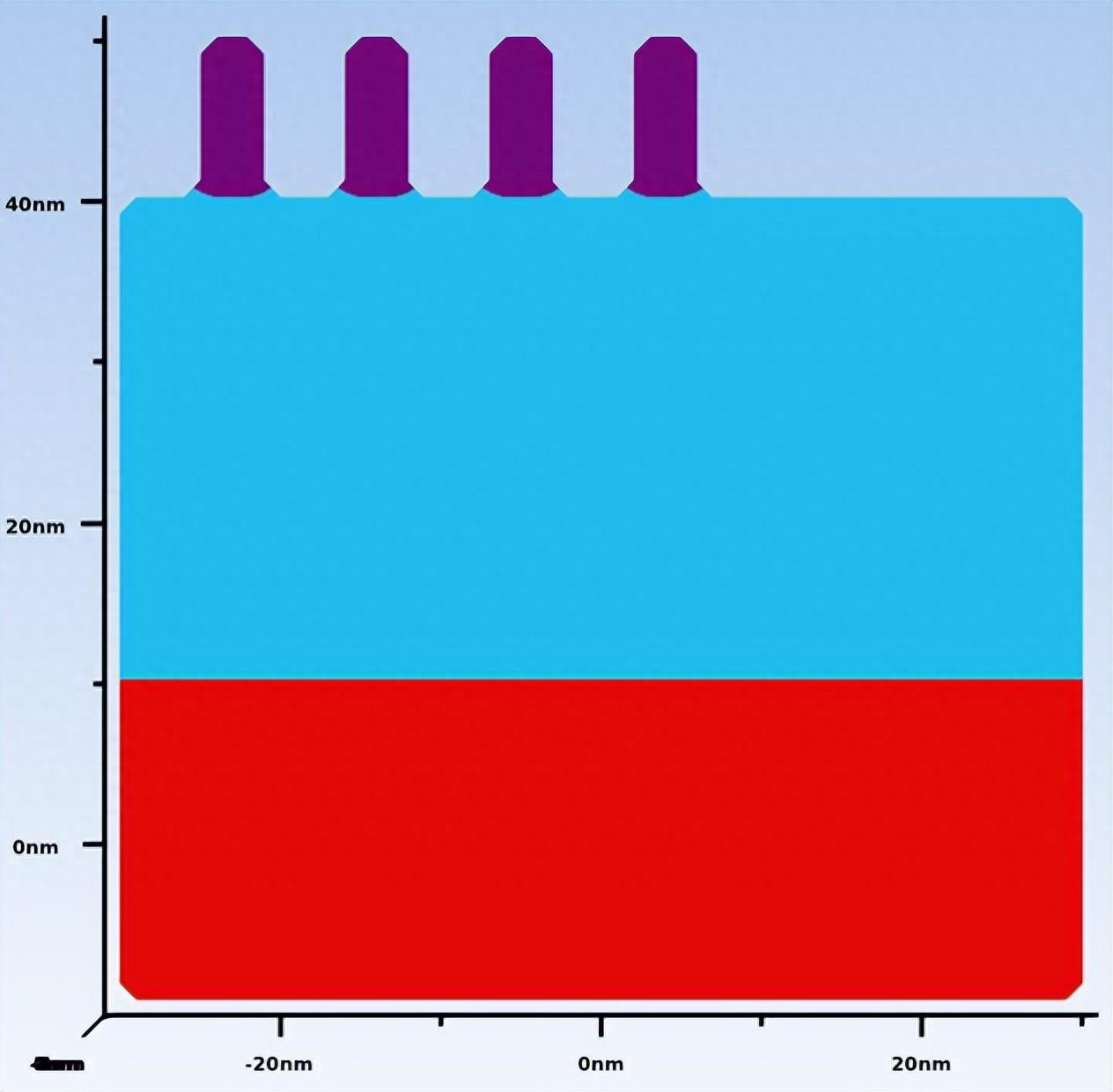

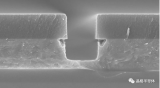

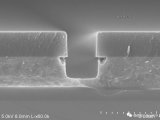

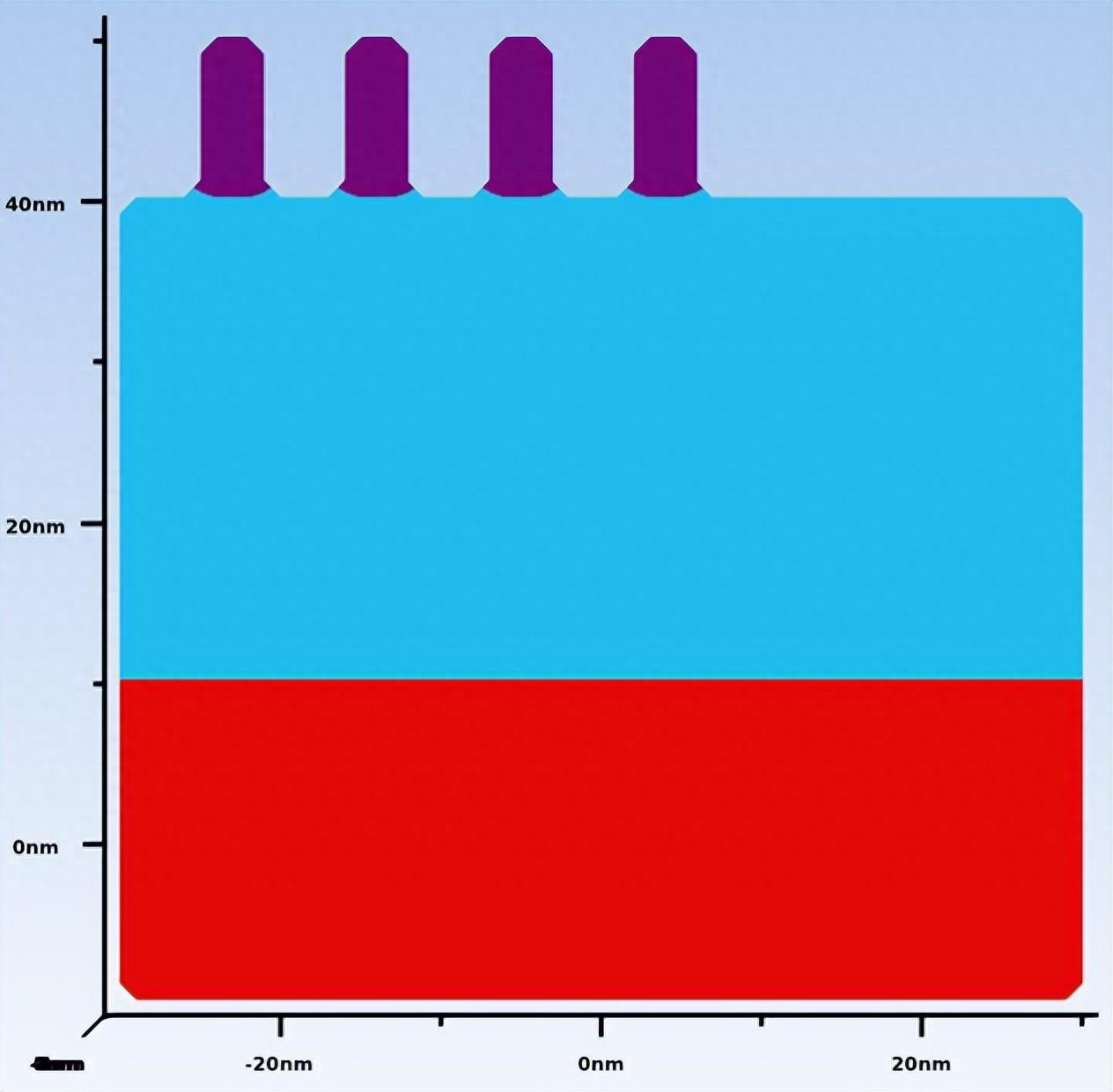

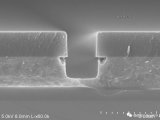

370 的 2.5D/3D 封裝技術可以實現芯片之間的高速、低功耗和高帶寬的信號傳輸。常見的垂直 TSV 的制造工藝復雜,容易造成填充缺陷。錐形 TSV 的側壁傾斜,開口較大,有利于膜層沉積和銅電鍍填充,可降低工藝難度和提高填充質量。在相對易于實現的刻蝕條件下制備

2024-02-25 17:19:00 119

119

影響深硅刻蝕的關鍵參數有:氣體流量、上電極功率、下電極功率、腔體壓力和冷卻器。

2024-02-25 10:44:39 283

283

在半導體制造領域,我們經常聽到“薄膜制備技術”,“薄膜區”,“薄膜工藝”等詞匯,那么有厚膜嗎?答案是:有。

2024-02-25 09:47:42 237

237

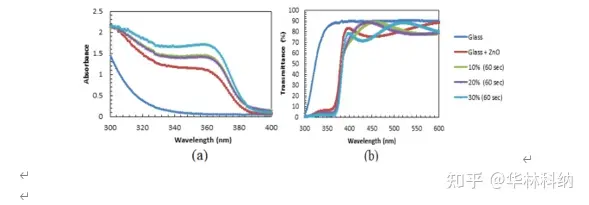

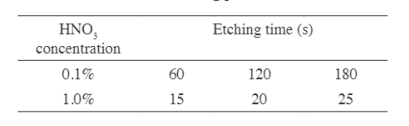

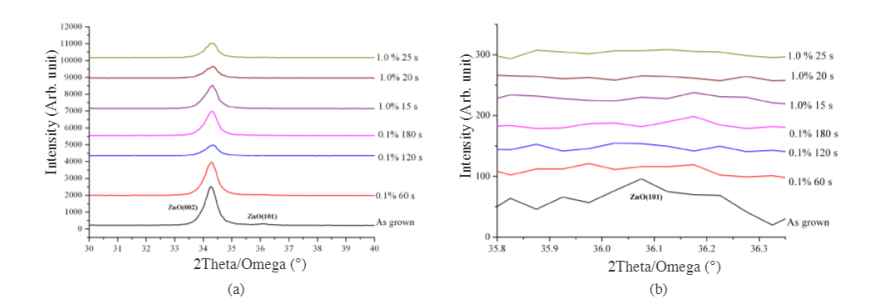

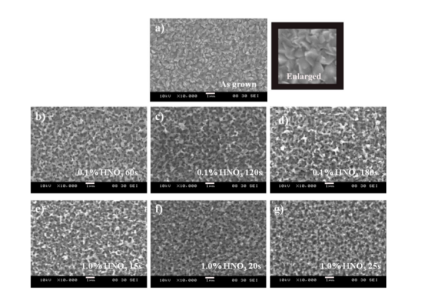

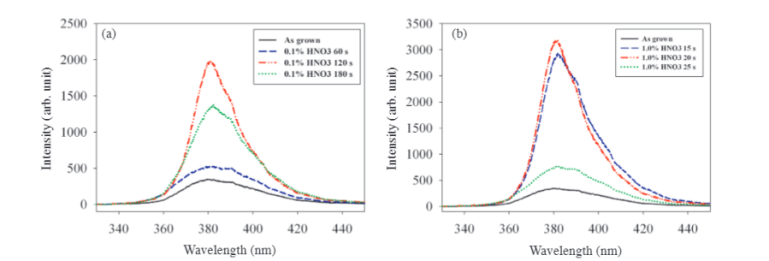

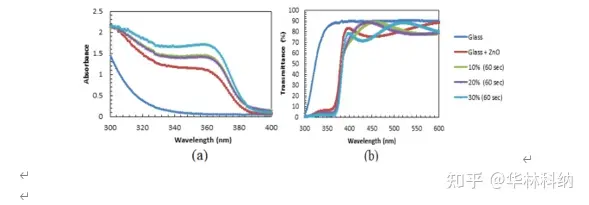

蝕刻時間和過氧化氫濃度對ZnO玻璃基板的影響 本研究的目的是確定蝕刻ZnO薄膜的最佳技術。使用射頻濺射設備在玻璃基板上沉積ZnO。為了蝕刻ZnO薄膜,使用10%、20%和30%的過氧化氫(H2O2

2024-02-02 17:56:45 306

306

Molex 的薄膜電池由鋅和二氧化錳制成,讓最終用戶更容易處置電池。大多數發達國家都有處置規定;這使得最終用戶處置帶有鋰電池的產品既昂貴又不便。消費者和醫療制造商需要穿著舒適且輕便的解決方案

2024-01-26 15:51:04

在半導體加工工藝中,常聽到的兩個詞就是光刻(Lithography)和刻蝕(Etching),它們像倆兄弟一樣,一前一后的出現,有著千絲萬縷的聯系,這一節介紹半導體刻蝕工藝。

2024-01-26 10:01:58 548

548

干法刻蝕技術是一種在大氣或真空條件下進行的刻蝕過程,通常使用氣體中的離子或化學物質來去除材料表面的部分,通過掩膜和刻蝕參數的調控,可以實現各向異性及各向同性刻蝕的任意切換,從而形成所需的圖案或結構

2024-01-20 10:24:56 1106

1106

ITO薄膜即銦錫氧化物半導體透明導電膜,主要優點是其高透明度和導電性,可以作為透明電極應用在光伏電池中。在TOPCon電池中,添加ITO薄膜可以有效提升電池的短路電流密度和轉換效率,是提高

2024-01-20 08:32:51 280

280

使用SEMulator3D?工藝步驟進行刻蝕終點探測 作者:泛林集團 Semiverse Solutions 部門軟件應用工程師 Pradeep Nanja 介紹 半導體行業一直專注于使用先進的刻蝕

2024-01-19 16:02:42 128

128

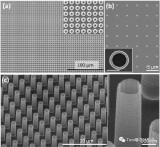

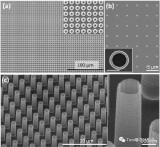

近期,來自西班牙加泰羅尼亞納米科學與納米技術研究所(ICN2)等機構的研究人員介紹了一種基于納米多孔石墨烯的薄膜技術及其形成柔性神經界面的工程策略。該研究所開發的技術可用于制造小型微電極(直徑 = 25?μm),同時實現低阻抗(~ 25?kΩ)和高電荷注入(3 ~ 5?mC/cm2)。

2024-01-15 15:55:48 263

263

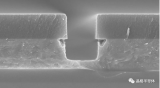

對DRIE刻蝕,是基于氟基氣體的高深寬比硅刻蝕技術。與RIE刻蝕原理相同,利用硅的各向異性,通過化學作用和物理作用進行刻蝕。不同之處在于,兩個射頻源:將等離子的產生和自偏壓的產生分離

2024-01-14 14:11:59 511

511

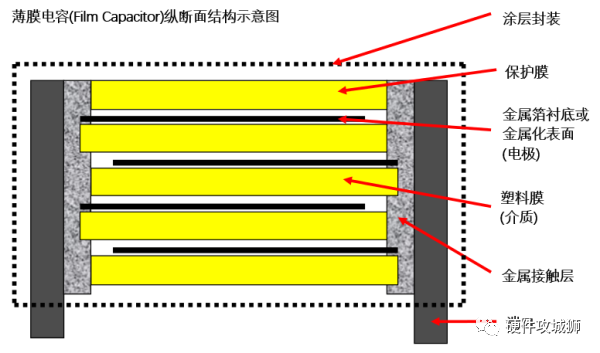

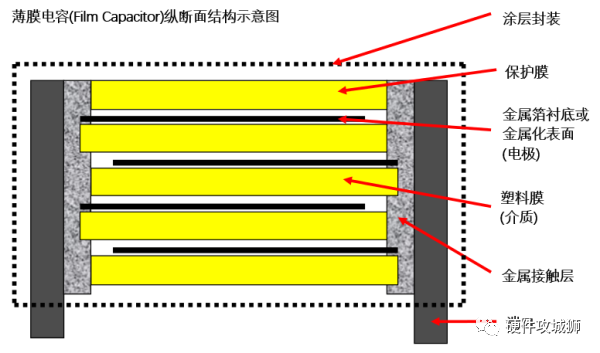

薄膜電容是一種常見的電子元件,其具有體積小、重量輕、容量大、可靠性高等優點,廣泛應用于各種電子設備中。薄膜電容的工藝與結構對其性能和可靠性有著重要的影響。本文將對薄膜電容的工藝與結構進行詳細的介紹

2024-01-10 15:41:54 443

443

在紅外探測器的制造技術中,臺面刻蝕是完成器件電學隔離的必要環節。

2024-01-08 10:11:01 206

206

TOPCon 電池的制備工序包括清洗制絨、正面硼擴散、BSG 去除和背面刻蝕、氧化層鈍化接觸制備、正面氧化鋁沉積、正背面氮化硅沉積、絲網印刷、燒結和測試分選,約 12 步左右。從技術路徑角度:LPCVD 方式為目前量產的主流工藝,預計 PECVD 路線有望成為未來新方向。

2023-12-26 14:59:11 2725

2725

氧化鋅避雷器具有良好的保護性能,在電氣系統和低壓電路中應用的很多。氧化鋅避雷器的工作原理是利用了氧化鋅壓敏電阻的非線性特點。

2023-12-25 11:35:07 489

489

電力安全是至關重要的。為了確保電力系統的穩定運行,氧化鋅避雷器發揮著重要的作用。 氧化鋅避雷器是一種用于電力系統的過電壓保護設備。它采用高性能的氧化鋅電阻片,能夠在雷電或操作過電壓等情況下,迅速

2023-12-14 10:26:59 177

177 多孔超級石墨烯在學術界通常被稱為多孔石墨烯(hG),它已經過完善,可以滿足高科技領域的要求,有望加速進步并推動進步。

2023-12-12 13:59:58 368

368 近日,中科院上海光機所高功率激光元件技術與工程部吳衛平研究員團隊采用飛秒激光結合模板法,構筑了內部孔隙精準可控且獨立支撐的多孔石墨烯薄膜,在自支撐多孔碳薄膜表面構筑三維陣列化石墨烯微結構,實現了光譜

2023-12-12 11:32:39 304

304

刻蝕的機制,按發生順序可概分為「反應物接近表面」、「表面氧化」、「表面反應」、「生成物離開表面」等過程。所以整個刻蝕,包含反應物接近、生成物離開的擴散效應,以及化學反應兩部分。

2023-12-11 10:24:18 250

250

金屬柵極的沉積方法主要由HKMG的整合工藝決定。為了獲得穩定均勻的有效功函數,兩種工藝都對薄膜厚度的均勻性要求較高。另外,先柵極的工藝對金屬薄膜沒有臺階覆蓋性的要求,但是后柵極工藝因為需要重新填充原來多晶硅柵極的地方,因此對薄膜的臺階覆蓋 性及其均勻度要求較高。

2023-12-11 09:25:31 659

659

在太陽能電池的生產工藝中,退火工藝和氧氣含量作為外界條件往往是影響ITO薄膜性能的關鍵因素,因此,為了較高程度的提升ITO薄膜的性能,電池廠商都會通過在生產中嚴謹的操作手段來保證其性能的提升,并通過

2023-12-07 13:37:19 292

292

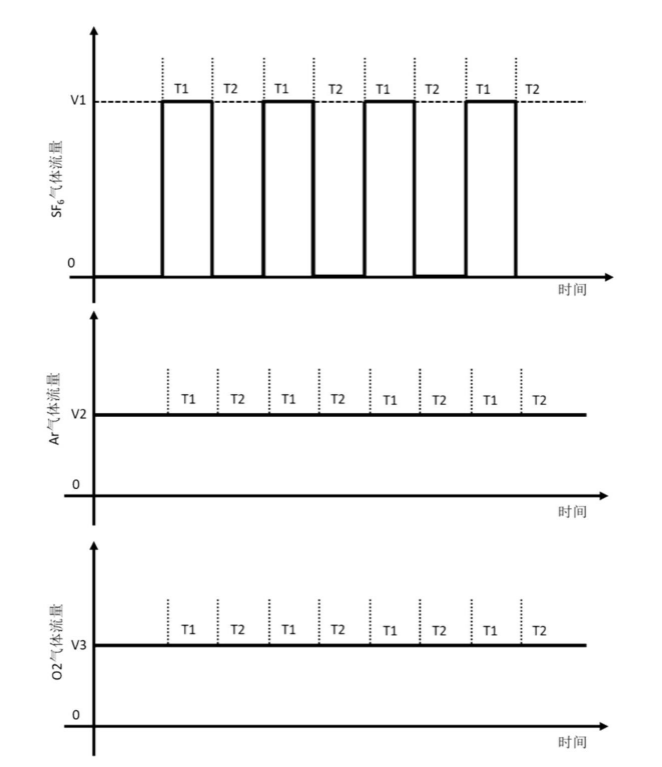

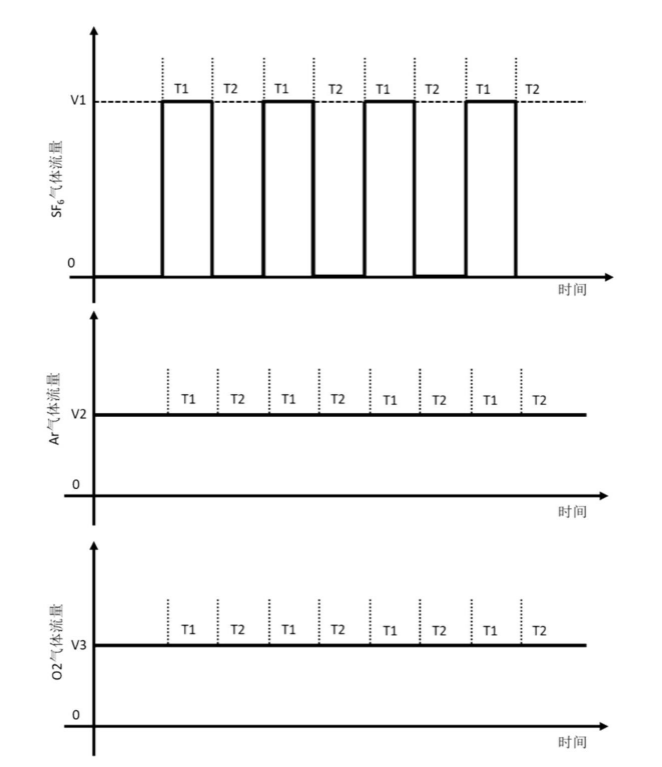

該專利詳細闡述了一種針對含硅有機介電層的高效刻蝕方法及相應的半導體工藝設備。它主要涉及到通過交替運用至少兩個刻蝕步驟來刻蝕含硅有機介電層。這兩個步驟分別為第一刻蝕步驟和第二刻蝕步驟。

2023-12-06 11:58:16 370

370

W刻蝕工藝中使用SF6作為主刻步氣體,并通過加入N2以增加對光刻膠的選擇比,加入O2減少碳沉積。在W回刻工藝中分為兩步,第一步是快速均勻地刻掉大部分W,第二步則降低刻蝕速率減弱負載效應,避免產生凹坑,并使用對TiN有高選擇比的化學氣體進行刻蝕。

2023-12-06 09:38:53 1536

1536 薄膜沉積技術主要分為CVD和PVD兩個方向。 PVD主要用來沉積金屬及金屬化合物薄膜,分為蒸鍍和濺射兩大類,目前的主流工藝為濺射。CVD主要用于介質/半導體薄膜,廣泛用于層間介質層、柵氧化層、鈍化層等工藝。

2023-12-05 10:25:18 994

994 [半導體前端工藝:第二篇] 半導體制程工藝概覽與氧化

2023-11-29 15:14:34 541

541

,二氧化碳的濃度一般在500到700 ppm。二氧化碳會在狹窄的空間內積聚,造成健康和安全隱患,二氧化碳能置換或耗盡氧氣,導致頭暈、神志不清、呼吸短促、失去知覺,甚至在不安全的濃度水平下窒息而死。 短期內,過高的二氧化碳濃度不會對人體產生太大的影響。但

2023-11-28 15:02:25 232

232

半導體前端工藝(第四篇):刻蝕——有選擇性地刻蝕材料,以創建所需圖形

2023-11-27 16:54:26 256

256

模組,其實就是把類似和相關的工序組成一個集合的概念,這樣就可以分配給相對的部門去負責,他們只做這一部分對應的工作。比如:刻蝕工藝工程師就專門做刻蝕這一部分工作,不要做薄膜的工作。

2023-11-25 15:08:25 3276

3276

對薄膜太陽能電池進行適當的后處理工藝是提高薄膜太陽能電池性能的重要手段之一,退火工藝作為一種常見的后處理工藝,可大幅度改善薄膜材料的結晶性、去除缺陷、調整相組成等,從而提高薄膜太陽能電池的光電轉換率

2023-11-23 08:33:12 303

303

氧化鋅的靈敏度、成本效益、環境兼容性、穩定性和集成能力,使其成為監測并降低二氧化碳排放的高效氣體傳感系統不可或缺的材料。

2023-11-21 12:31:43 265

265

在當今的高壓電力系統中,氧化鋅避雷器扮演著至關重要的角色。它的實用性在于能夠有效地保護電力設備免受雷電過電壓和操作過電壓的損害,從而確保了電力系統的穩定運行。 氧化鋅避雷器是一種特殊的避雷器,它采用

2023-11-16 15:59:36 167

167

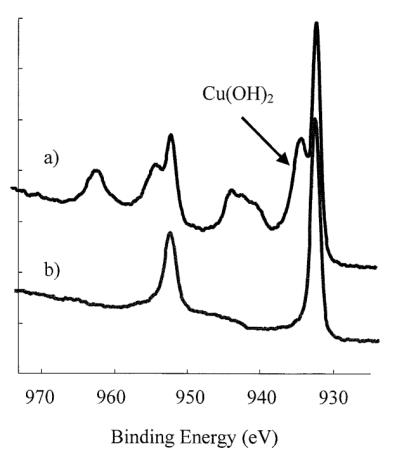

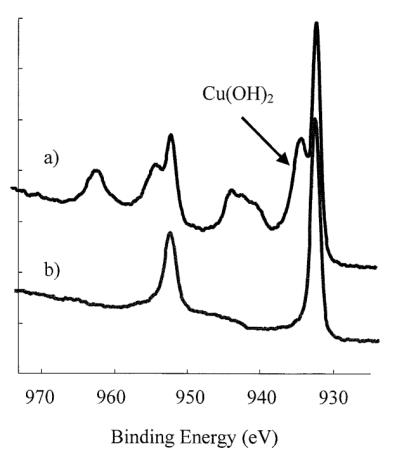

英思特研究了在低溫下用乙酸去除氧化銅。乙酸去除各種氧化銅,包括氧化亞銅、氧化銅和氫氧化銅,而不會侵蝕下面的銅膜。

2023-11-06 17:59:44 239

239

釩敏感材料采用微測輻射熱計技術與CMOS工藝兼容,能夠與CMOS讀出電路集成,可以基于半導體制造工藝大規模生產制造,屬于半導體熱敏薄膜,薄膜電阻溫度系數與電阻率都成正

2023-11-03 16:54:37 280

280

均勻性是衡量工藝在晶圓上一致性的一個關鍵指標。比如薄膜沉積工序中薄膜的厚度;刻蝕工序中被刻蝕材料的寬度,角度等等,都可以考慮其均勻性。

2023-11-01 18:21:13 608

608

在電力系統中,氧化鋅避雷器是一種重要的保護設備,用于防止雷電和電力系統過電壓對設備造成的損害。然而,如果氧化鋅避雷器被擊穿,它還能繼續使用嗎?首先,我們要了解什么是氧化鋅避雷器。氧化鋅避雷器是一種

2023-11-01 16:51:44 373

373 為了從根本上直接改善TOPcon太陽能電池的光電轉換率,電池廠商通常需要在太陽能電池片表面進行氧化退火工藝,從而使沉積的薄膜材料具有更高的方阻/電阻率,氧化退火工藝是影響TOPcon太陽能電池性能

2023-10-31 08:34:28 623

623

多孔性 氧化膜具有多孔的蜂窩狀結構,膜層的空隙率決定于電解液的類型和氧化的工藝條件。氧化膜的多孔結構,可使膜層對各種有機物、樹脂、地蠟、無機物、染料及油漆等表現出良好的吸附能力,可作為涂鍍層的底層,也可將氧化膜染成各種不同的顏色,提高金屬的裝飾效果。

2023-10-11 15:59:04 897

897

刻蝕(或蝕刻)是從晶圓表面去除特定區域的材料以形成相應微結構。但是,在目標材料被刻蝕時,通常伴隨著其他層或掩膜的刻蝕。

2023-10-07 14:19:25 2073

2073

在半導體制造中,刻蝕工序是必不可少的環節。而刻蝕又可以分為干法刻蝕與濕法刻蝕,這兩種技術各有優勢,也各有一定的局限性,理解它們之間的差異是至關重要的。

2023-09-26 18:21:00 3305

3305

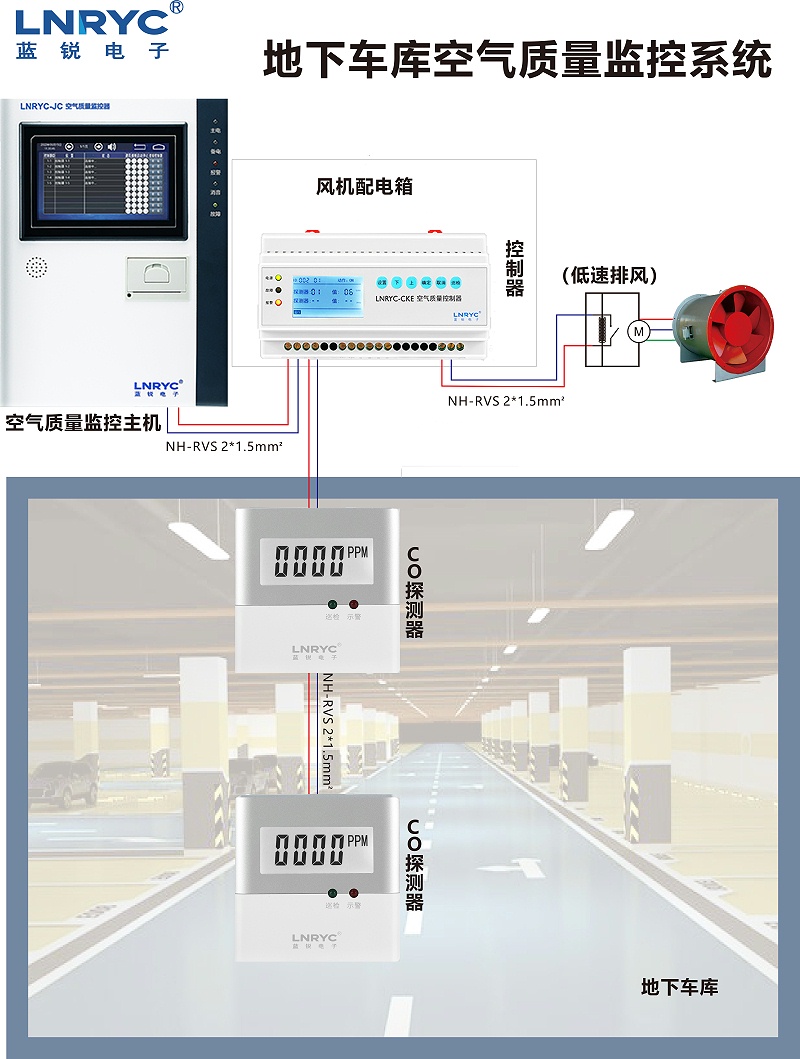

一氧化碳檢測儀是一種用于公共場所具有檢測及超限報警功能的儀器,能起到預防一氧化碳中毒的效果,使人們安全放心的工作。系統以單片機為核心,利用一氧化碳檢測傳感器檢測環境中的一氧化碳的濃度,并利用顯示器顯示當前的濃度值,同時可設定報警值,超過設定值時進行聲光報警。

2023-09-25 06:39:48

在半導體制程工藝中,有很多不同名稱的用于移除多余材料的工藝,如“清洗”、“刻蝕”等。如果說“清洗”工藝是把整張晶圓上多余的不純物去除掉,“刻蝕”工藝則是在光刻膠的幫助下有選擇性地移除不需要的材料,從而創建所需的微細圖案。半導體“刻蝕”工藝所采用的氣體和設備,在其他類似工藝中也很常見。

2023-09-24 17:42:03 996

996

濟南祥控自動化有限公司生產的工業級二氧化碳濃度檢測儀采用進口的二氧化碳傳感器,檢測精度高;具備空氣中零點自動校正功能,保證使用過程中不出現誤報現象;采用全量程溫度補償,確保測量數值長期穩定可靠;采用

2023-09-11 14:47:58 675

675

CVD因具有可控、高質量生長石墨烯的優點而引起國內外關注,據報道石墨烯薄膜可在多個襯底上生長,如Fe、Cu和Ni、 Pt等。研究表明,采用CVD工藝生長單層石墨烯,可實現晶粒可調、降低石墨烯固有強度、降低碳原料分解的能量屏障,一定條件下,CVD工藝能帶來可擴展、經濟、可重復且易于使用的優點。

2023-09-01 11:12:53 338

338

微弧氧化技術工藝流程

主要包含三部分:鋁基材料的前處理,微弧氧化,后處理三部分

其工藝流程如下:鋁基工件→化學除油→清洗→微弧氧化→清洗→后處理→成品檢驗。

2023-09-01 10:50:34 1235

1235

濕法刻蝕由于精度較差,只適用于很粗糙的制程,但它還是有優點的,比如價格便宜,適合批量處理,酸槽里可以一次浸泡25張硅片,所以有些高校和實驗室,還在用濕法做器件,芯片廠里也會用濕法刻蝕來顯露表面缺陷(defect),腐蝕背面多晶硅。

2023-08-28 09:47:44 890

890

光刻蝕(Photolithography)是一種在微電子和光電子制造中常用的加工技術,用于制造微細結構和芯片元件。它的基本原理是利用光的化學和物理作用,通過光罩的設計和控制,將光影投射到光敏材料上,形成所需的圖案。

2023-08-24 15:57:42 2270

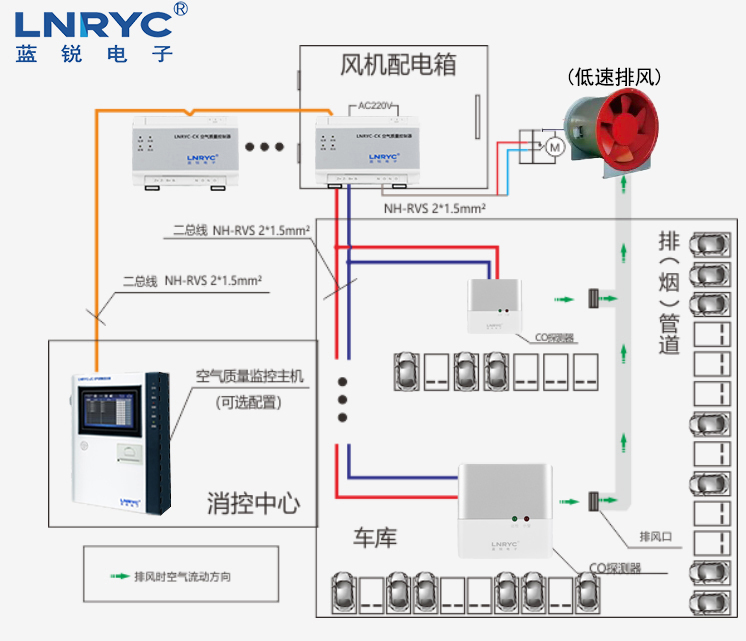

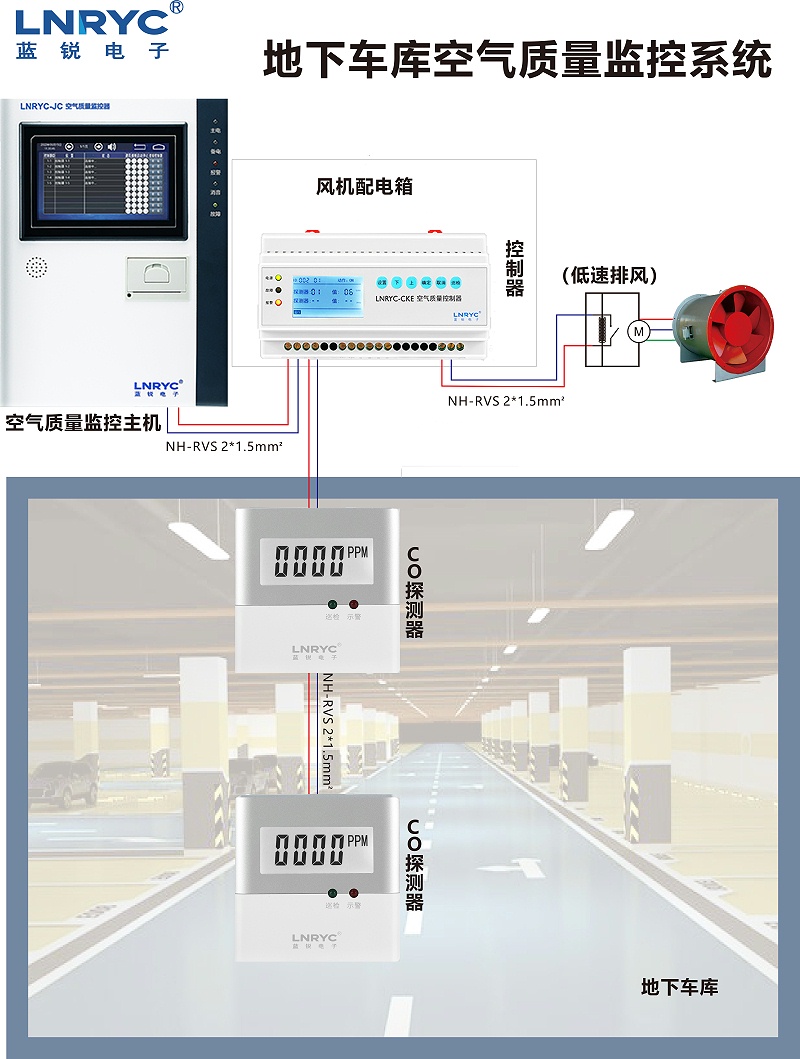

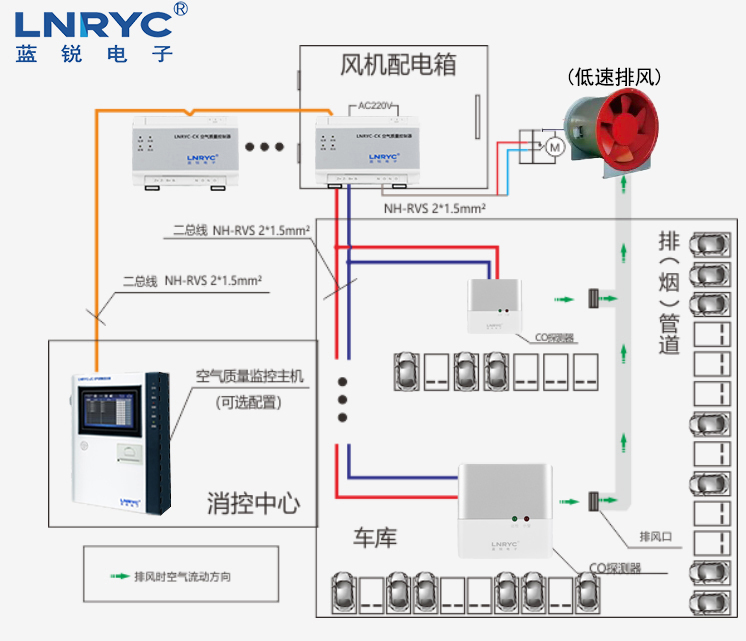

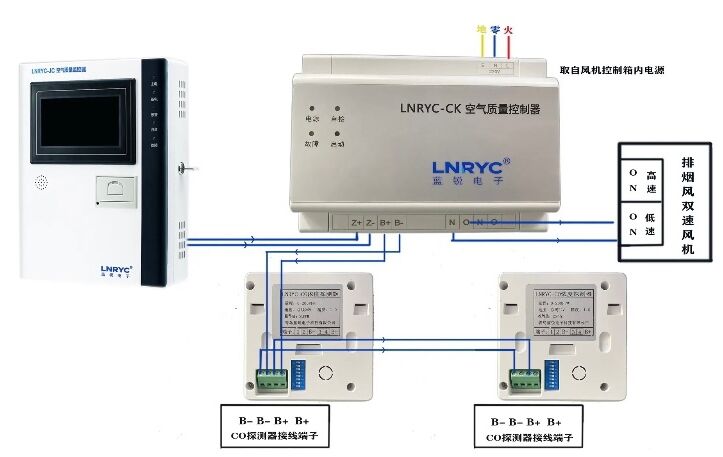

2270 關鍵詞:地下車庫、一氧化碳、一氧化碳監測系統 安裝地下車庫一氧化碳監測的目的:一氧化碳濃度超標情況下保證地下停車場內一氧化碳濃度低于危害水平,屬于安全考慮,能保證空氣質量。 車庫一氧化碳濃度探測器

2023-08-24 10:40:00 336

336

二氧化氮,化學式為NO2,一種棕紅色氣體。在常溫下(0~21.5℃)二氧化氮與四氧化二氮混合而共存。有毒、有刺激性。溶于濃硝酸中而生成發煙硝酸。能疊合成四氧化二氮。與水作用生成硝酸和一氧化

2023-08-18 11:14:59 290

290 PVP可以在刻蝕過程中形成一層保護性的膜,降低刻蝕劑對所需刻蝕材料的腐蝕作用。它可以填充材料表面的裂縫、孔洞和微小空隙,并防止刻蝕劑侵入。這樣可以減少不需要的蝕刻或損傷,提高刻蝕的選擇性。

2023-08-17 15:39:39 2855

2855 在半導體制程中,移除殘余材料的“減法工藝”不止“刻蝕”一種,引入其他材料的“加法工藝”也非“沉積”一種。比如,光刻工藝中的光刻膠涂敷,其實也是在基底上形成各種薄膜;又如氧化工藝中晶圓(硅)氧化,也需要在基底表面添加各種新材料。那為什么唯獨要強調“沉積”工藝呢?

2023-08-17 15:33:27 370

370

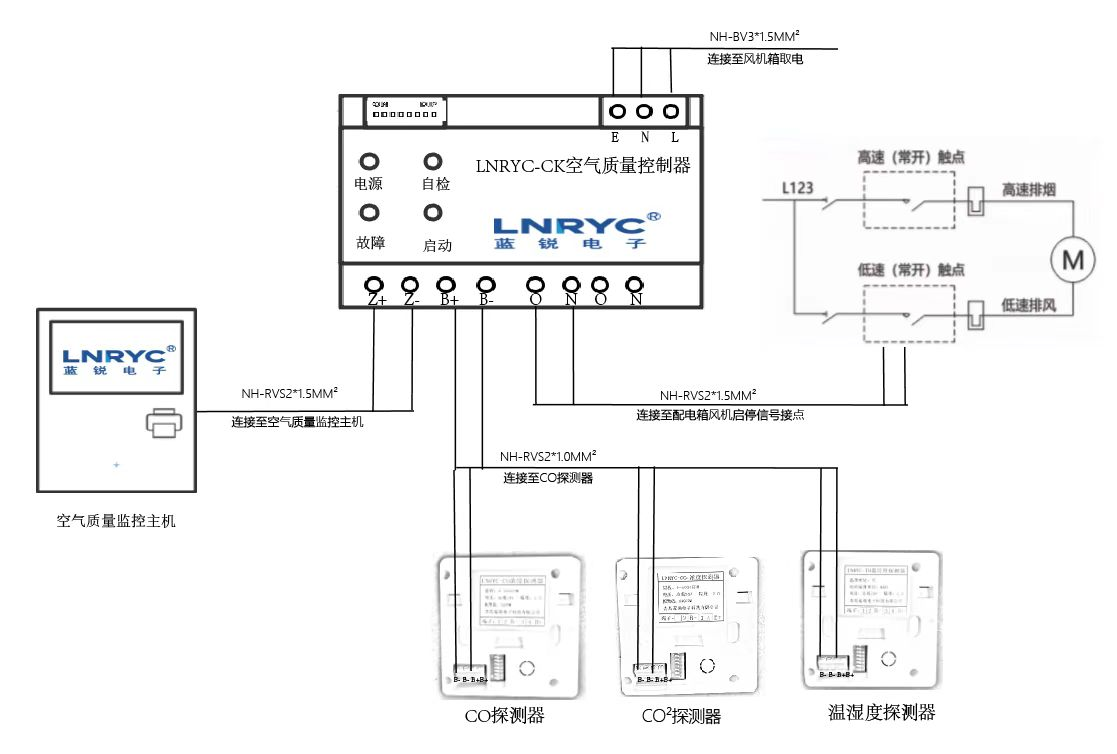

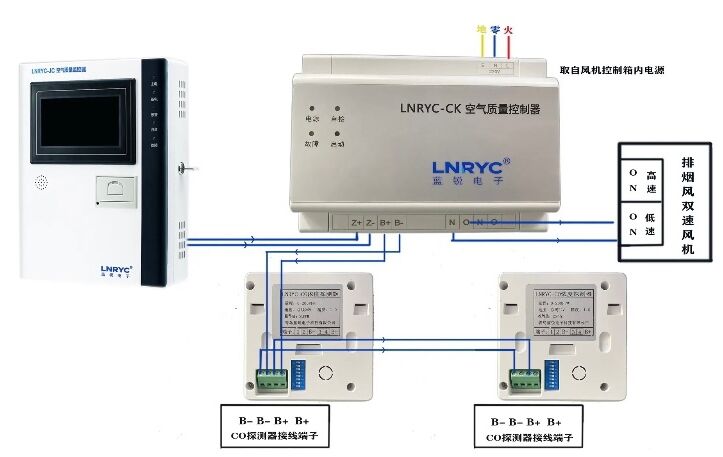

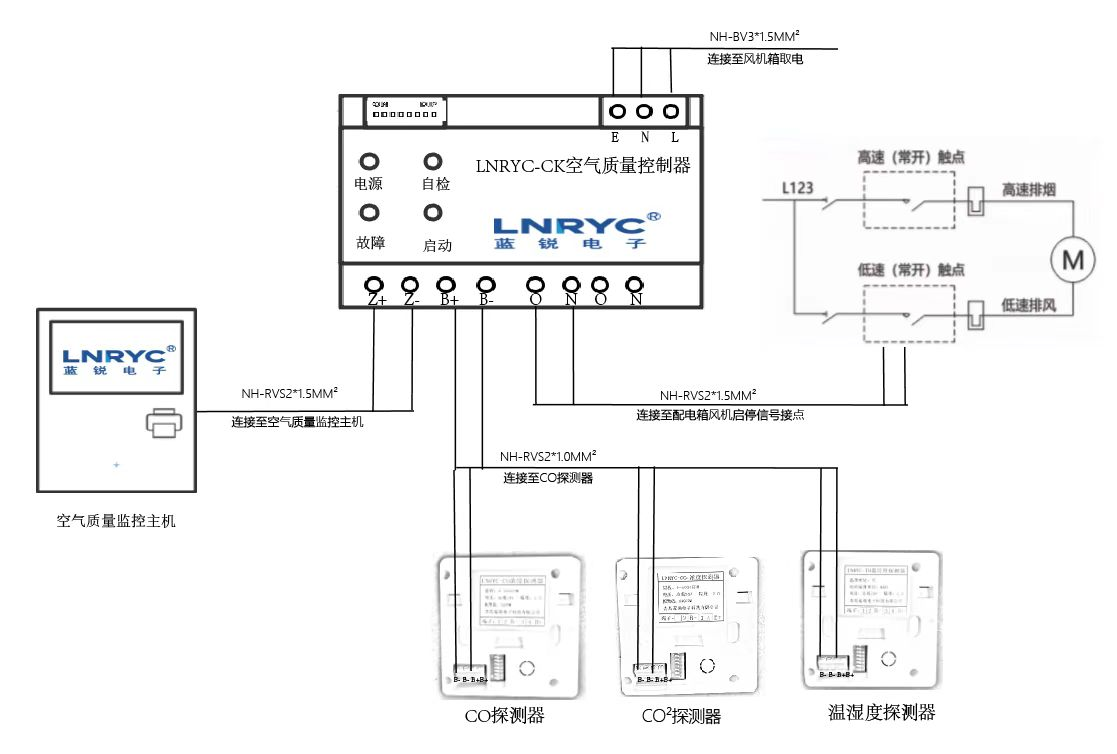

關鍵詞:車庫一氧化碳濃度監控系統、原理 車庫一氧化碳濃度監控系統主要由CO探測器,CO控制器,CO監控主機組成。 車庫一氧化碳濃度監控系統通過CO探測器實時監控區域內的一氧化碳濃度,當濃度超過CO

2023-08-15 17:18:07 547

547

K 系列壓敏電阻器氧化鋅壓敏電阻器是以氧化鋅為主要材料制造的半導體無極性電子陶瓷元件。當施加在壓敏電 阻器兩端的電壓達到某一閥值時,壓敏電阻器的電阻值迅猛變小,從而在電子(電力)線路

2023-08-12 16:12:23

在半導體前端工藝第三篇中,我們了解了如何制作“餅干模具”。本期,我們就來講講如何采用這個“餅干模具”印出我們想要的“餅干”。這一步驟的重點,在于如何移除不需要的材料,即“刻蝕(Etching)工藝”。

2023-08-10 15:06:10 506

506 在電力系統中,保護設備免受雷電沖擊和過電壓的影響至關重要。氧化鋅避雷器作為一種先進的過電壓保護設備,經歷了漫長的發展過程,并在不斷地進步和完善。 氧化鋅避雷器的發展可以追溯到19世紀末期,當時

2023-08-09 14:27:41 301

301 一、產品簡介避雷器在線檢測儀用于氧化鋅[MOA]泄漏電流的測量分析。主要是用于測量阻性電流,3~7次諧波電流,從而分析氧化鋅老化和受潮的程度。是檢測氧化鋅避雷器運行中的各項交流電氣參數

2023-08-09 10:49:13

一、產品簡介HM6020氧化鋅避雷器測試儀是專門用于檢測10kV及以下電力系統用無間隙氧化鋅避雷器MOA閥電間接觸不良的內部缺陷,測量MOA的直流參考電壓(U1mA)和0.75 U1mA

2023-08-08 11:01:16

氧化鋅避雷器是一種用于保護電氣設備免受電壓過載損害的裝置。其工作原理是基于氧化鋅的電阻特性,在高壓下阻值迅速增加,從而限制電流,使電氣設備免受過度電壓的損害。以下將詳細介紹氧化鋅避雷器的用途

2023-08-07 15:43:24 723

723 一、產品簡介HM6010氧化鋅避雷器測試儀以先進的微型計算機為控制部件,全智能操作,具有抗干擾能力強,測量準確可靠,功能強大,操作方便等優點,是現場和實驗室檢測氧化鋅避雷器各項交流電

2023-08-07 11:25:59

刻蝕(Etching)的目的是在材料表面上刻出所需的圖案和結構。刻蝕的原理是利用化學反應或物理過程,通過移除材料表面的原子或分子,使材料發生形貌變化。

2023-08-01 16:33:38 3908

3908 電子發燒友網報道(文/周凱揚)在半導體制造的各路工序中,尤其是前道工序中,技術難度最大的主要三大流程當屬光刻、刻蝕和薄膜沉積了。這三大工藝的先進程度直接決定了晶圓廠所能實現的最高工藝節點,所用產品

2023-07-30 03:24:48 1556

1556

據介紹,在器件制造過程中,由于薄膜沉積、光刻、刻蝕和化學機械拋光等工藝步驟的大幅增長,在晶圓的邊緣造成了不可避免的副產物及殘留物堆積,這些晶邊沉積的副產物及殘留物驟增導致的缺陷風險成為產品良率的嚴重威脅。

2023-07-19 15:02:26 607

607 CMP 主要負責對晶圓表面實現平坦化。晶圓制造前道加工環節主要包括7個相互獨立的工藝流程:光刻、刻蝕、薄膜生長、擴散、離子注入、化學機械拋光、金屬化 CMP 則主要用于銜接不同薄膜工藝,其中根據工藝

2023-07-18 11:48:18 3030

3030

氧腐蝕的發生,我們可以采取一些措施,如涂覆防腐涂料、使用不易氧化的金屬材料、控制氧氣濃度等。下面工采網小編通過本文看看氧腐蝕控制氧氣濃度的應用解決方案。 吸氧腐蝕控制是一種常見的腐蝕控制方法,在實際應用中,吸

2023-07-18 11:29:14 305

305

第一種是間歇式刻蝕方法(BOSCH),即多次交替循環刻蝕和淀積工藝,刻蝕工藝使用的是SF6氣體,淀積工藝使用的是C4F8氣體

2023-07-14 09:54:46 3213

3213

關鍵詞:地下車庫、安裝、一氧化碳濃度監控系統 地下車庫是封閉或者半封閉的建筑,由于汽車的尾氣排放,加上空氣流通不流通,就會 一氧化碳等有害氣體,這些氣體對人體組織缺氧,心臟和大腦的影響顯著。地下

2023-07-03 11:43:59 559

559

在半導體制程中,移除殘余材料的“減法工藝”不止“刻蝕”一種,引入其他材料的“加法工藝”也非“沉積”一種。比如,光刻工藝中的光刻膠涂敷,其實也是在基底上形成各種薄膜;又如氧化工藝中晶圓(硅)氧化,也需要在基底表面添加各種新材料。那為什么唯獨要強調“沉積”工藝呢?

2023-06-29 16:58:37 404

404

在上一篇文章,我們介紹了光刻工藝,即利用光罩(掩膜)把設計好的電路圖形繪制在涂覆了光刻膠的晶圓表面上。下一步,將在晶圓上進行刻蝕工藝,以去除不必要的材料,只保留所需的圖形。

2023-06-28 10:04:58 843

843

圖案化工藝包括曝光(Exposure)、顯影(Develope)、刻蝕(Etching)和離子注入等流程。其中,刻蝕工藝是光刻(Photo)工藝的下一步,用于去除光刻膠(Photo Resist

2023-06-26 09:20:10 816

816

在半導體制程工藝中,有很多不同名稱的用于移除多余材料的工藝,如“清洗”、“刻蝕”等。如果說“清洗”工藝是把整張晶圓上多余的不純物去除掉,“刻蝕”工藝則是在光刻膠的幫助下有選擇性地移除不需要的材料,從而創建所需的微細圖案。半導體“刻蝕”工藝所采用的氣體和設備,在其他類似工藝中也很常見。

2023-06-15 17:51:57 1177

1177

關鍵詞:地下車庫、一氧化碳濃度監控系統、一氧化碳探測器、接線 地下車庫一氧化碳的產生主要源自于汽車發動機,由于燃燒不充分會產生大量的尾氣,車庫屬于密閉環境空氣流通不好,車輛尾氣不易排出,尾氣中含有

2023-06-13 15:09:18 1942

1942

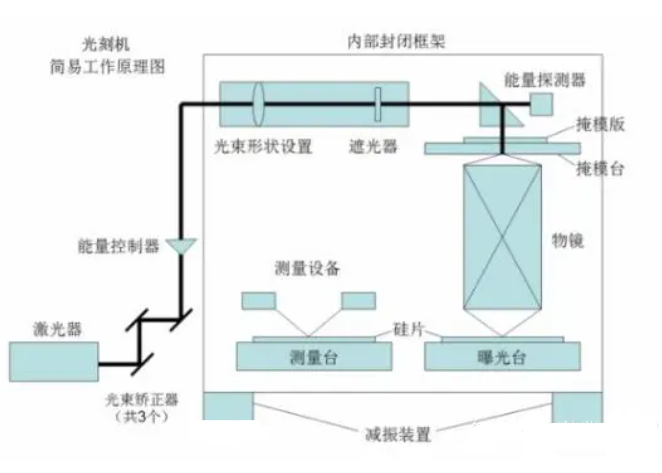

光刻機是芯片制造中最復雜、最昂貴的設備。芯片制造可以包括多個工藝,如初步氧化、涂光刻膠、曝光、顯影、刻蝕、離子注入。這個過程需要用到的設備種類繁多,包括氧化爐、涂膠顯影機、光刻機、薄膜沉積設備、刻蝕

2023-06-12 10:13:33 4452

4452

關鍵詞:地下車庫、一氧化碳濃度監控系統、節能 在車庫CO濃度監控系統還沒有設計出來并推廣之前,在業內普諞的調節車庫CO濃度的方式是定時開啟排風機。這種方式在高峰期確實能有效的降低CO濃度,但是高峰期

2023-06-09 15:24:48 202

202

光刻工藝后,在硅片或晶圓上形成了光刻膠的圖形,下一步就是刻蝕。

2023-06-08 10:52:35 3318

3318

刻蝕硅,硅的均勻剝離,同時帶走表面顆粒。隨著器件尺寸縮減會引入很多新材料(如高介電常數和金屬柵極),那么在后柵極制程,多晶硅的去除常用氫氧化氨或四甲基羥胺(TMAH)溶液,制程關鍵是控制溶液的溫度和濃度,以調整刻蝕對多晶硅和其他材料的選擇比。

2023-06-05 15:10:01 1597

1597 薄膜電容是指將金屬膜或半導體薄膜沉積在絕緣基板上,然后制成電容器。這種電容器具有結構簡單、體積小、重量輕、可靠性高等特點,被廣泛應用于電子設備領域。本文將從薄膜電容的基本原理、制備工藝、應用領域等方面進行介紹。

2023-05-31 14:24:55 2880

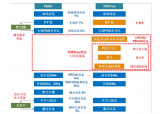

2880 集成電路前道工藝及對應設備主要分八大類,包括光刻(光刻機)、刻蝕(刻蝕機)、薄膜生長(PVD-物理氣相沉積、CVD-化學氣相沉積等薄膜設備)、擴散(擴散爐)、離子注入(離子注入機)、平坦化(CMP設備)、金屬化(ECD設備)、濕法工藝(濕法工藝設備)等。

2023-05-30 10:47:12 1131

1131

。 PVD 沉積工藝在半導體制造中用于為各種邏輯器件和存儲器件制作超薄、超純金屬和過渡金屬氮化物薄膜。最常見的 PVD 應用是鋁板和焊盤金屬化、鈦和氮化鈦襯墊層、阻擋層沉積和用于互連金屬化的銅阻擋層種子沉積。 PVD 薄膜沉積工藝需要一個高真空的平臺,在

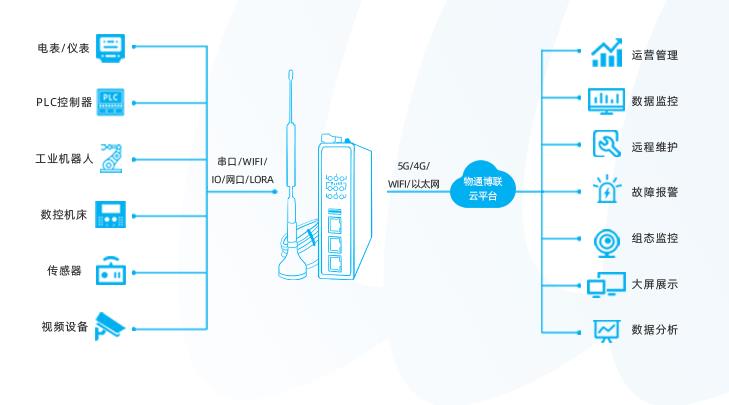

2023-05-26 16:36:51 1749

1749 氧化鋅揮發窯是化工行業中廣泛應用的生產設備,作為一種高溫下運行的大型設備,保證設備安穩定全運行、節能減排十分重要。 通過傳感器與工業物聯網的結合,物通博聯推出一套氧化鋅揮發窯在線監測系統,可以連接

2023-05-22 10:40:28 227

227

MOV(Metal Oxide Varistors)即金屬氧化物壓敏電阻,以氧化鋅為主體,摻雜多種金 屬氧化物,采用典型的電子陶瓷工藝制成的多晶半導體陶瓷元器件。

2023-05-15 12:25:54 3236

3236

薄膜陶瓷基板一般采用磁控濺射、真空蒸鍍等工藝直接在陶瓷基片表面沉積金屬層。通過光刻、顯影、刻蝕、電鍍等工藝,將金屬層圖形化制備成特定的線路及膜層厚度。通常,薄膜陶瓷基板表面金屬層厚度較小 (一般小于 4μm)。薄膜陶瓷基板可制備高精密圖形 (線寬/線距小于 10 μm、精度±1μm)。

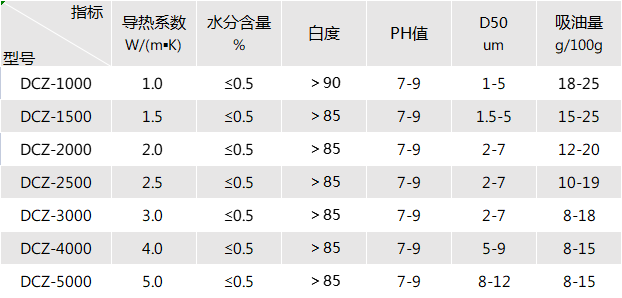

2023-05-15 10:18:56 591

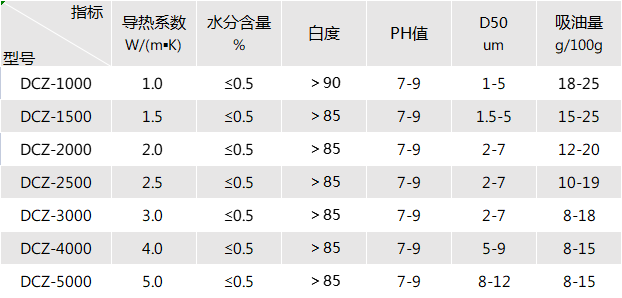

591 導熱填料顧名思義就是添加在基體材料中用來增加材料導熱系數的填料,常用的導熱填料有氧化鋁、氧化鎂、氧化鋅、氮化鋁、氮化硼、碳化硅等;其中,尤以微米級氧化鋁、硅微粉為主體,納米氧化鋁,氮化物做為高導熱

2023-05-05 14:04:03 984

984

圖案化工藝包括曝光(Exposure)、顯影(Develope)、刻蝕(Etching)和離子注入等流程。

2023-04-28 11:24:27 1073

1073

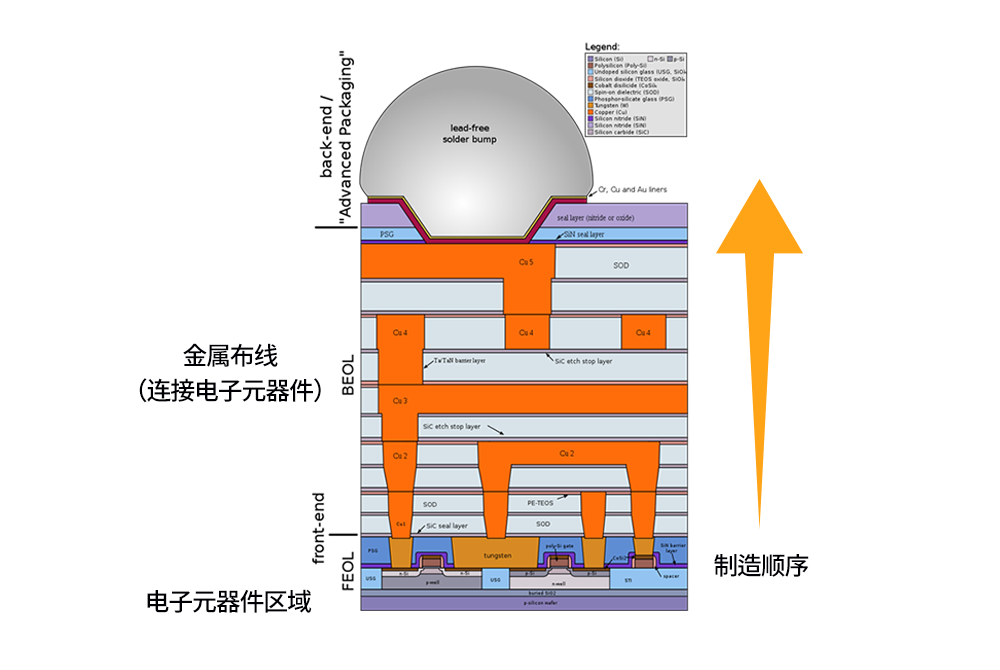

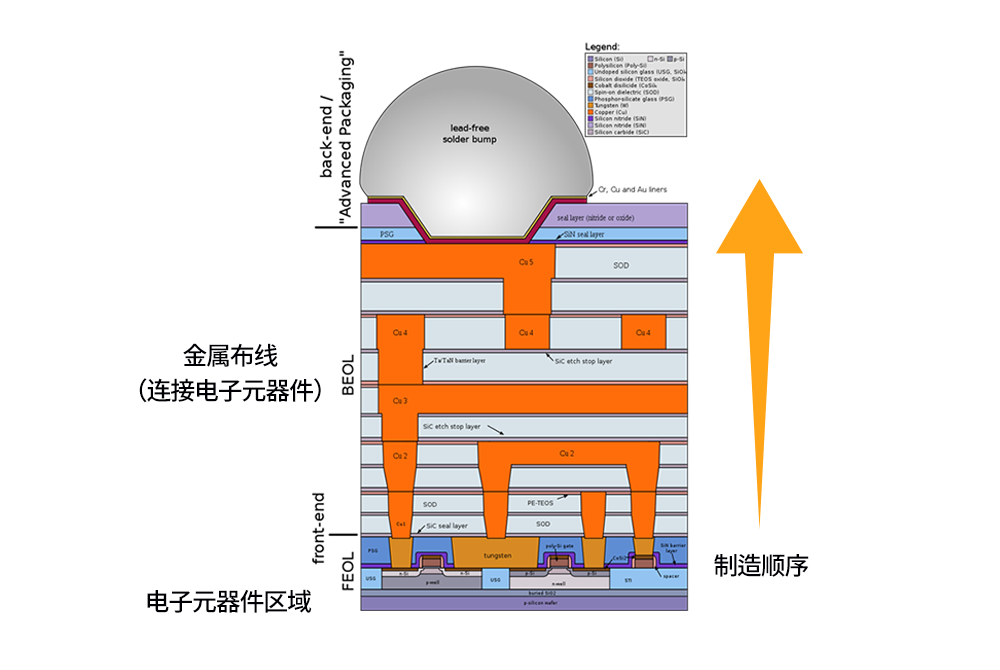

經過氧化、光刻、刻蝕、沉積等工藝,晶圓表面會形成各種半導體元件。半導體制造商會讓晶圓表面布滿晶體管和電容(Capacitor);

2023-04-28 10:04:52 532

532

本篇要講的金屬布線工藝,與前面提到的光刻、刻蝕、沉積等獨立的工藝不同。在半導體制程中,光刻、刻蝕等工藝,其實是為了金屬布線才進行的。在金屬布線過程中,會采用很多與之前的電子元器件層性質不同的配線材料(金屬)。

2023-04-25 10:38:49 986

986

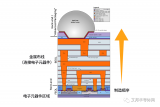

書籍:《炬豐科技-半導體工藝》 文章:金屬氧化物半導體的制造 編號:JFKJ-21-207 作者:炬豐科技 概述 CMOS制造工藝概述 ? CMOS制造工藝流程 ? 設計規則 ? 互補金屬氧化

2023-04-20 11:16:00 247

247

壓力主要控制刻蝕均勻性和刻蝕輪廓,同時也能影響刻蝕速率和選擇性。改變壓力會改變電子和離子的平均自由程(MFP),進而影響等離子體和刻蝕速率的均勻性。

2023-04-17 10:36:43 1922

1922 近日,上海玻璃鋼研究院有限公司的高級工程師趙中堅沿著該思路,以純纖維狀α-Si3N4粉為主要原料,通過添加一定比例氧化物燒結助劑,經冷等靜壓成型和氣氛保護無壓燒結工藝燒結制備出了能充分滿足高性能導彈天線罩使用要求的多孔氮化硅陶瓷。

2023-04-16 10:30:46 1274

1274 金屬刻蝕具有良好的輪廓控制、殘余物控制,防止金屬腐蝕很重要。金屬刻蝕時鋁中如果 有少量銅就會引起殘余物問題,因為Cu Cl2的揮發性極低且會停留在晶圓表面。

2023-04-10 09:40:54 2330

2330 DRAM柵工藝中,在多晶硅上使用鈣金屬硅化物以減少局部連線的電阻。這種金屬硅化物和多晶硅的堆疊薄膜刻蝕需要增加一道工藝刻蝕W或WSi2,一般先使用氟元素刻蝕鈞金屬硅化合物層,然后再使用氯元素刻蝕多晶硅。

2023-04-07 09:48:16 2198

2198 產品介紹:多孔質超高分子量聚乙烯薄膜是WERS微爾斯新材料事業部開發的特殊微孔薄膜產品。首先將超高分子量聚乙烯粉末制成多孔成形體、然后通過對成形體的切削制成UHMW-PE多孔質薄膜。該產品不單保持

2023-03-30 13:51:48 719

719

氧化鋅壓敏電阻以氧化鋅(ZnO)為基料,加入Bi2O3、Co2O3、MnCO3等多種金屬氧化物混合,經過高溫燒結、焊接、包封等多重工序制成的電阻器

2023-03-30 10:26:26 1973

1973 FinFET三維器件也可以用體硅襯底制作,這需要更好地控制單晶硅刻蝕工藝,如CD、深度和輪廓。

2023-03-30 09:39:18 2459

2459 薄膜電阻應用于光通訊、 射頻微波毫米波通訊,如放大、耦合、衰減、濾波等模塊電路。電阻網絡應用于微波集成電路中,能夠縮小電路板空間,降低元器件成本。薄膜衰減器應用于光通訊、微波集成電路模塊,其

2023-03-28 14:19:17

電子成品組裝薄膜面板制作工藝對比

2023-03-24 15:37:39 631

631

電子發燒友App

電子發燒友App

評論