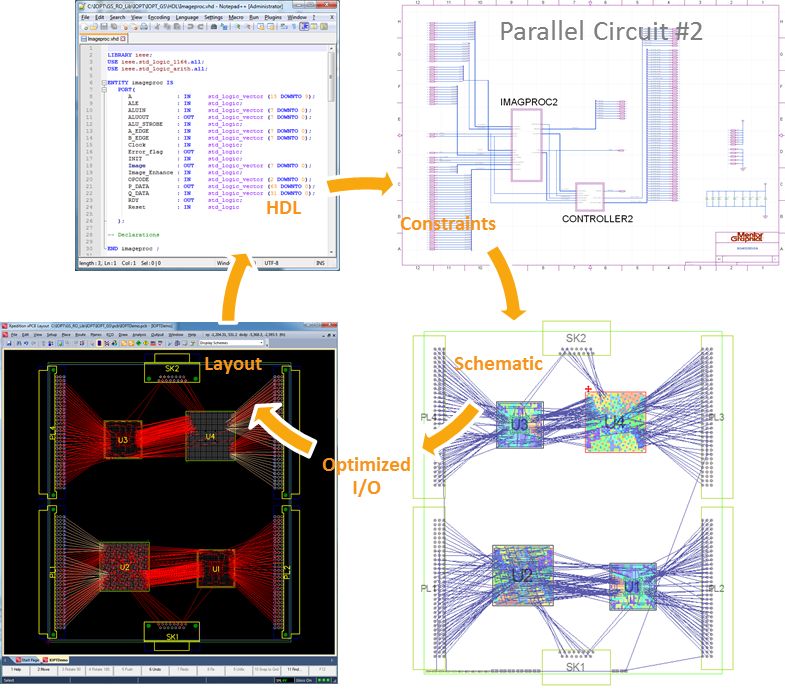

隨著電子產品的集成性及復雜度呈指數型增長,加上越來越苛刻的研發周期要求,給各種設計公司提出了難題。這其中FPGA的設計挑戰尤為突出。不斷增加的管腳數量,同一PCB上的多顆FPGA之間互連等等,面對這些挑戰如果還依照以往的手動式設計流程,勢必會在激烈的市場競爭中失去優勢!Mentor公司針對這種實際應用情況,提出了集成式管腳優化方案,根據信號連接關系及器件位置擺放信息,自動實現IO管腳優化,在保證產品質量的前提下,高效完成FPGA設計及優化工作,在最短的時間內使產品順利上市!

4大技術優勢:

1縮減設計成本:

減少過孔數量

節省PCB疊層數量

減少生產制造迭代次數

2縮短設計周期:

減少設計迭代次數

提升FPGA布線效率

快速優化IO管腳,自動生成器件symbol

3減少設計失誤:

杜絕器件symbol設計失誤

避免手動更換IO管腳而造成的失誤

4提高產品質量:

減少布線長度,提升信號質量

-

FPGA

+關注

關注

1643文章

21960瀏覽量

614065 -

pcb

+關注

關注

4352文章

23417瀏覽量

406738

原文標題:不容錯過的研討會 | 復雜FPGA高效設計及優化方法

文章出處:【微信號:gh_1a93bb3ab6f3,微信公眾號:Mentor明導PADS】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

工控一體機多線程任務調度優化:聚徽分享破解工業復雜流程高效協同密碼

VirtualLab 應用:傾斜光柵的參數優化及公差分析

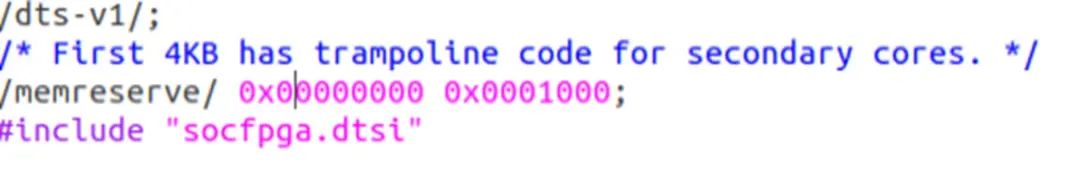

Linux系統中通過預留物理內存實現ARM與FPGA高效通信的方法

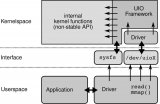

使用Linux UIO框架實現ARM和FPGA的高效通信

FPGA在磁致伸縮位移傳感器中的應用

焊接技術流程優化方法

使用 RISC-V 進行高效數據處理的方法

如何優化FPGA設計的性能

AI大模型的性能優化方法

解鎖SoC “調試”挑戰,開啟高效原型驗證之路

復雜FPGA高效設計及優化方法

復雜FPGA高效設計及優化方法

評論