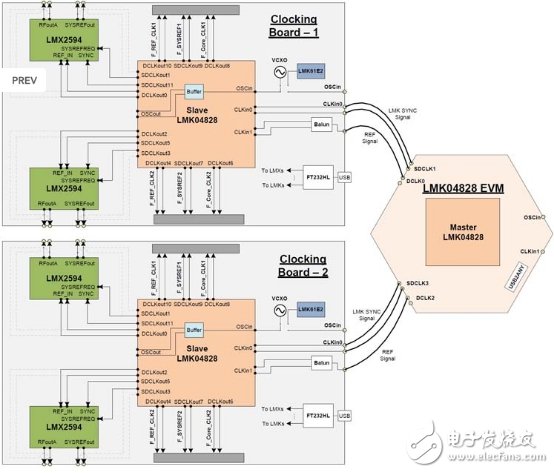

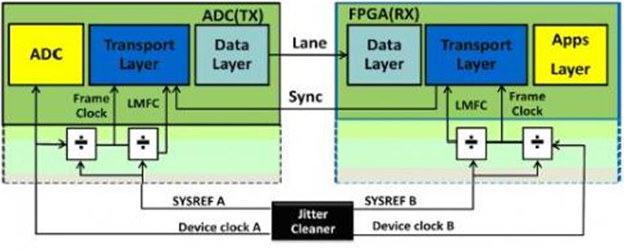

高速多通道應用需要低噪聲、可擴展且可進行精確通道間偏差調節的時鐘解決方案,以實現最佳系統 SNR、SFDR 和 ENOB。此參考設計使用一個主時鐘器件和多個從時鐘器件,支持高通道數 JESD204B 同步時鐘。此設計可提供多通道 JESD204B 時鐘,采用 TI LMK04828 時鐘抖動清除器和帶有集成式 VCO 的 LMX2594 寬帶 PLL,能夠實現低于 10ps 的時鐘間偏差。此設計經過 TI ADC12DJ3200 EVM 在 3GSPS 環境中檢測,具有改善的 SNR 性能,通道間偏差低于 50ps。本文對所有重要設計理論都進行了闡釋說明,可指導用戶完成器件選擇流程和設計優化。最后,此設計還包含原理圖、板布局、硬件測試和測試結果。

特性

·高頻 (GSPS) 采樣時鐘生成

·符合 JESD204B 標準、高通道數、可擴展的時鐘解決方案

·可配置的相位同步可在多通道系統中實現低偏差

·支持 TI 高速轉換器和采集卡(ADC12DJ3200EVM、TSW14J56/TSW14J57)

TIDA-01023 High Channel Count JESD204B Clock Generation Reference Design for RADAR and 5G Wireless Testers Board Image

TIDA-01023 High Channel Count JESD204B Clock Generation Reference Design for RADAR and 5G Wireless Testers Board Setup Image

TIDA-01023 High Channel Count JESD204B Clock Generation Reference Design for RADAR and 5G Wireless Testers Block Diagram Image

-

雷達

+關注

關注

50文章

3076瀏覽量

119409 -

無線測試儀

+關注

關注

0文章

22瀏覽量

9156

發布評論請先 登錄

JESD204B的系統級優勢

5G無線測試儀高通道數JESD204B時鐘生成參考設計

高通道數JESD204B菊鏈可擴展時鐘解決方案

串行LVDS和JESD204B的對比

JESD204B串行接口時鐘的優勢

FPGA高速數據采集設計之JESD204B接口應用場景

如何采用系統參考模式設計JESD204B時鐘

JESD204B協議介紹

JESD204B標準及演進歷程

JESD204B在時鐘方面的設計及其驗證實現

JESD204B時鐘網絡原理概述

JESD204B使用說明

用于雷達和5G無線測試儀的JESD204B時鐘生成參考設計

用于雷達和5G無線測試儀的JESD204B時鐘生成參考設計

評論