半導體的支持工藝和CPU的性能關系就大了,它關系到CPU內能塞進多少個晶體管,還有CPU所能達到的頻率還有它的功耗,1978年Intel推出了第一顆CPU——8086,它采用3μm(3000nm)工藝生產(chǎn),只有29000個晶體管,工作頻率也只有5MHz。

而現(xiàn)在晶體管數(shù)量最多的單芯片CPU應該是Intel的28核Skylake-SP Xeon處理器,它擁有超過80億個晶體管,而頻率最高的則是Core i9-9900K,最大睿頻能到5GHz,他們都是用Intel的14nm工藝生產(chǎn)的。

Intel 14nm工藝在性能、功耗方面繼續(xù)改進

CPU的生產(chǎn)是需要經(jīng)過7個工序的,分別是:硅提純,切割晶圓,影印,蝕刻,重復、分層,封裝,測試, 而當中的蝕刻工序是CPU生產(chǎn)的重要工作,也是重頭技術,簡單來說蝕刻就是用激光在硅晶圓制造晶體管的過程,蝕刻這個過程是由光完成的,所以用于蝕刻的光的波長就是該技術提升的關鍵,它影響著在硅晶圓上蝕刻的最小尺寸,也就是線寬。

現(xiàn)在半導體工藝上所說的多少nm工藝其實是指線寬,也就是芯片上的最基本功能單位門電路的寬度,因為實際上門電路之間連線的寬度同門電路的寬度相同,所以線寬可以描述制造工藝。縮小線寬意味著晶體管可以做得更小、更密集,而且在相同的芯片復雜程度下可使用更小的晶圓,于是成本降低了。

更先進半導體制造工藝另一個重要優(yōu)點就是可以提升工作頻率,縮減元件之間的間距之后,晶體管之間的電容也會降低,晶體管的開關頻率也得以提升,從而整個芯片的工作頻率就上去了。

另外晶體管的尺寸縮小會減低它們的內阻,所需導通電壓會降低,這代表著CPU的工作電壓會降低,所以我們看到每一款新CPU核心,其電壓較前一代產(chǎn)品都有相應降低。另外CPU的動態(tài)功耗損失是與電壓的平方成正比的,工作電壓的降低,可使它們的功率也大幅度減小。

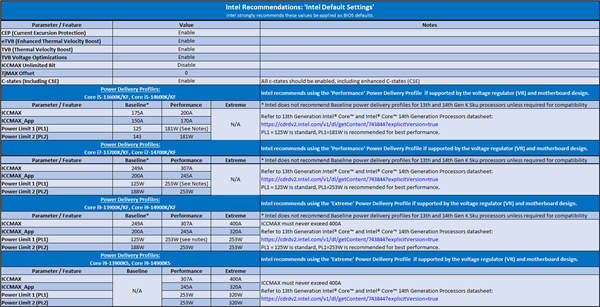

另外同種工藝的概率也是相當重要的,Intel自2015年14nm工藝投產(chǎn)以來已經(jīng)發(fā)展到了第三代,Intel一直在改進工藝,在不提升功耗的情況不斷提升性能,14nm++工藝比初代14nm工藝性能提升26%,或者功耗降低52%。

實際上AMD Ryzen處理器現(xiàn)在所用的12nm工藝本質上也只是GlobalFoundries的14nm工藝的改良版,也就是原計劃的14nm+,晶體管密度并沒有提升,但在性能方面有所改善,最高工作頻率提升了250MHz,而同頻下Vcore下降了50mV。

多年前Intel對自家半導體工藝的進展預期,此處應該有個滑稽的表情

總的來說半導體工藝是決定各種集成電路性能、功耗的關鍵,線寬的縮小晶體管密度得以提升從而降低了成本,其次就是晶體管頻率提高,性能提升而功耗降低。

-

芯片

+關注

關注

459文章

52331瀏覽量

438351 -

intel

+關注

關注

19文章

3494瀏覽量

188178

原文標題:CPU工藝與性能的關系探討

文章出處:【微信號:iawbs2016,微信公眾號:寬禁帶半導體技術創(chuàng)新聯(lián)盟】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

廣明源172nm晶圓光清洗方案概述

三星在4nm邏輯芯片上實現(xiàn)40%以上的測試良率

Cadence UCIe IP在Samsung Foundry的5nm汽車工藝上實現(xiàn)流片成功

突破14nm工藝壁壘:天準科技發(fā)布TB2000晶圓缺陷檢測裝備

千億美元打水漂,傳三星取消1.4nm晶圓代工工藝

千億美元打水漂,傳三星取消1.4nm晶圓代工工藝?

英特爾18A與臺積電N2工藝各有千秋

三星重啟1b nm DRAM設計,應對良率與性能挑戰(zhàn)

臺積電分享 2nm 工藝深入細節(jié):功耗降低 35% 或性能提升15%!

Cortex-A55 處理器到底什么來頭?創(chuàng)龍教儀一文帶您了解

蘋果iPhone 17或沿用3nm技術,2nm得等到2026年了!

臺積電產(chǎn)能爆棚:3nm與5nm工藝供不應求

TLC2252和TLC2254功耗和性能方面有何不同?

Intel:13/14代酷睿補丁幾乎無損性能!未來所有產(chǎn)品都安全

Intel 14nm工藝在性能、功耗方面繼續(xù)改進

Intel 14nm工藝在性能、功耗方面繼續(xù)改進

評論