來源:IEEE

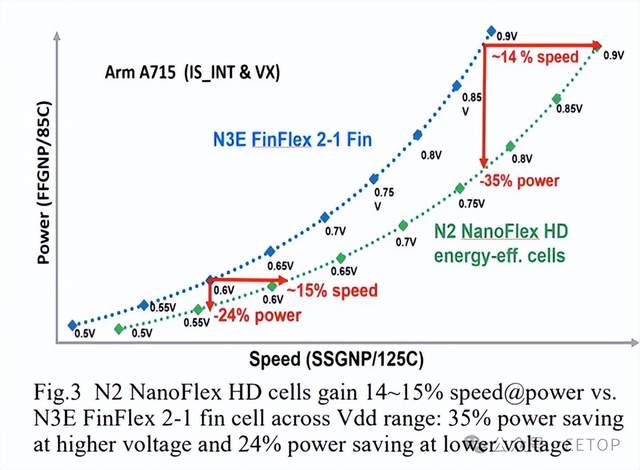

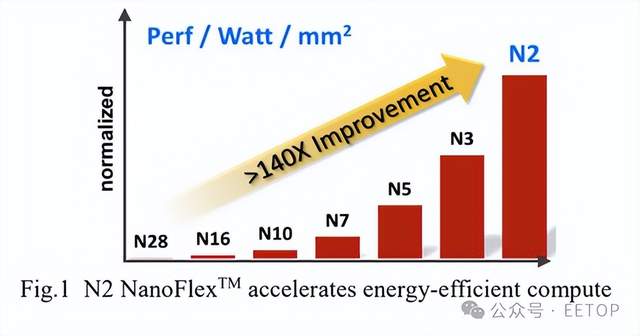

臺積電在本月早些時候于IEEE國際電子器件會議(IEDM)上公布了其N2(2nm級)制程的更多細節(jié)。該新一代工藝節(jié)點承諾實現(xiàn)24%至35%的功耗降低或15%的性能提升(在相同電壓下),同時其晶體管密度是上一代3nm制程的1.15倍。這些顯著優(yōu)勢主要得益于臺積電的全柵極(Gate-All-Around, GAA)納米片晶體管、N2 NanoFlex設(shè)計技術(shù)協(xié)同優(yōu)化(DTCO)能力,以及IEDM會上詳述的其他創(chuàng)新。

全柵極納米片晶體管允許設(shè)計師調(diào)整通道寬度,以在性能和功耗效率之間實現(xiàn)平衡。此外,臺積電的N2制程引入了N2 NanoFlex DTCO,使設(shè)計師能夠開發(fā)面積最小且功耗效率優(yōu)化的短單元,或者性能優(yōu)化的高單元。這項技術(shù)還包括六種閾值電壓級別(6-Vt),覆蓋200mV范圍,通過臺積電第三代基于偶極子的整合技術(shù)實現(xiàn),涵蓋n型和p型偶極子。

N2的技術(shù)亮點:

N2在工藝和器件層面引入的創(chuàng)新不僅通過優(yōu)化片厚、結(jié)、摻雜激活和應(yīng)力工程提高了晶體管驅(qū)動電流,還通過降低有效電容(Ceff)實現(xiàn)了業(yè)界領(lǐng)先的能效。這些優(yōu)化共同帶來了N型和P型納米片晶體管分別約70%和110%的I/CV速度提升。

與FinFET相比,N2納米片晶體管在0.5V至0.6V的低電壓范圍內(nèi)提供了顯著更高的每瓦性能。工藝和器件優(yōu)化使時鐘速度提升約20%,同時在0.5V運行時待機功耗降低約75%。此外,結(jié)合N2 NanoFlex和多種閾值電壓選項(Multi-Vt),進一步增強了高邏輯密度下設(shè)計節(jié)能處理器的靈活性。

在靜態(tài)隨機存取存儲器(SRAM)方面,由于GAA納米片晶體管的閾值電壓波動(Vt-sigma)更小,N2實現(xiàn)了大約38Mb/mm2的2nm SRAM密度,創(chuàng)下新紀錄。相較于基于FinFET的設(shè)計,N2的最低運行電壓(Vmin)對于高電流(HC)宏單元降低了約20mV,而高密度(HD)宏單元降低了30-35mV。這些改進使SRAM在約0.4V的電壓下仍能夠穩(wěn)定地進行讀寫操作,同時保持高良率和可靠性。

導(dǎo)線和電路優(yōu)化:

除了新型晶體管外,N2制程采用全新的中間層(MoL)、后端層(BEOL)和遠后端層(Far-BEOL)導(dǎo)線,電阻降低了20%,性能效率進一步提升。N2的MoL引入了無阻擋層的鎢導(dǎo)線設(shè)計,垂直柵極接觸電阻減少55%,振蕩器頻率提高約6.2%。此外,第一金屬層(M1)采用一次EUV曝光和單次蝕刻工藝(1P1E),減少了復(fù)雜性、掩模數(shù)量,并提高了整體工藝效率。臺積電表示,M1的1P1E工藝將標(biāo)準(zhǔn)單元電容降低了近10%,節(jié)省了多個EUV掩模。

N2還將金屬(My)和通孔(Vy)電阻降低了10%,并為高性能計算(HPC)應(yīng)用提供了超高性能MiM(SHP-MiM)電容器,其電容密度約為200fF/mm2,通過減少瞬態(tài)電壓下降(Voltage Droop),幫助實現(xiàn)更高的最大運行頻率(Fmax)。

3D堆疊支持:

N2技術(shù)還引入了一種全新的銅RDL選項,配備平整鈍化層和貫穿硅通孔(TSV),優(yōu)化用于正面對正面或正面對背面3D堆疊,SoIC鍵合間距為4.5μm,適用于人工智能(AI)、高性能計算(HPC)甚至移動設(shè)備設(shè)計。

投產(chǎn)時間:

臺積電計劃于2025年下半年開始N2制程技術(shù)的量產(chǎn)。

聲明:本網(wǎng)站部分文章轉(zhuǎn)載自網(wǎng)絡(luò),轉(zhuǎn)發(fā)僅為更大范圍傳播。 轉(zhuǎn)載文章版權(quán)歸原作者所有,如有異議,請聯(lián)系我們修改或刪除。聯(lián)系郵箱:viviz@actintl.com.hk, 電話:0755-25988573

審核編輯 黃宇

-

臺積電

+關(guān)注

關(guān)注

44文章

5738瀏覽量

168858 -

2nm

+關(guān)注

關(guān)注

1文章

209瀏覽量

4706

發(fā)布評論請先 登錄

性能殺手锏!臺積電3nm工藝迭代,新一代手機芯片交戰(zhàn)

臺積電2nm制程良率已超60%

手機芯片進入2nm時代,首發(fā)不是蘋果?

英特爾18A與臺積電N2工藝各有千秋

臺積電加大亞利桑那州廠投資,籌備量產(chǎn)3nm/2nm芯片

2025年半導(dǎo)體行業(yè)競爭白熱化:2nm制程工藝成焦點

臺積電2nm工藝將量產(chǎn),蘋果iPhone成首批受益者

臺積電2納米制程技術(shù)細節(jié)公布:性能功耗雙提升

臺積電2nm制成細節(jié)公布:性能提升15%,功耗降低35%

臺積電分享 2nm 工藝深入細節(jié):功耗降低 35% 或性能提升15%!

臺積電分享 2nm 工藝深入細節(jié):功耗降低 35% 或性能提升15%!

評論