每次PCB設計最讓你頭疼的是什么?是密密麻麻的走線?還是讓人抓狂的EMI問題?問題的根源可能藏在你看不見的地方——PCB疊層結構。

當你的設計從實驗室小批量轉到批量生產時,是否遇到過信號完整性突然惡化?當產品工作溫度升高時,PCB是否出現意外故障?這些痛點很可能源自不合理的疊層設計。

當我們面對越來越高速的電路設計,合理的疊層結構已成為項目成敗的關鍵因素之一。

為什么PCB疊層設計如此關鍵?

選擇疊層結構時,需要平衡產品復雜度、信號速率、EMC要求和成本預算四個關鍵因素。以下是它直接影響的三大核心性能。

1、信號完整性

高速信號層需要夾在電源或地平面之間,形成帶狀線結構。例如第3層作為高速信號層時,上下需設置地平面。

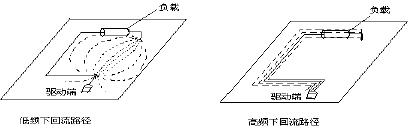

2、電磁兼容性(EMC)

合理的疊層結構能減少60%以上的串擾。多個地平面層能有效減小PCB板阻抗,降低共模EMI。

3、機械穩定性

疊層必須保持對稱,否則熱脹冷縮差異會讓板子變成“曲面屏”,焊接良率直線下降。

不同應用場景的PCB疊層方案選擇

1、雙層板:低成本方案的代價

適用于結構簡單、信號速率低的應用,如家電控制器、LED驅動板。成本優勢明顯,但EMC性能差,信號易受干擾,不適合復雜布線。

設計提示:在空間允許的情況下,盡量增加地線面積,形成局域參考平面。

2、四層板:性價比之選

對于常見的MCU開發板、工業控制板等中等復雜度應用,四層板是最佳選擇。經典結構:TOP(信號)-GND-PWR-BOTTOM(信號)。

優勢在于信號層靠近參考地層,能有效控制阻抗,減少信號回流路徑長度。適合帶差分信號或較高頻率的數字電路設計。

進階技巧:電源層與地層相鄰時,控制層間介質厚度在0.1-0.2mm,可降低電源平面阻抗。

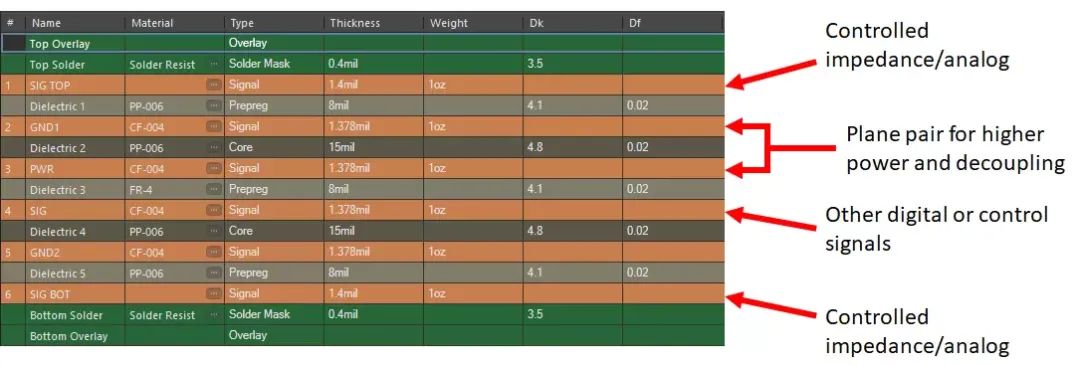

3、六層板:高速信號的避風港

當遇到高速信號較多(如DDR4、PCIe),或板子體積小、布線密度高時,六層板是更優選擇。

推薦結構:TOP-GND-Signal1-PWR-GND-Signal2-BOTTOM。這種架構將高速信號層(Signal1)夾在雙層地平面間,EMI抑制效果最佳。

成本警示:每多一層,成本可能上漲50%,但EMI風險可降低30%。

4、八層及以上:高密度設計的終極方案

適用于高復雜度BGA封裝或超高速系統。典型方案:TOP-GND-Signal1-PWR-GND-Signal2-PWR-BOTTOM,四層信號與四層參考平面。

PCB疊層設計五大黃金法則

1、信號與電源完整性優先

高速信號層:優先布設于內層帶狀線,距參考平面≤4mil

參考平面原則:避免信號跨越平面分割區,否則導致回流路徑斷裂

差分對處理:必須同層布線,長度偏差≤5mil,避免縱向寬邊耦合

2、對稱設計消除應力

銅厚鏡像對稱:如L2/L3層均使用1oz銅箔

介質對稱分布:上下半區介質厚度一致

特殊處理:厚銅層(≥2oz)相鄰層需補償設計——每增加1oz銅厚,兩側各加1張PP

3、材料選型決定性能上限

對于汽車電子等嚴苛環境,選擇Tg≥180℃材料,使PCB在-40℃~150℃溫度循環下的可靠性提升30%+

4、阻抗控制是高速設計的命脈

精度控制:采用UV激光直接成像(LDI)技術,線寬公差±0.2mil

制造補償:1oz銅厚實際按1.2mil計入模型

特殊板材:Rogers與FR4混壓時,對稱位置使用相同熱膨脹系數材料

5、可制造性設計避免翻車

PP片選擇:每層介質不超過3張PP疊層

厚度控制:兩層間PP介質厚度≤21mil(過厚導致加工困難)

銅箔選型:外層優選0.5oz銅箔,內層1oz;電源層按電流需求選擇(2-3oz)

制造工藝中的實戰技巧

1、Foil vs Core疊法

Foil法(外層壓銅箔):成本低,但阻抗控制難(表層流膠問題)

Core法(外層用芯板):成本高20%,但阻抗精度高

2、混合材料壓合

Rogers與FR4混壓時,需采用階梯式壓合工藝,防止層間滑移

3、厚銅板制造

3oz以上銅層采用差分蝕刻工藝——先蝕刻至2oz,二次圖形化至目標厚度

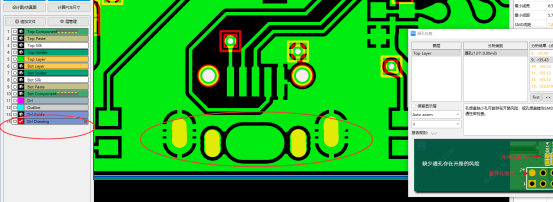

設計完成關鍵步驟:用工具驗證疊層

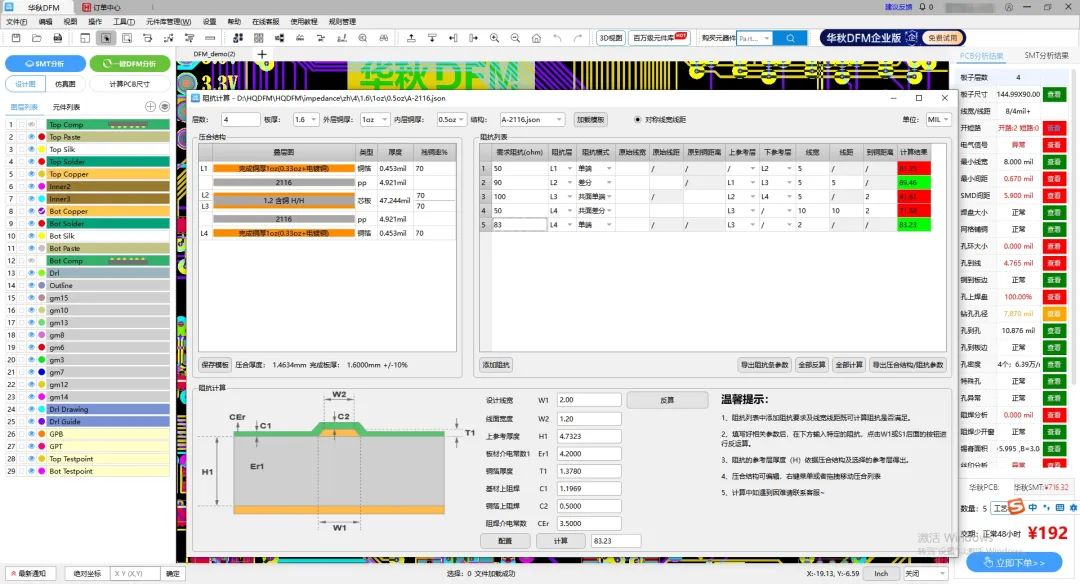

疊層設計完成后,如何驗證?傳統方法依賴工程師經驗,現在華秋DFM軟件提供了一站式解決方案。

1、阻抗神器

結合各種生產因素,自動計算或反算阻抗,確保阻抗公差控制在±10%。

2、一鍵分析

自動檢測設計隱患,排除生產難點和設計缺陷,警示影響價格因素。

3、疊層驗證

軟件能自動匹配符合生產的疊層結構,確保多層PCB板品質可靠。

4、文件對比

輕松比較前后版本疊層差異,避免人為疏忽。

5、設計提示

提前仿真,能發現80%的信號完整性問題。結合華秋DFM的制造分析,可在生產前解決隱患。

打開華秋DFM軟件,上傳設計文件的那一刻,就像給你的PCB疊層做了一次“全身掃描”。相關制造分析的指標在屏幕上跳動,每一項都關系著最終產品的成敗。

軟件不僅告訴你哪里有問題,更給出優化方向——是調整線寬線距,還是修改疊層結構,甚至是更換更經濟的板材。

疊層設計沒有標準答案,但有了專業工具的輔助,新一代硬件工程師們不再需要經歷“打樣-失敗-再打樣”的痛苦循環。

設計完成后,不妨用華秋DFM做一次全面檢查,精準定位隱患位置,獲取合理的優化建議。

華秋DFM軟件最新下載地址(復制到電腦瀏覽器打開):

https://dfm.elecfans.com/dl/software/hqdfm.zip?from=DFMGZH

華秋DFM軟件是國內首款免費PCB可制造性和裝配分析軟件,擁有1200+細項檢查規則。基本可涵蓋所有可能發生的制造性問題,能幫助設計工程師在生產前檢查出可制造性問題,且能夠滿足工程師需要的多種場景,將產品研制的迭代次數降到最低,減少成本。

-

pcb

+關注

關注

4361文章

23452瀏覽量

408000 -

emc

+關注

關注

172文章

4143瀏覽量

186346 -

疊層設計

+關注

關注

0文章

29瀏覽量

6359

發布評論請先 登錄

PCB疊層設計避坑指南

為什么要進行PCB疊層

著火的電路板——大電流PCB設計避坑指南

PCB疊層設計避坑指南

PCB疊層設計避坑指南

評論