對于FPGA而言,時序收斂是一個很重要的概念。在我看來,時序約束是必要的,但不是在最重要的,我們應該在設計初始就考慮到時序問題,而不是完全的靠約束來獲得一個好的結果。

在軍事和航空領域,工程師面臨的挑戰越來越嚴峻,例如延遲要求、帶寬要求、在極端氣溫下使應用達標,以及緊迫的工程進度。在更高的抽象層級上工作,設計會更加清晰簡潔,報錯和糾錯也會更少。但是,這個方法一般會以犧牲性能為代價。要想在 FPGA 設計中實現高性能,需要手動優化 RTL 代碼。而在 C 到 RTL 開發環境中直接生成的RTL代碼,往往是不達標的.

1. FPGA時序的基本概念

FPGA器件的需求取決于系統和上下游(upstream and downstrem)設備。我們的設計需要和其他的devices進行數據的交互,其他的devices可能是FPGA外部的芯片,可能是FPGA內部的硬核。

對于FPGA design來說,必須要關注在指定要求下,它能否正常工作。這個正常工作包括同步時序電路的工作頻率,以及輸入輸出設備的時序要求。在FPGA design內部,都是同步時序電路,各處的延時等都能夠估計出來,但是FPGA內部并不知道外部的設備的時序關系。所以,Timing constraints包括:

輸入路徑(Input paths )

寄存器-寄存器路徑(Register-to-register paths )

輸出路徑(Output paths )

例外(Path specific exceptions )

這正好對應了上圖中三個部分,Path specific exceptions 暫時不提。

Input paths對應的是OFFSET IN約束,即輸入數據和時鐘之間的相位關系。針對不同的數據輸入方式(系統同步和源同步,SDR和DDR)有不同的分析結果。

Register-to-register paths 對應的是整個FPGA design的工作時鐘。如果只有一個時鐘,那么只需要指定輸入的頻率即可。如果有多個時鐘,這些時鐘是通過DCM,MMCM,PLL生成的,那么顯然ISE知道這些時鐘之間的頻率、相位關系,所以也不需要我們指定。如果這些不同的時鐘是通過不同的引腳輸入的,ISE不知道其相位關系,所以指定其中一個為主時鐘,需要指定其間的相位關系。

Output paths對應的是OFFSET OUT 約束,和OFFSET IN約束很類似,不過方向相反。

2.找到合適的 FPGA 工具設置

盡管工程師們很清楚已有 FPGA 工具的參數設置,但是很多時候并沒有完全把這些設置的功能發揮出來。一般而言,這些設置只有在設計無法達到時序要求的時候才會用到。而且,對于已經達到性能目標的設計來說,如果好好利用這些設置,性能再提升10%-50%也是完全有可能的。難點在于,各種 FPGA 工具一般會有30-70個綜合和布局布線的設置選項,從這些選項中選擇合適的那一組設置組合如同大海撈針。幸好,目前已經有些工具可以控制并運行設計探索,而且整套流程是自動化的,也十分嚴謹。

最后的一個難題,是計算資源的匱乏。傳統的嵌入式應用都是在單一電腦上設計的,但是運行多個編譯需要更多的計算能力,這樣就會犧牲更多的時間。如果可以并行運行編譯的話,那么周轉時間就會短很多。

3.優化高層次設計

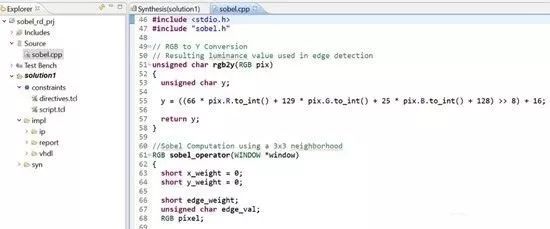

市面上已經有工具可以將設計性能提升50%并且不改變 RTL 代碼了。如下圖所展示的是設計探索非常好的一個例子:在視頻處理的設計中,進行 Sobel Filter Implementation。該設計的目標器件為一個 FPGA 搭載雙核 Arm? Cortex?-A9 MPCore?。

該設計的時鐘周期為5.00ns或者200MHz。根據時序預估,它的時序還差506ps,也就是據目標速率還差10%或181MHz,如下圖

Intime在不改變 C++代碼的情況下,工程師把設計輸出為 RTL 代碼。通過使用一種探索工具,工程師打開項目(xpr),然后并行運行不同 FPGA 工具參數的編譯來優化設計。

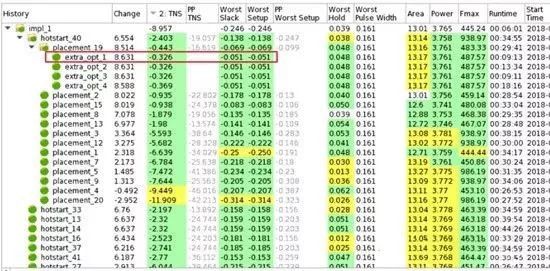

在兩輪優化,15次編譯之后,該設計達到了性能目標,200MHz,而且沒有修改源代碼。如下圖:

這個案例并不是說這種優化只能在高層次設計中進行。其實,只要是RTL代碼都有可能提升性能。

4.RTL 項目的設計探索

軟件無線電 (SDR) 是另一個可以從時序收斂工具中獲益的應用。在這個案例中,參考設計直接用 RTL 代碼創建。這是一個高性能,高集成度的射頻 (RF) 捷變收發器 (Agile Transceiver),為3G和4G基站的應用而設計。該設備把一個擁有靈活混合信號基帶單元的射頻前端 (RF Front End),和集成頻率合成器 (integrated frequency synthesizers)相結合,再把處理器加上一個可配置的數字界面。

開始的時鐘周期是4ns 或250MHz,并且參考設計默認時序達標。為了讓這個設計時序失敗,工程師把時鐘周期設置成激進的2ns,新的目標速率為500MHz。在這種情況下,設計時序離達標就會差246ps,并以445MHz 運行。

在同樣的情況下,不改變RTL,該設計可以通過探索多種 FPGA 工具參數來優化。優化過程為三輪,60次編譯。

結果顯示,最終 WNS 從-246ps 提升到-0.051ps,提升了79.2%,相當于時鐘周期為487MHz 以及9.4%的最大頻率提升。如下圖:

5.讓性能更進一步

隨著科學技術的發展,電子器件會變得越來越復雜,要求也越來越高,這是大勢所趨。新的 FPGA 軟件科技和方法會幫助我們提升質量、效率,滿足我們的需求。盡管 FPGA 設計的潛能尚未完全被了解,但工具參數的探索可以減少高層次設計的性能犧牲,從而保證項目完成地又快又好。工程師們會在使用工具探索 FPGA 設計參數選項上,越來越熟練。這些工具也會在設計中大放異彩。

有需要試用intime軟件者,請加群提交申請即可。

-

FPGA

+關注

關注

1643文章

21957瀏覽量

614026 -

芯片

+關注

關注

459文章

52162瀏覽量

436081 -

寄存器

+關注

關注

31文章

5421瀏覽量

123315

原文標題:Intime在軍事航空項目中大放異彩

文章出處:【微信號:gh_873435264fd4,微信公眾號:FPGA技術聯盟】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

FPGA高級班前言基本原理基本概念

時序分析基本概念介紹——時序庫Lib,除了這些你還想知道什么?

時序分析和時序約束的基本概念詳細說明

時序設計基本概念之collection

FPGA設計中時序分析的基本概念

介紹時序分析基本概念MMMC

時序分析基本概念介紹—Timing Arc

FPGA時序的基本概念,RTL項目的設計探索

FPGA時序的基本概念,RTL項目的設計探索

評論